Method for protecting silicon oxide layer in low-voltage field by CMOS high-voltage process

A technology of silicon oxide layer and low-voltage area, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of affecting the thickness of the field silicon oxide layer, loss of insulation isolation, etc., and achieve the effect of low cost and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Now in conjunction with accompanying drawing, the specific embodiment of the present invention is described in further detail:

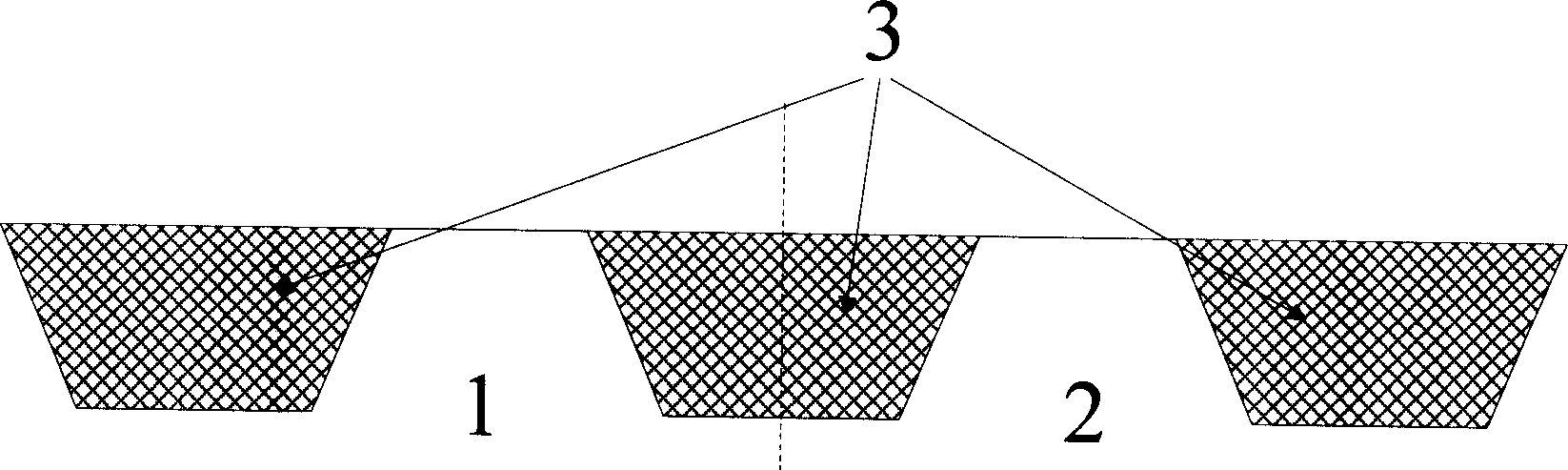

[0032] First, if figure 1 as shown ( figure 1 is a schematic diagram of the formation of field silicon oxide), and the required field silicon oxide layer is formed on the silicon substrate. The process of forming the field silicon oxide layer can be a LOCOS (local oxidation) process or an STI (shallow trench isolation) process. .

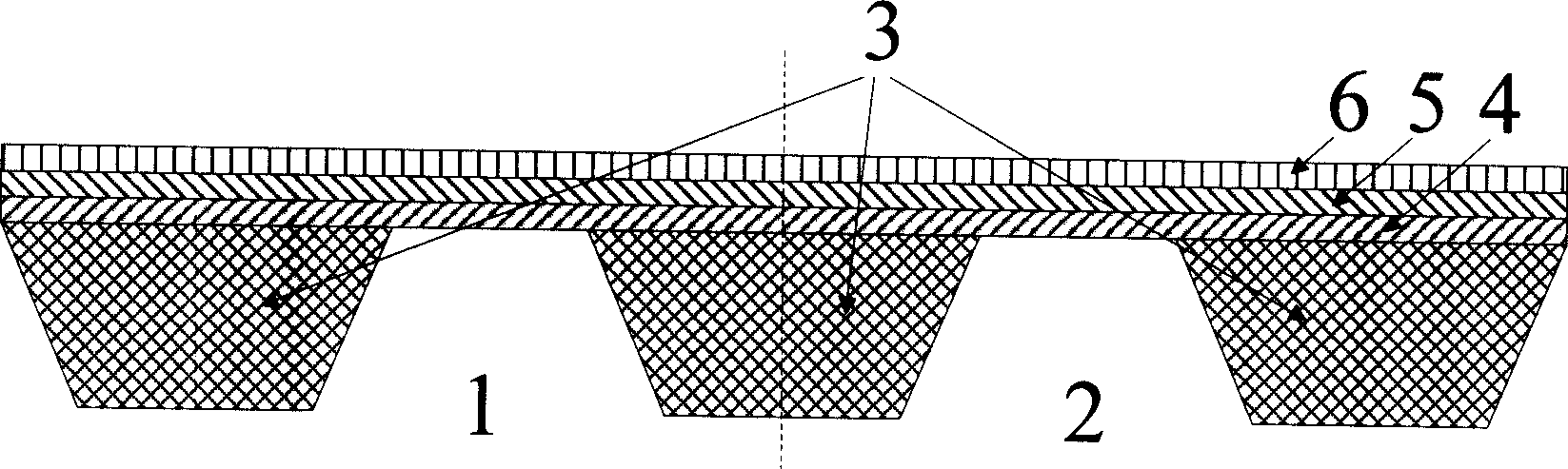

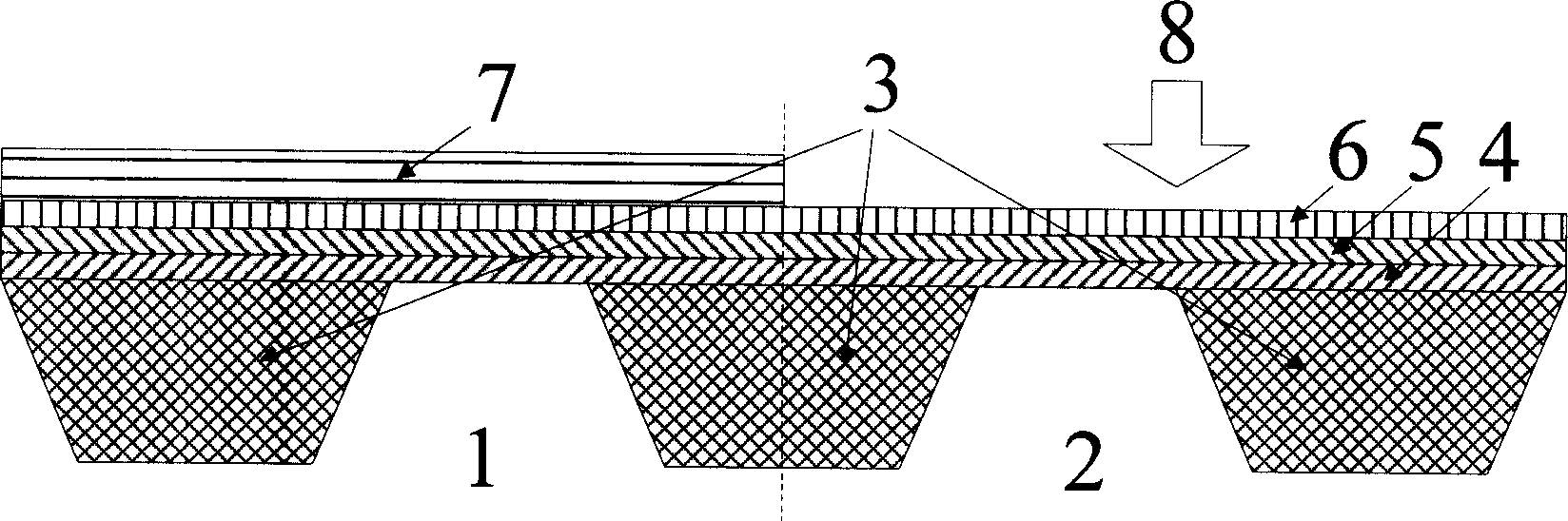

[0033] Secondly, if figure 2 as shown ( figure 2 It is a schematic diagram of growing a bottom silicon oxide layer, a silicon nitride layer and a top silicon oxide layer as a shielding layer), using a thermal oxidation method to grow a bottom silicon oxide layer on the substrate silicon and a field silicon oxide layer, and using chemical vapor deposition (CVD) A silicon nitride layer is grown on the silicon oxide layer, and a top silicon oxide layer (HTO) is grown on the silicon nitride layer using chemical va...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com