Semiconductor device with low thermal expansion coefficient and use thereof

A thermal expansion coefficient, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., to achieve the effect of reducing structural distortion or deformation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to further illustrate the technical means and effects adopted by the present invention to achieve the predetermined purpose of the invention, the following describes the specific implementation and structure of the semiconductor element with a low thermal expansion coefficient substrate according to the present invention with reference to the accompanying drawings and preferred embodiments. , features and their effects are described in detail below.

[0047] For clarity of illustration, elements in the figures are not drawn to scale. In different figures, the reference numerals of elements may be repeated to designate corresponding or similar elements.

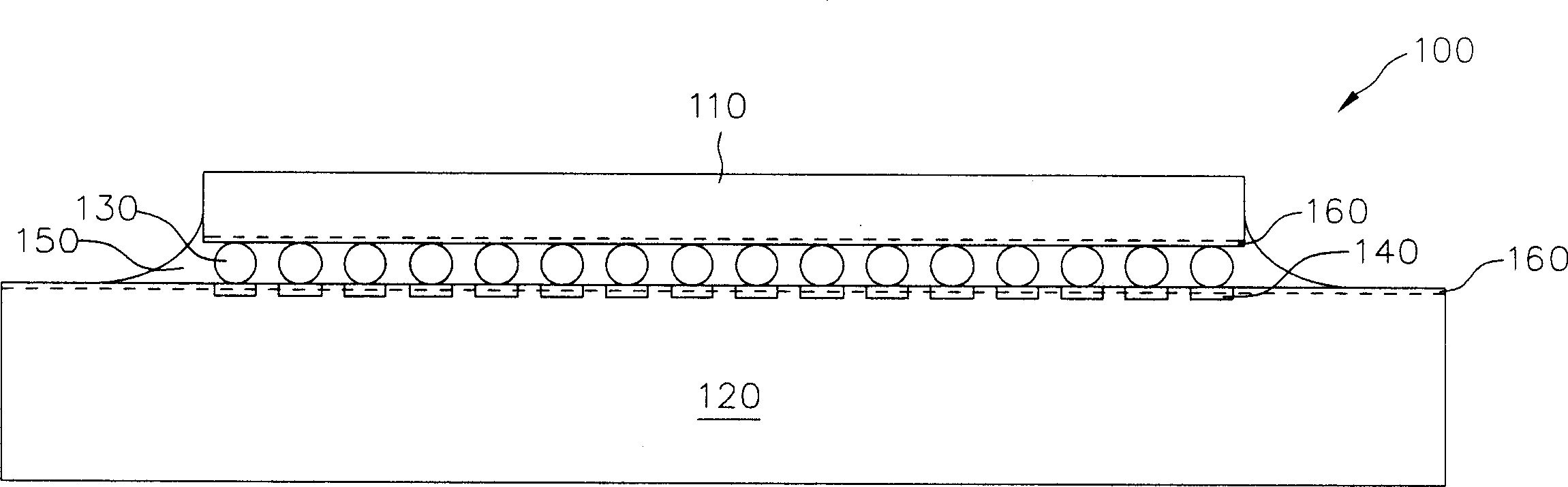

[0048] see figure 1 As shown, it is a schematic structural diagram of a semiconductor package device 100 according to a preferred embodiment of the present invention. Specifically, the semiconductor package device 100 includes an integrated circuit chip 110, wherein the integrated circuit chip 110 includes a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com