Method for forming secondary partition sheet used for strain silicon MOS transistor and structure thereof

一种隔片、栅极结构的技术,应用在晶体管、电固体器件、半导体器件等方向,能够解决困难、难制造、复杂制造工艺和结构等问题,达到增大空穴迁移率、改进工艺集成、高器件产率的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

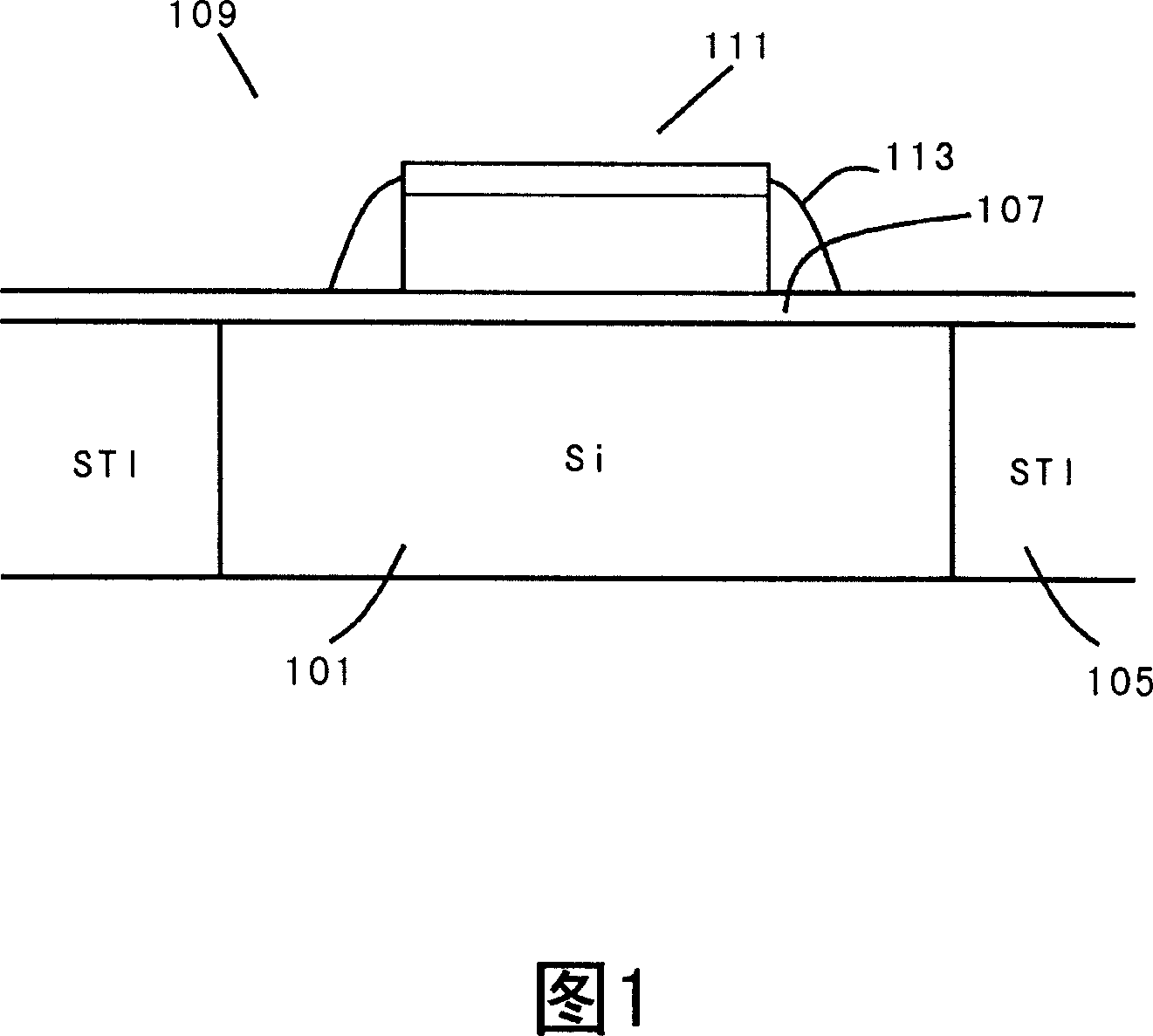

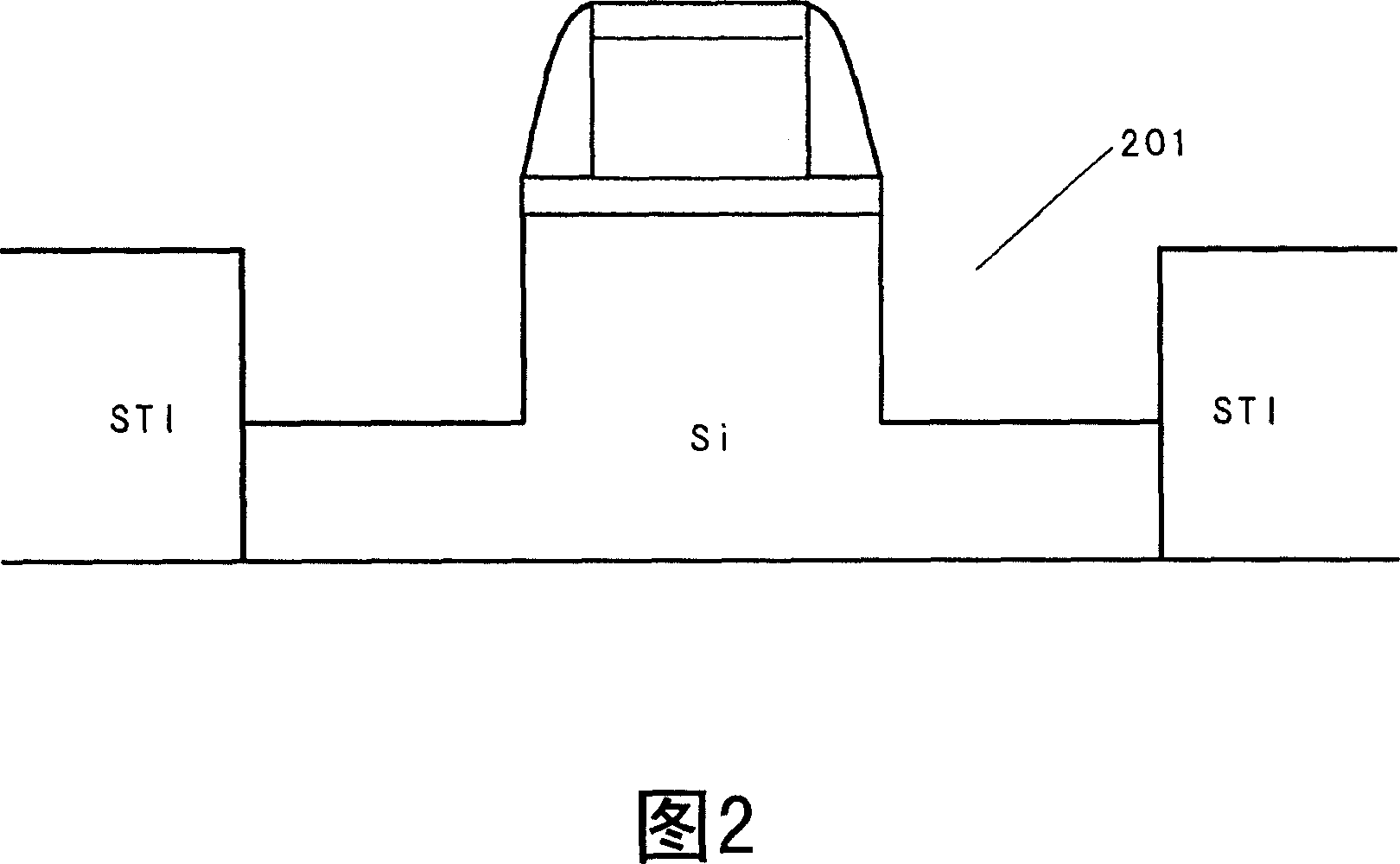

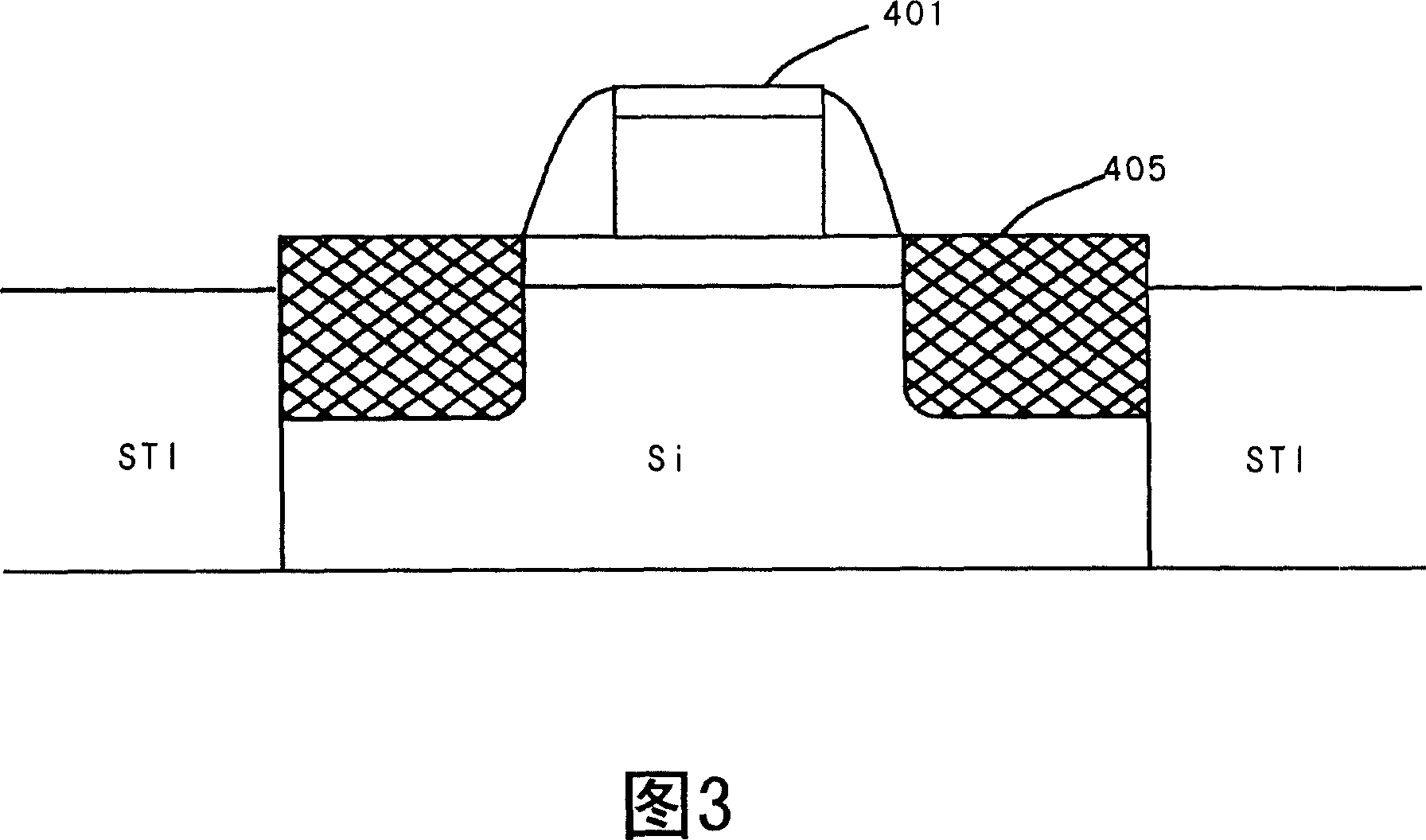

[0014] According to the present invention, there is provided a technique for processing integrated circuits for semiconductor device fabrication. More specifically, the present invention provides methods and structures for fabricating MOS devices using strained silicon structures for CMOS advanced integrated circuit devices. However, it should be realized that the present invention has broader applicability.

[0015] A method for manufacturing a CMOS integrated circuit device according to one embodiment of the present invention can be summarized as follows:

[0016] 1. Provide semiconductor substrates such as silicon wafers, silicon-on-insulator;

[0017] 2. Forming a dielectric layer (eg, gate oxide or nitride) overlying the semiconductor substrate;

[0018] 3. Forming a gate layer (eg, polysilicon, metal) overlying the dielectric layer;

[0019] 4. patterning the gate layer to form a gate structure comprising a plurality of edges (eg, a plurality of sides or edges);

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More