Self-aligned silicone process for low resistivity contacts to thin film silicon-on-insulator mosfets

a technology of silicon-on-insulator mosfets and self-aligning silicone, which is applied in the direction of semiconductors, electrical equipment, semiconductor devices, etc., can solve the problems of low parasitic resistance, low source/drain series resistance, and loss of silicide layer efficiency in reducing series resistan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

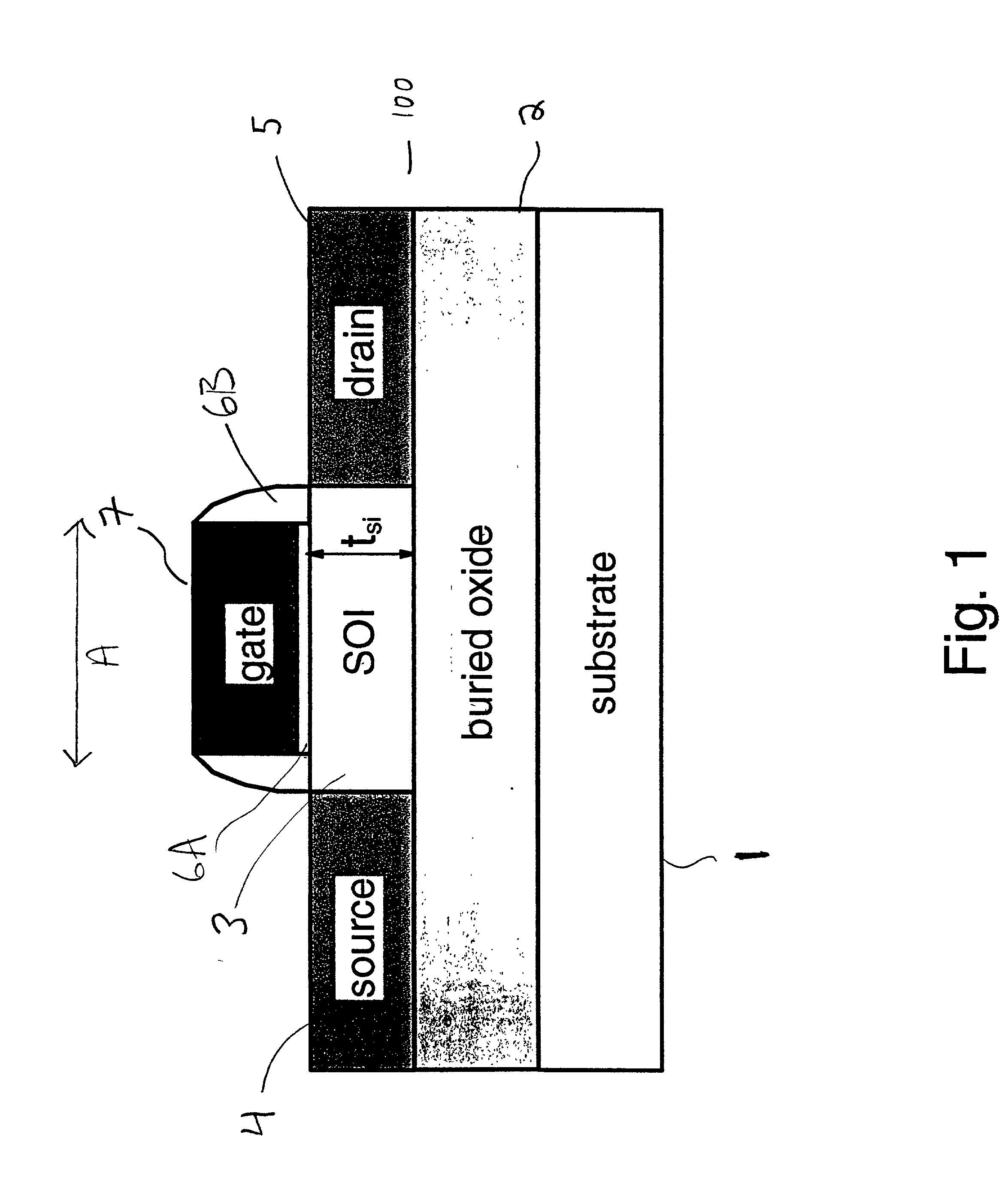

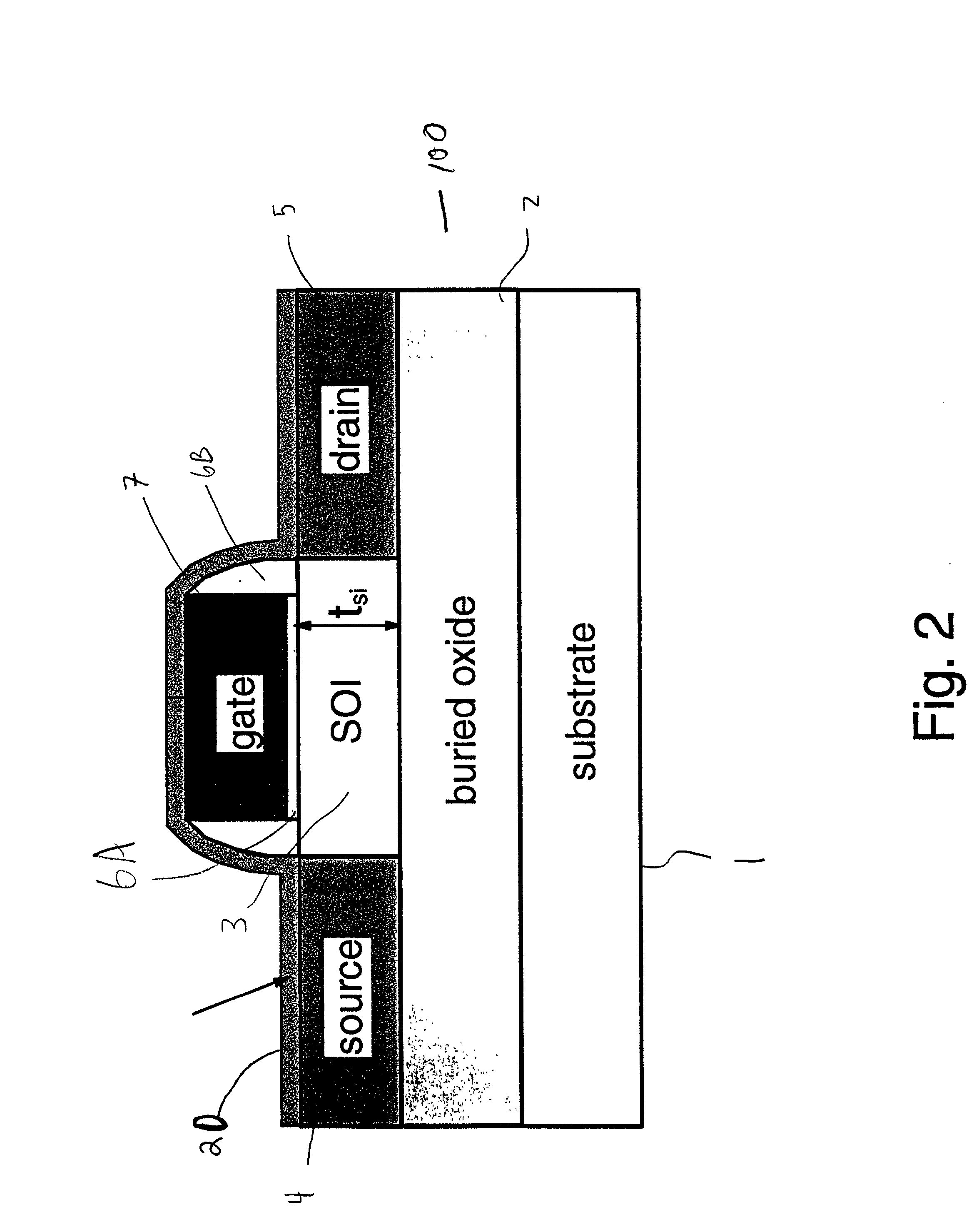

[0029] Referring now to the drawings, and more particularly to FIGS. 1-6, there is shown a preferred embodiment of the method of making of a self-aligned silicide which is applicable to the standard MOSFET structure, and also to non-conventional MOSFETs and structures according to the present invention.

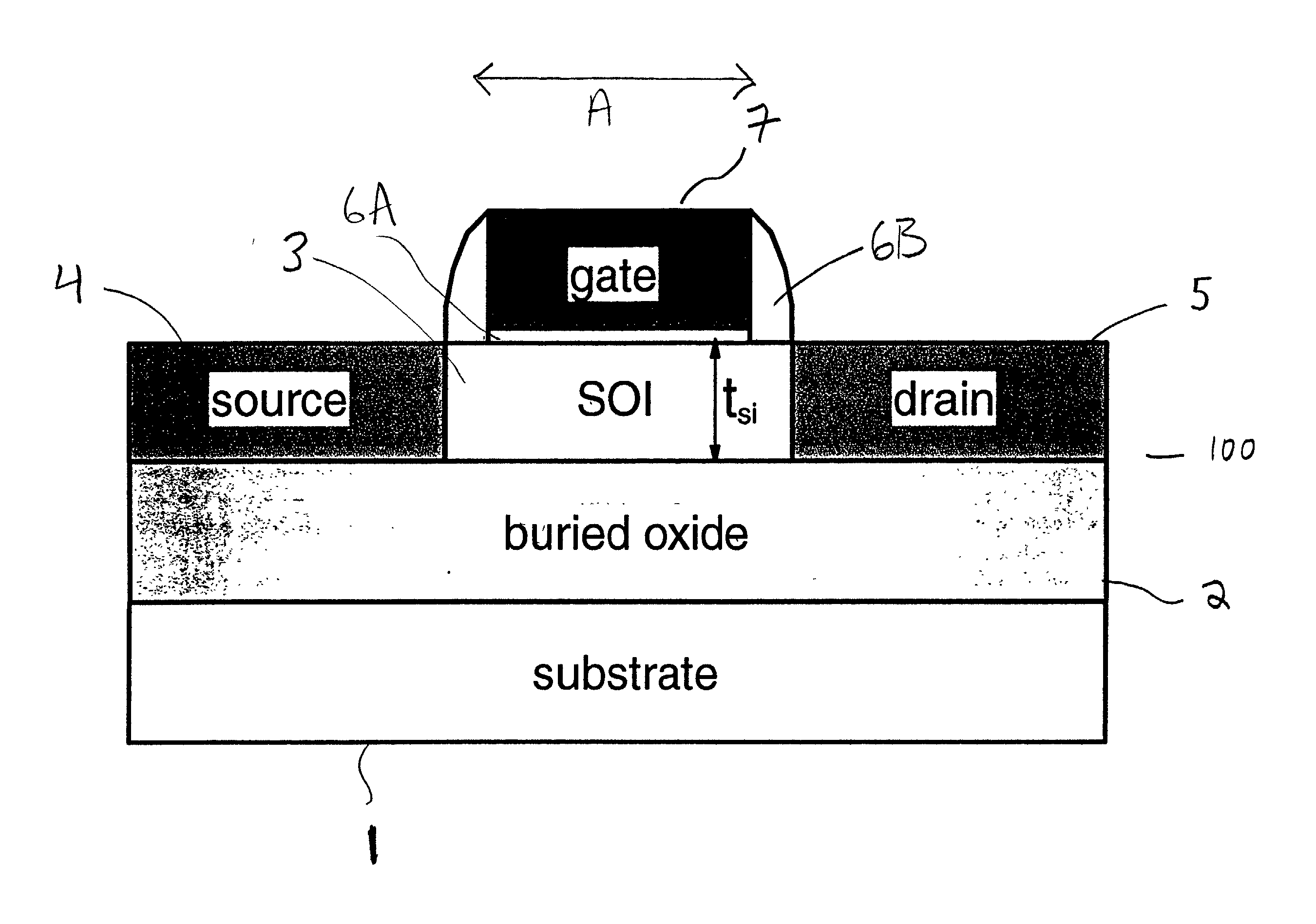

[0030] Referring now to FIG. 1, a conventional MOSFET structure 100 is shown having a substrate 1 formed of silicon, a buried oxide layer 2 (e.g., silicon oxide layer), an SOI layer 3 which thickness noted by t.sub.si, a gate dielectric 6A (e.g., SiO.sub.2), sidewall spacers 6B formed of nitride or oxide, a gate 7 (e.g. doped poly-Si, or metal), and a source 4 and a drain 5 maid into the SOI film 3, typically by an implant.

[0031] The inventive method is directed to making a self-aligned silicide which is applicable to the standard MOSFET structure, and also to non-conventional MOSFETs and structures. For ease of discussion, the present invention will be applied to the conventional MOS...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More