Patents

Literature

30 results about "Thin film soi" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

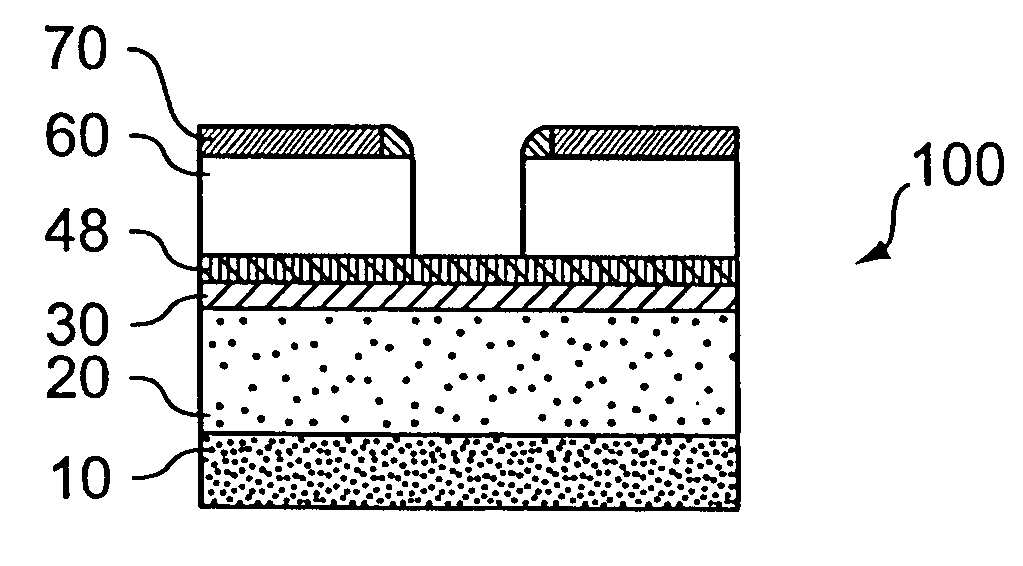

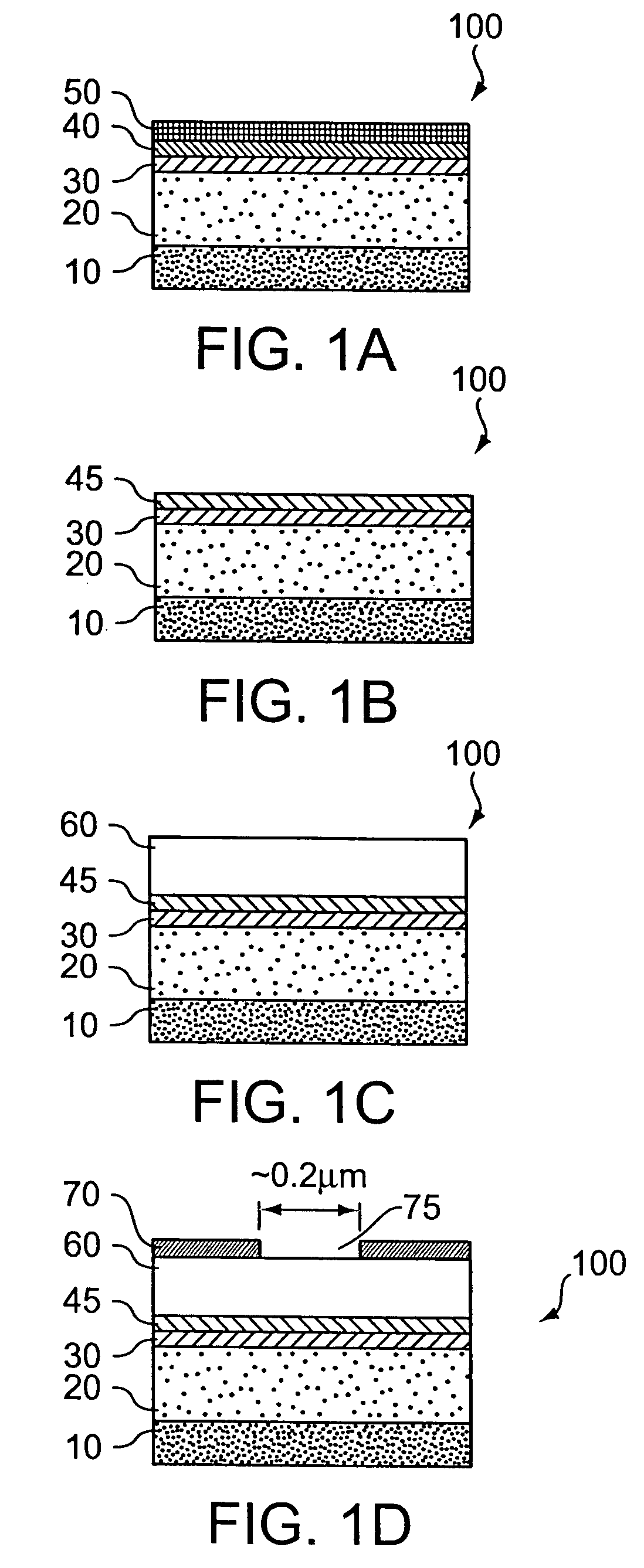

Image sensor using thin-film SOI

InactiveUS20080070340A1Faster throughputImage degradationSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalThin film soi

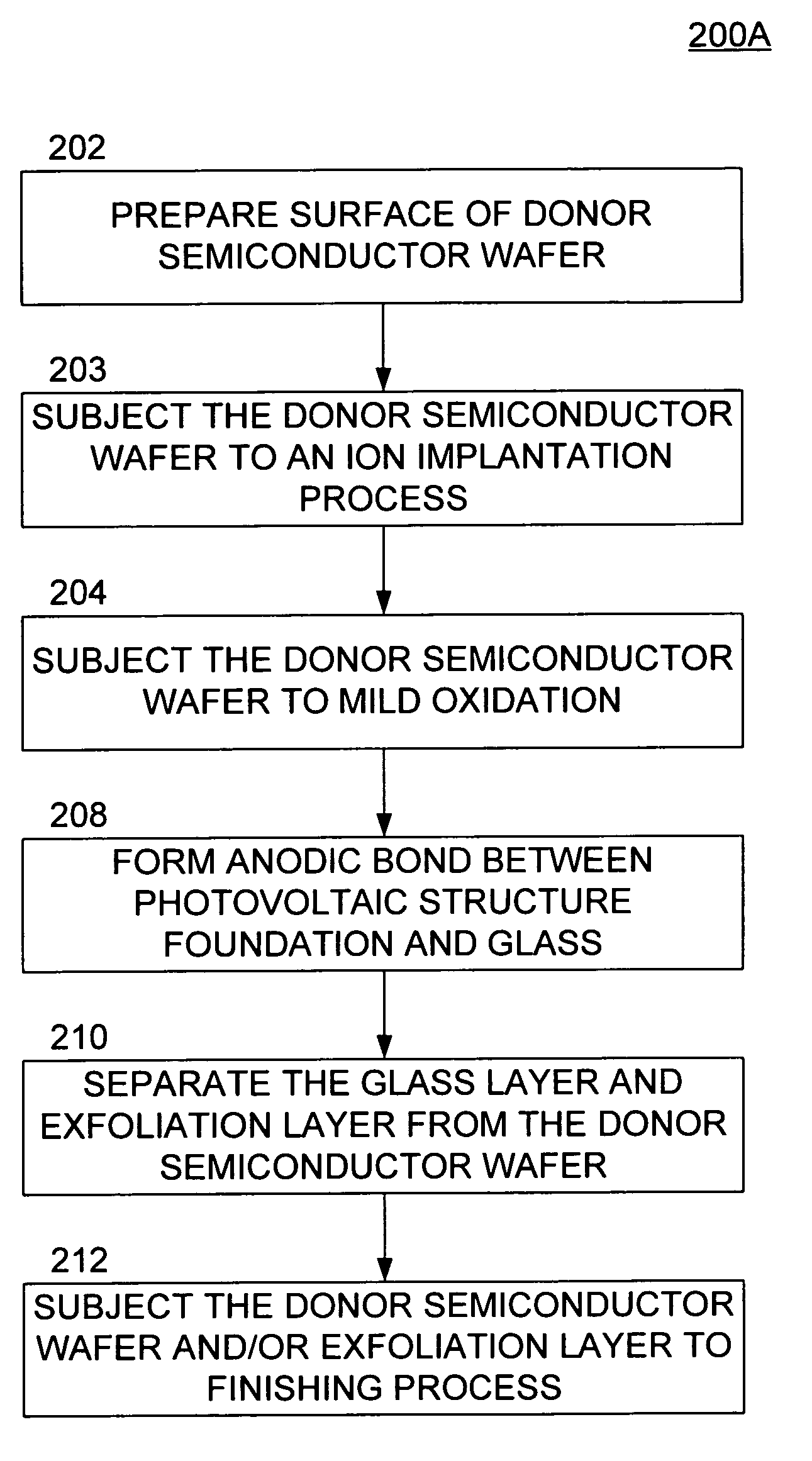

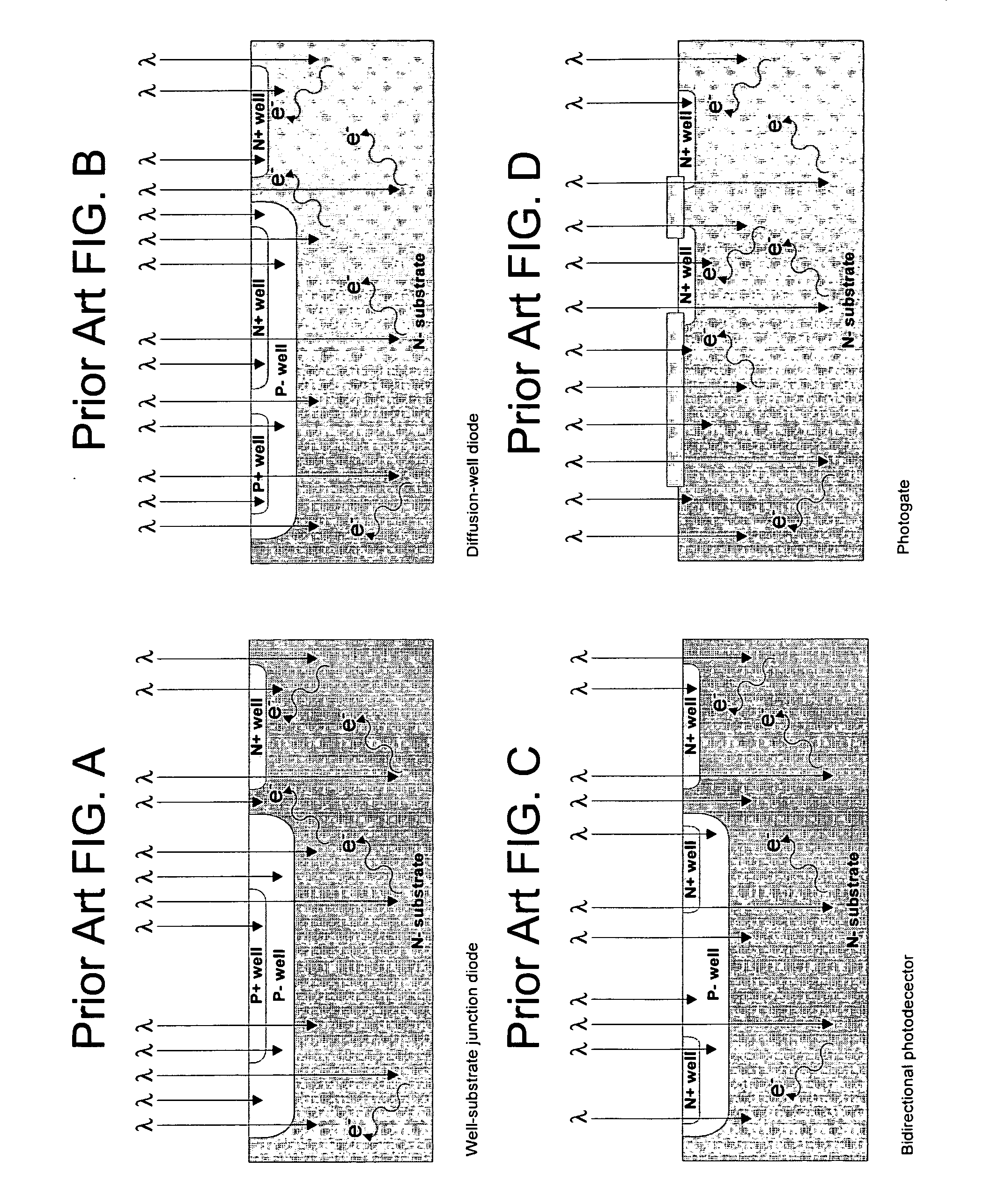

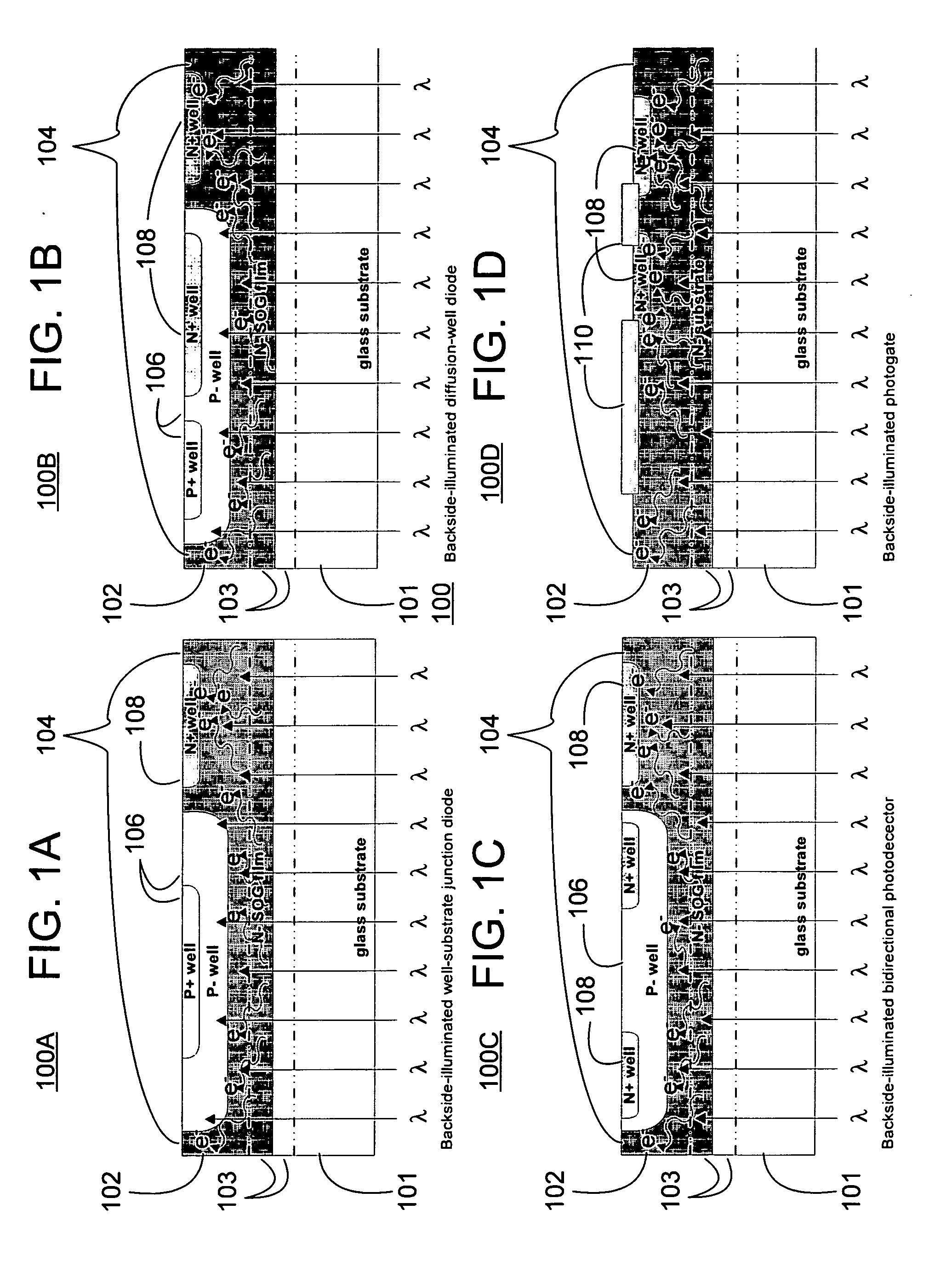

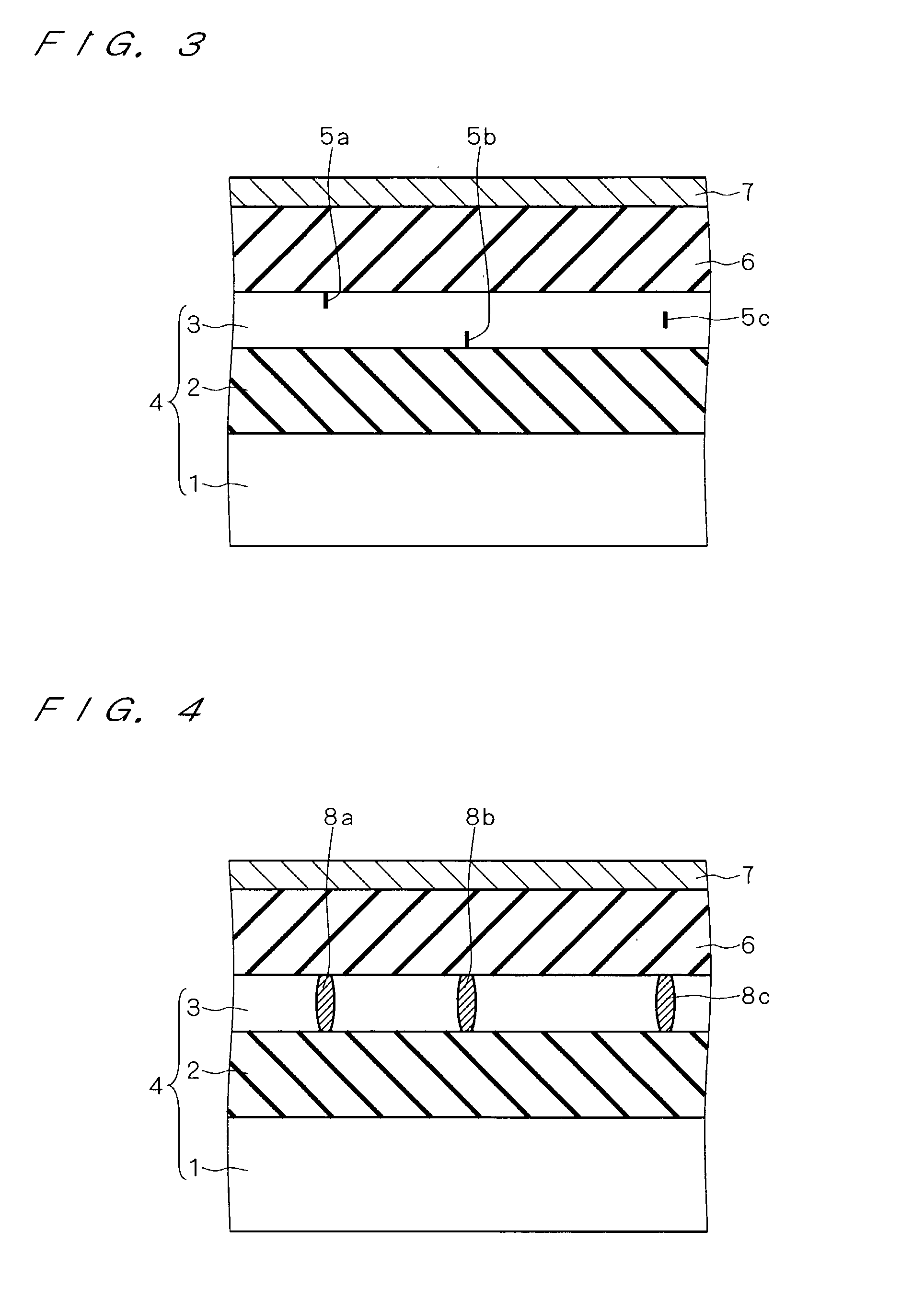

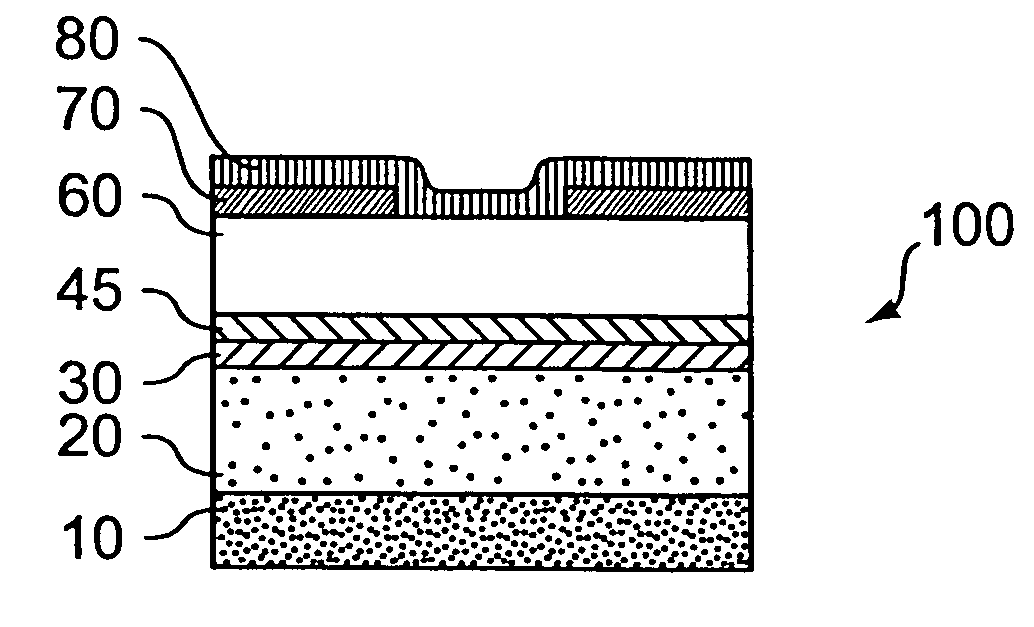

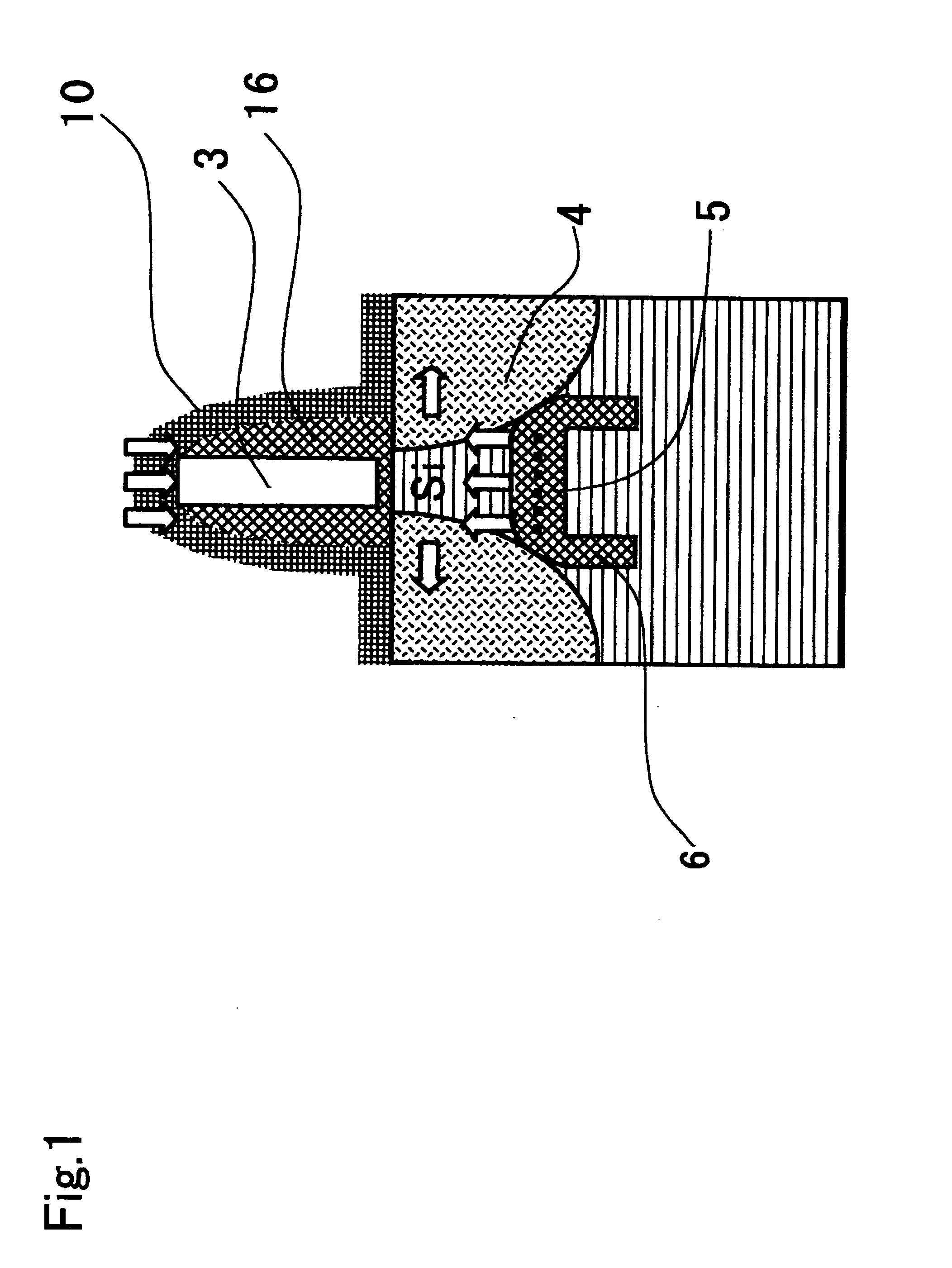

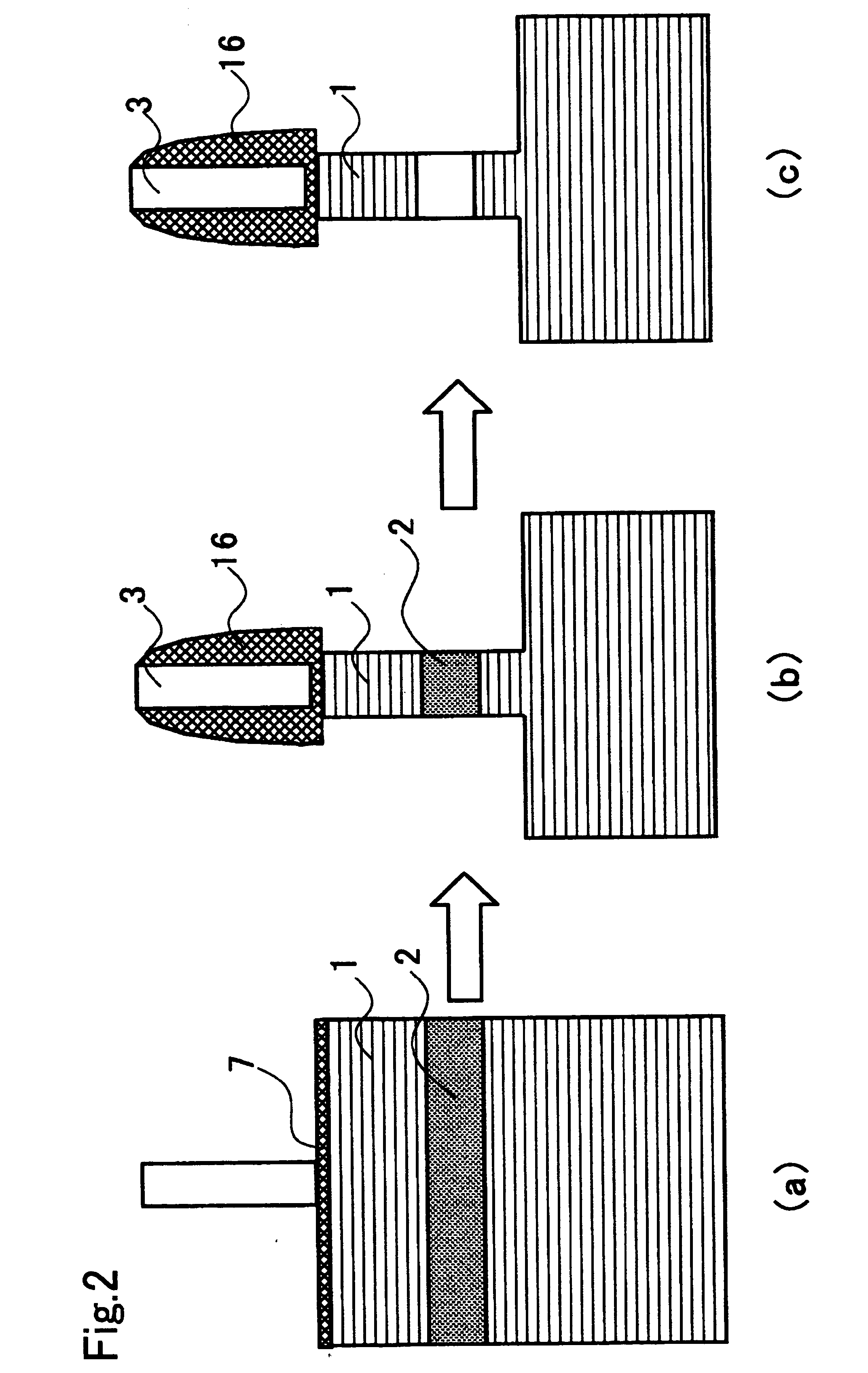

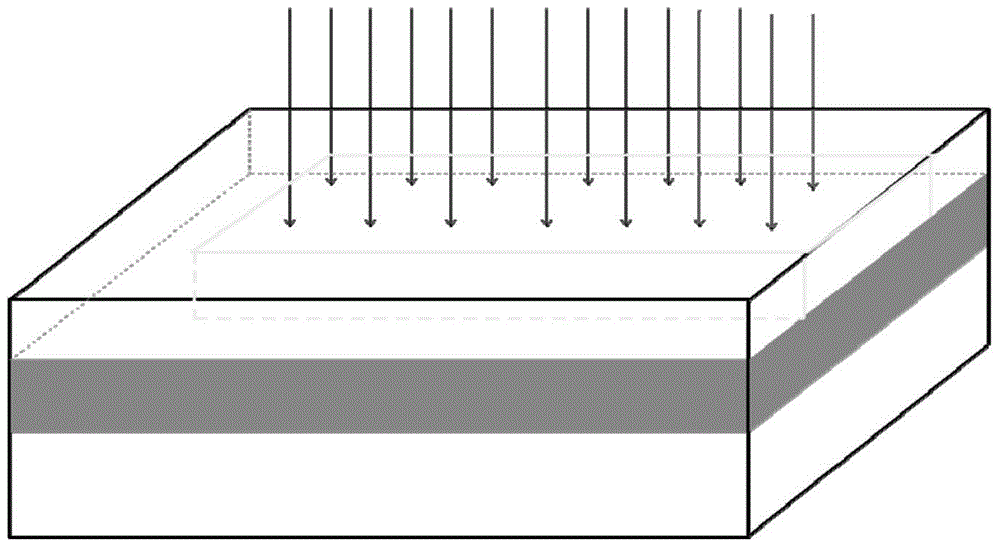

Systems and methods related to an image sensor of one or more embodiments include subjecting a donor semiconductor wafer to an ion implantation process to create an exfoliation layer of semiconductor film on the donor semiconductor wafer, forming an anodic bond between the exfoliation layer and an insulator substrate by means of electrolysis; separating the exfoliation layer from the donor semiconductor wafer to transfer the exfoliation layer to the insulator substrate; and creating a plurality of image sensor features proximate to the exfoliation layer. Forming the anodic bonding by electrolysis may include the application of heat, pressure and voltage to the insulator structure and the exfoliation layer attached to the donor semiconductor wafer. Image sensor devices include an insulator structure, a semiconductor film, an anodic bond between them, and a plurality of image sensor features. The semiconductor film preferably comprises an exfoliation layer of a substantially single-crystal donor semiconductor wafer.

Owner:CORNING INC

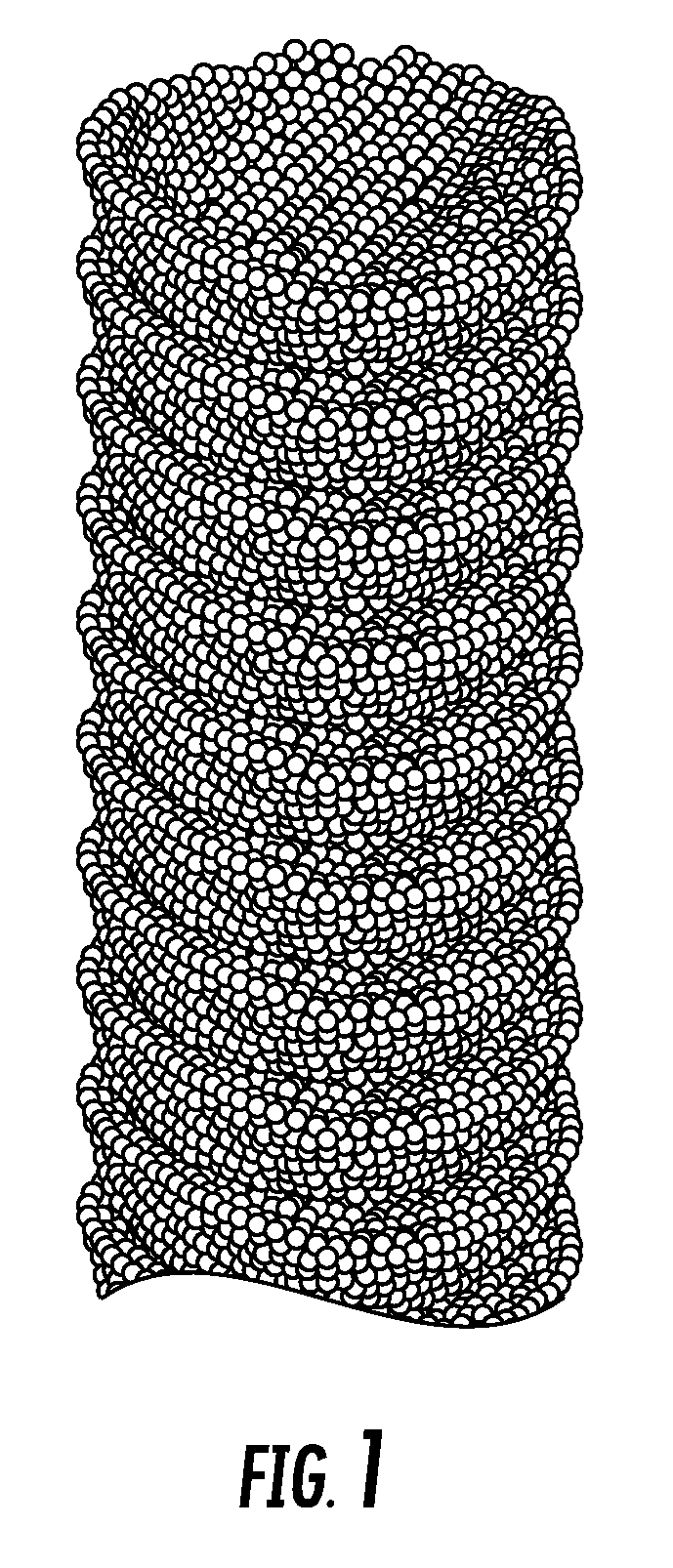

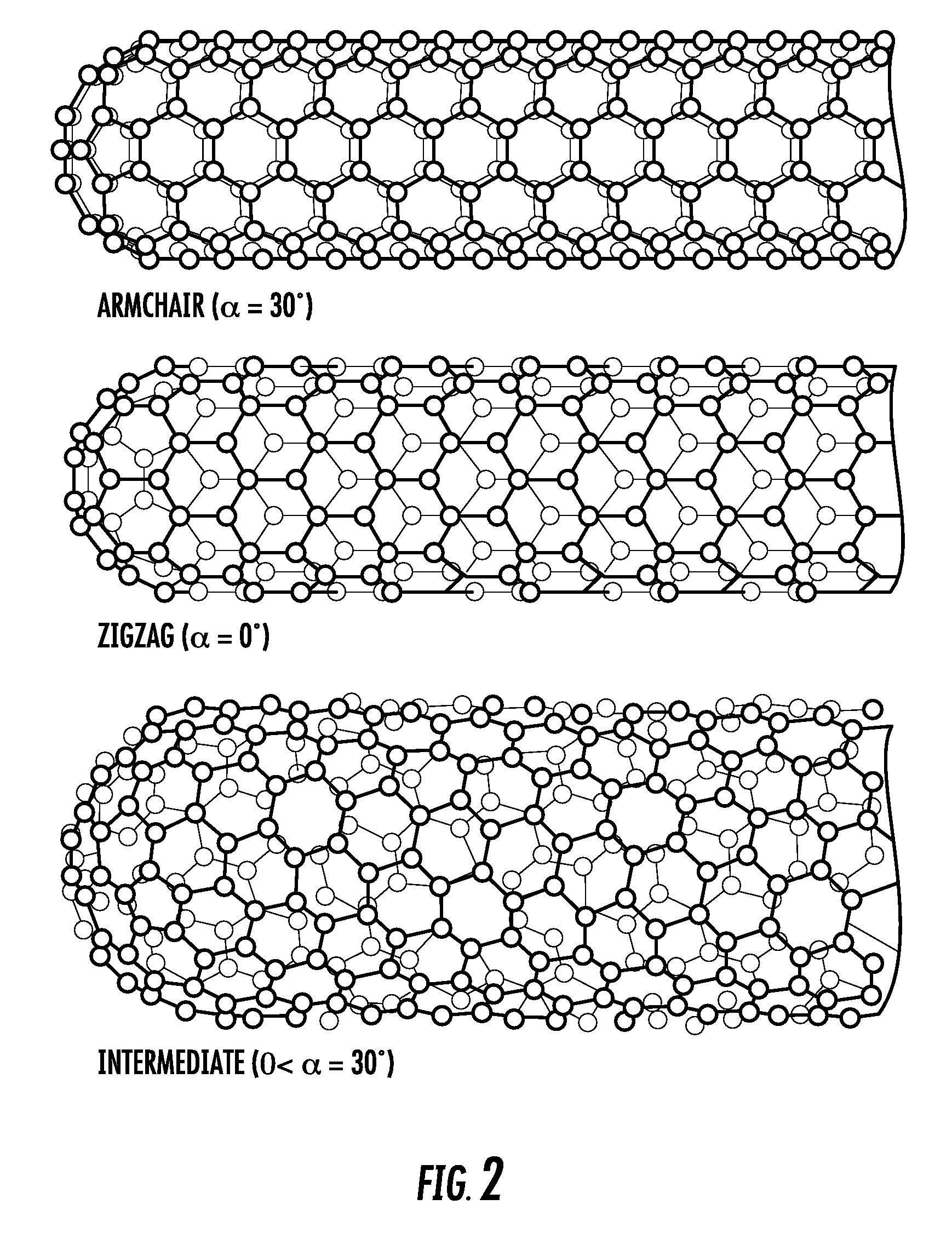

Low density lightning strike protection for use in airplanes

ActiveUS20090227162A1Minimize micro-crackingWeight optimizationConductive materialWarp knittingFiberEpoxy

Surface films, paints, or primers can be used in preparing aircraft structural composites that may be exposed to lightning strikes. Methods for making and using these films, paints or primers are also disclosed. The surface film can include a thermoset resin or polymer, e.g., an epoxy resin and / or a thermoplastic polymer, which can be cured, bonded, or painted on the composite structure. Low-density electrically conductive materials are disclosed, such as carbon nanofiber, copper powder, metal coated microspheres, metal-coated carbon nanotubes, single wall carbon nanotubes, graphite nanoplatelets and the like, that can be uniformly dispersed throughout or on the film. Low density conductive materials can include metal screens, optionally in combination with carbon nanofibers.

Owner:ROHR INC +1

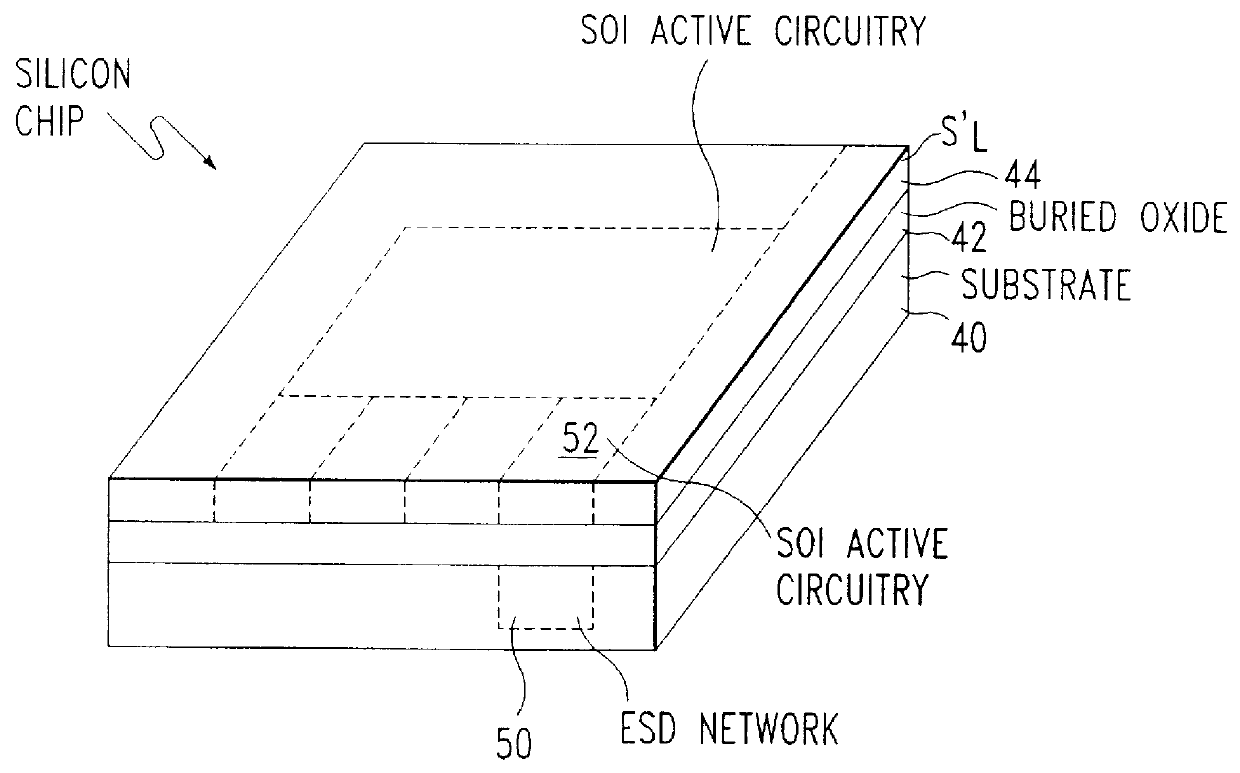

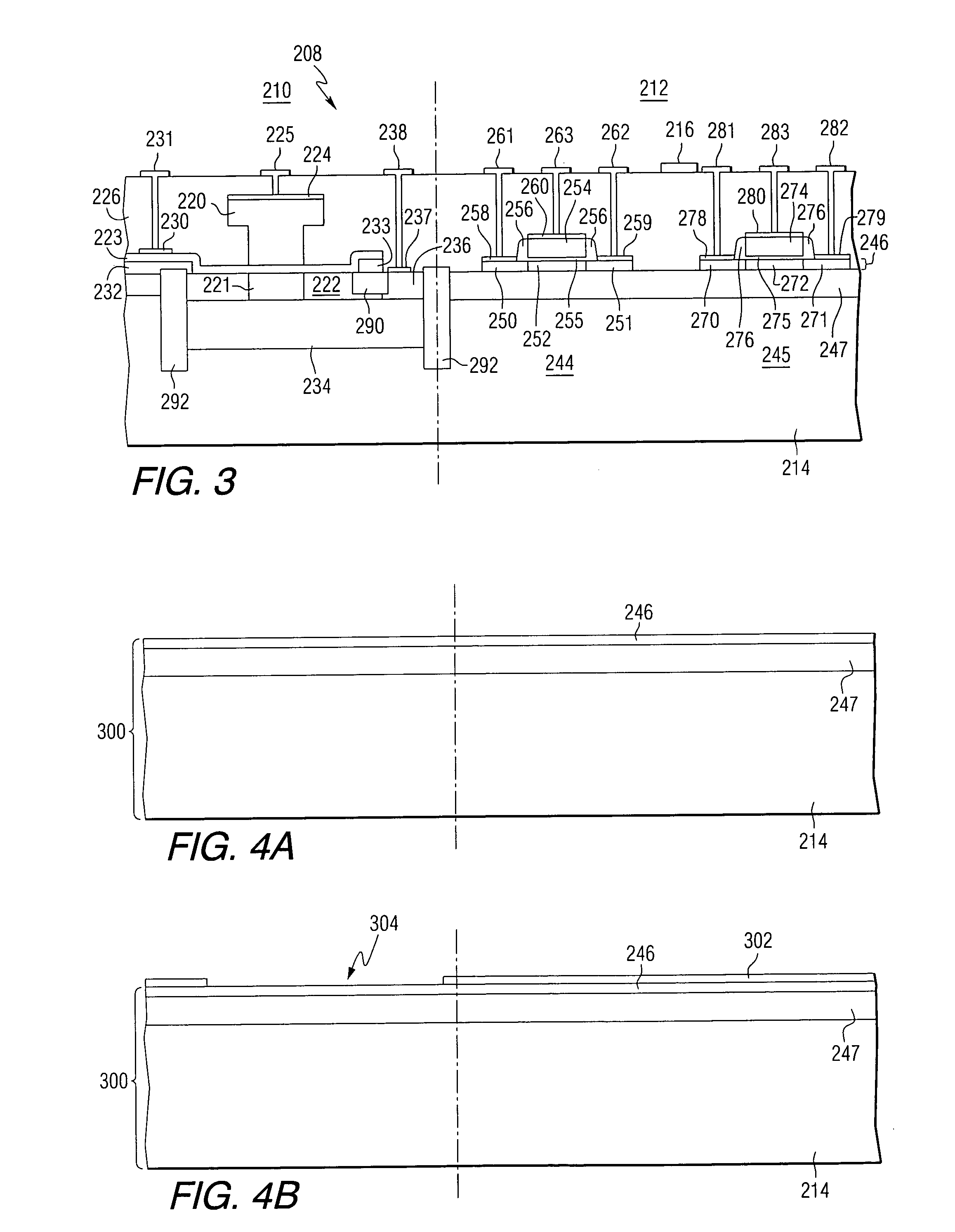

3-D CMOS-on-SOI ESD structure and method

Owner:IBM CORP

Photonic Devices Monolithically Integrated with Cmos

ActiveUS20080001139A1Improves intrinsic and extrinsic efficiencySolid-state devicesDiodeCMOSPhotonics

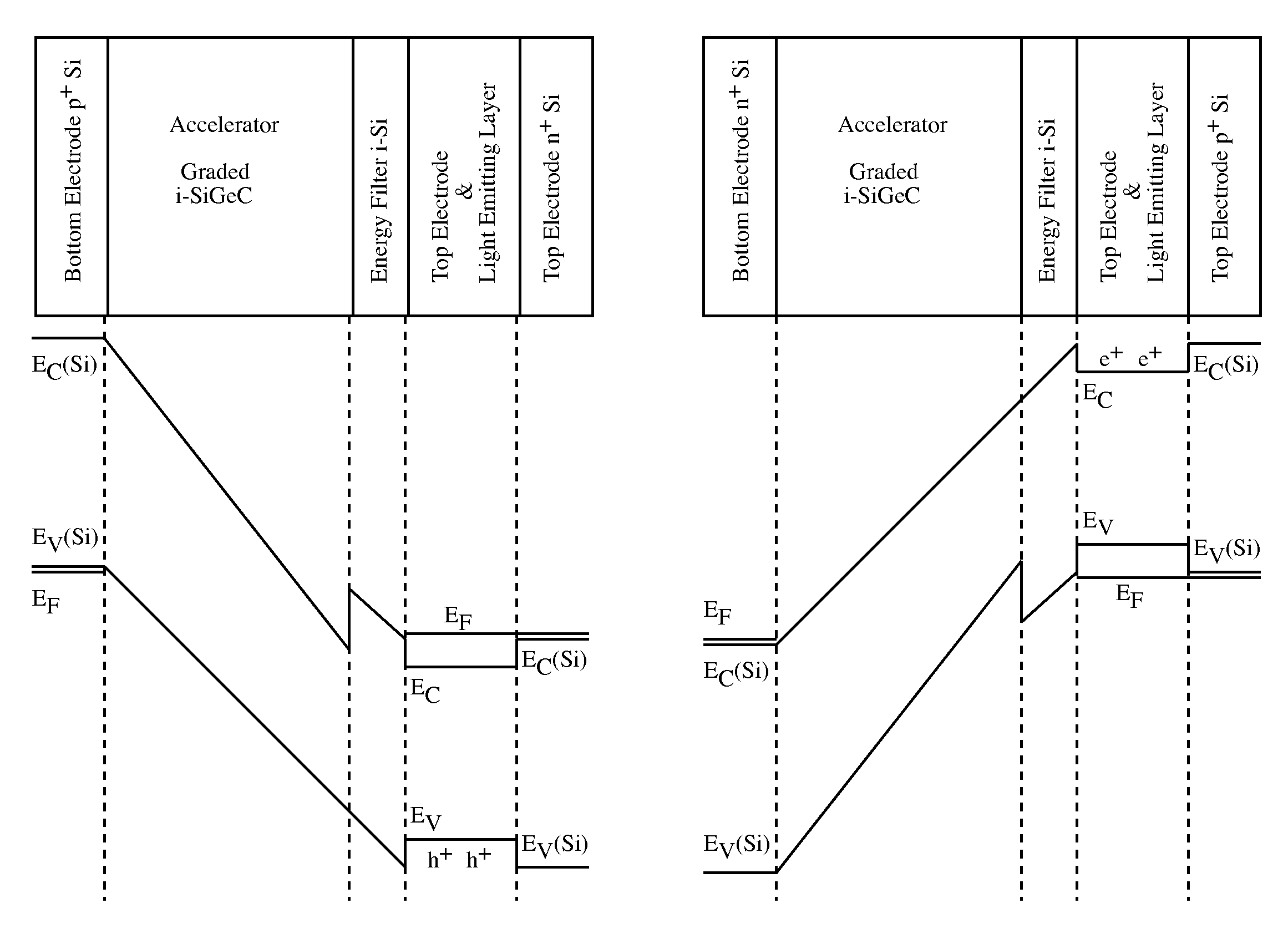

Photonic devices monolithically integrated with CMOS are disclosed, including sub-100nm CMOS, with active layers comprising acceleration regions, light emission and absorption layers, and optional energy filtering regions. Light emission or absorption is controlled by an applied voltage to deposited films on a pre-defined CMOS active area of a substrate, such as bulk Si, bulk Ge, Thick-Film SOI, Thin-Film SOI, Thin-Film GOI.

Owner:QUANTUM SEMICON

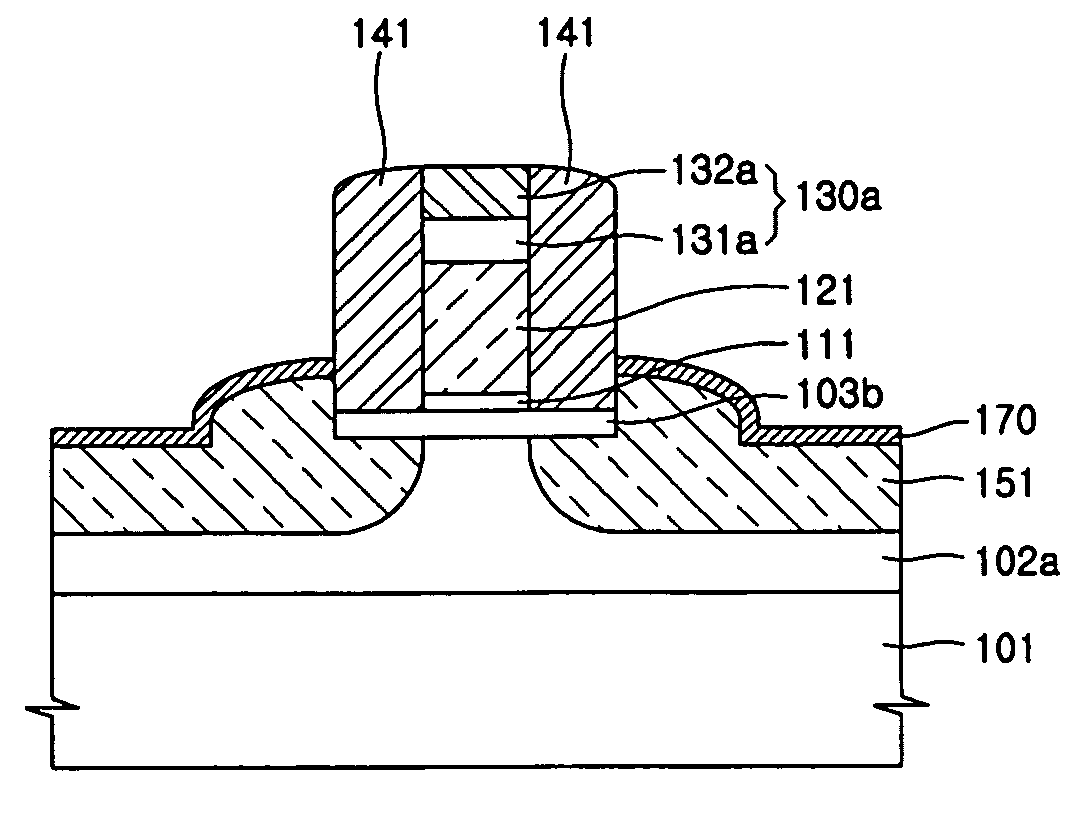

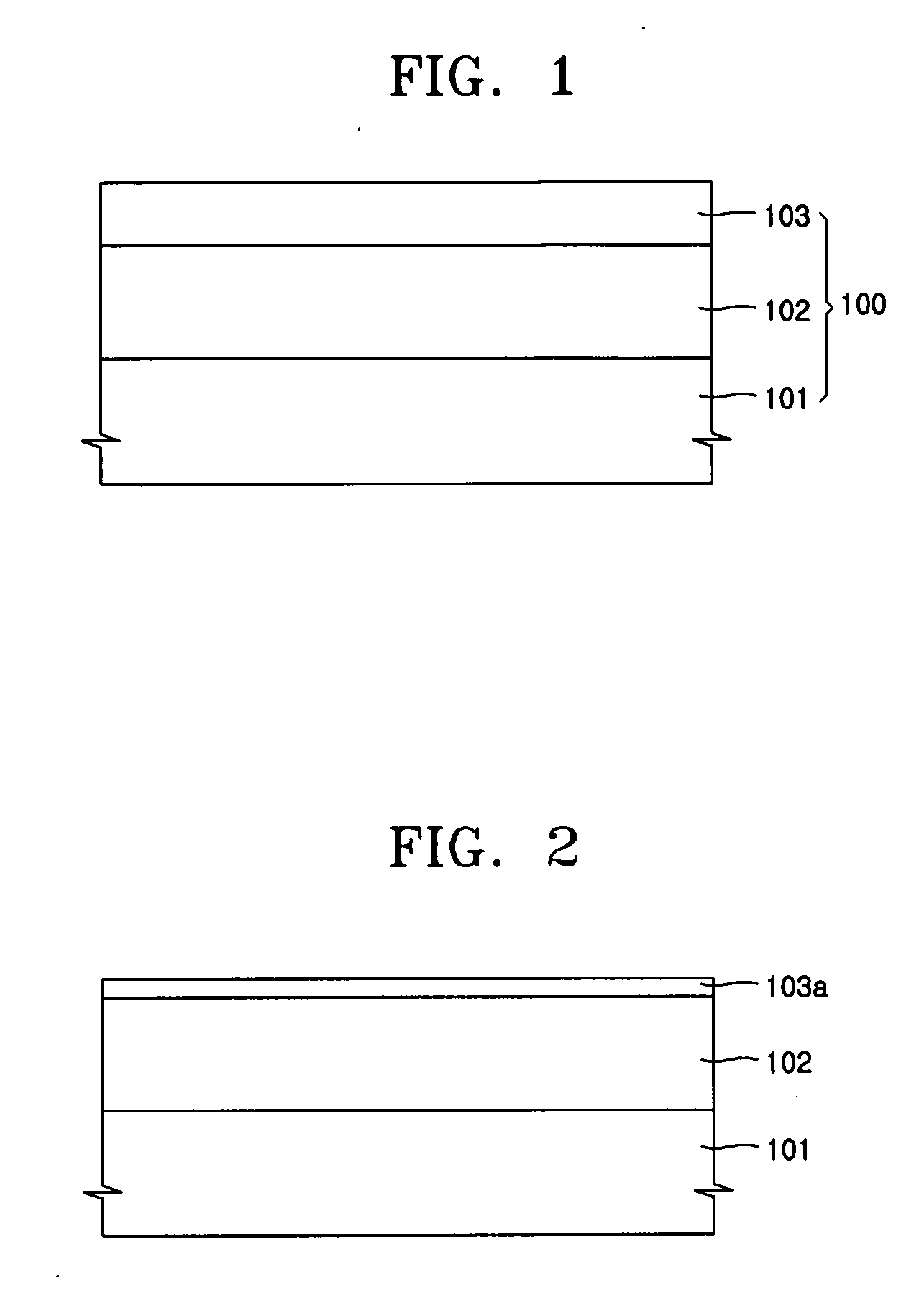

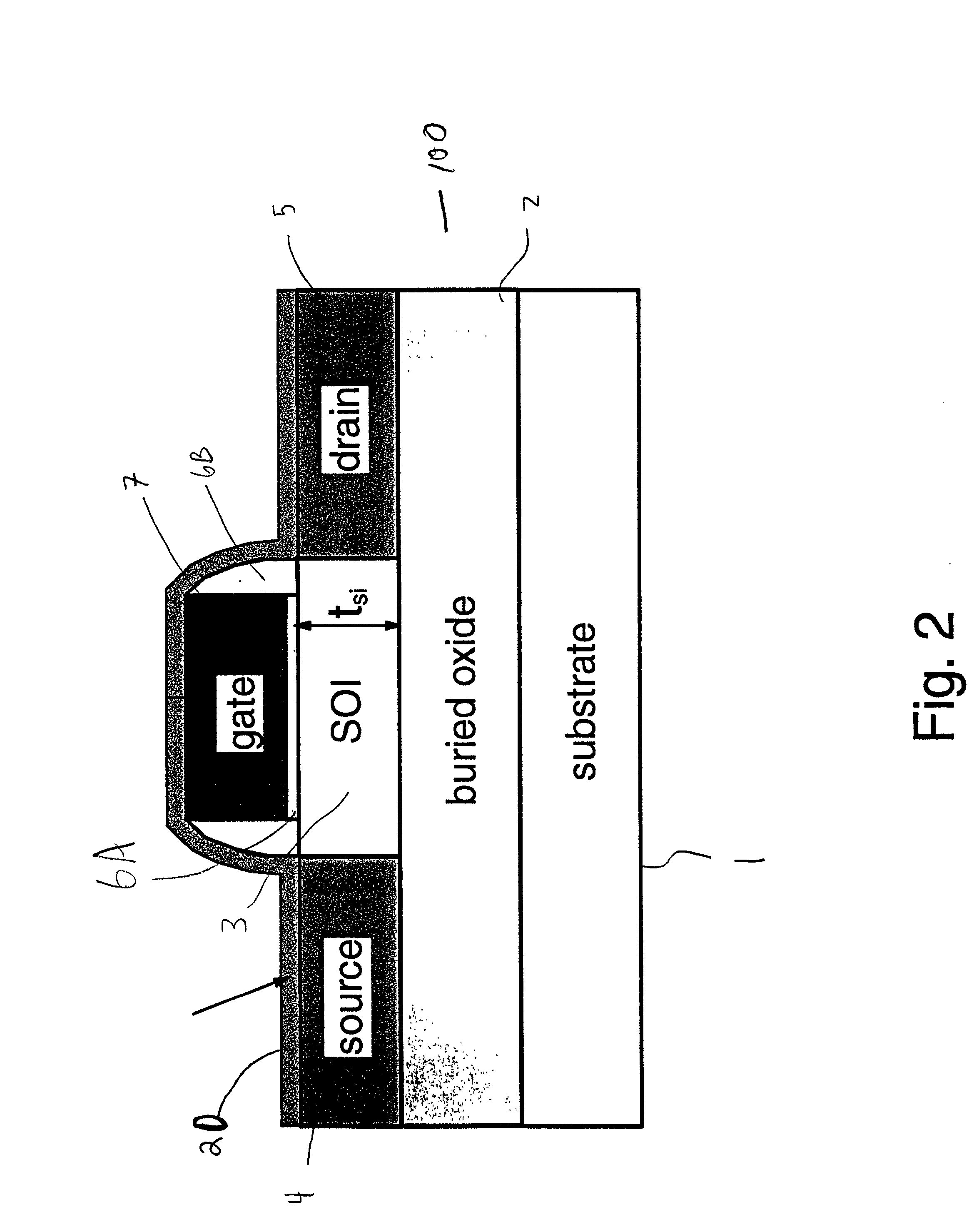

Ultra thin film SOI MOSFET having recessed source/drain structure and method of fabricating the same

InactiveUS20060131648A1Reduce resistanceTotal current dropSolid-state devicesSemiconductor devicesGate stackField-effect transistor

There are provided an ultra thin film silicon on insulator (SOI) metal oxide semiconductor field effect transistor (MOSFET) having a recessed source / drain structure, and a method of fabricating the same. The ultra thin film SOI MOS transistor includes a semiconductor substrate; a buried insulating layer disposed on the semiconductor substrate, and formed recessed except for a center portion thereof; an ultra thin film single crystalline silicon layer pattern disposed on the recessed buried insulating layer; a gate stack disposed on the ultra thin film single crystalline silicon layer pattern, and including a gate insulating layer pattern and a gate conductive layer pattern, which are sequentially stacked; a gate spacer layer disposed on sidewalls of the gate stack; and a recessed source / drain region disposed on the recessed buried insulating layer, and formed to overlap a bottom surface portion of the ultra thin film single crystalline silicon layer pattern, which does not overlap the center portion of the recessed buried insulating layer.

Owner:ELECTRONICS & TELECOMM RES INST

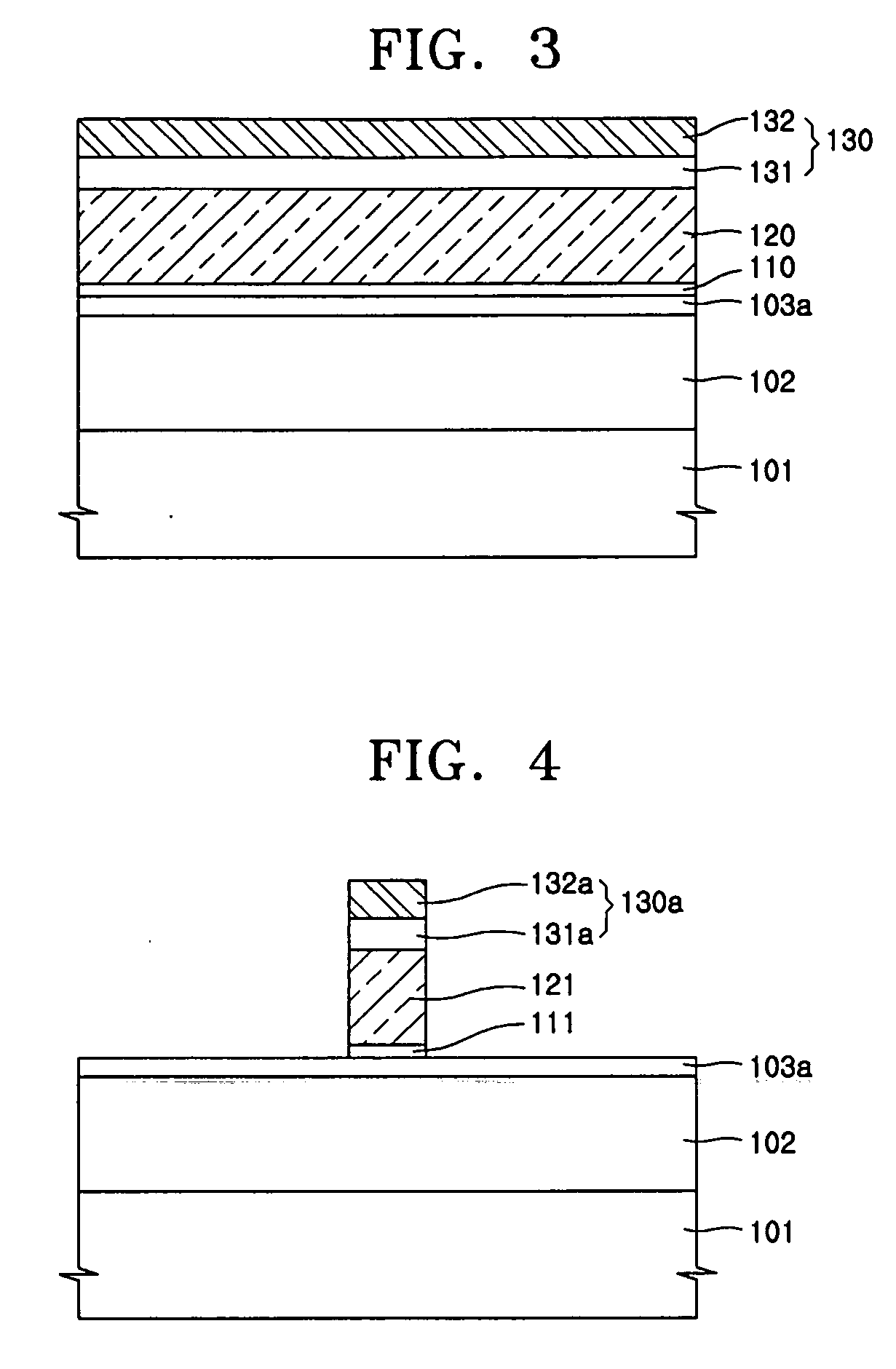

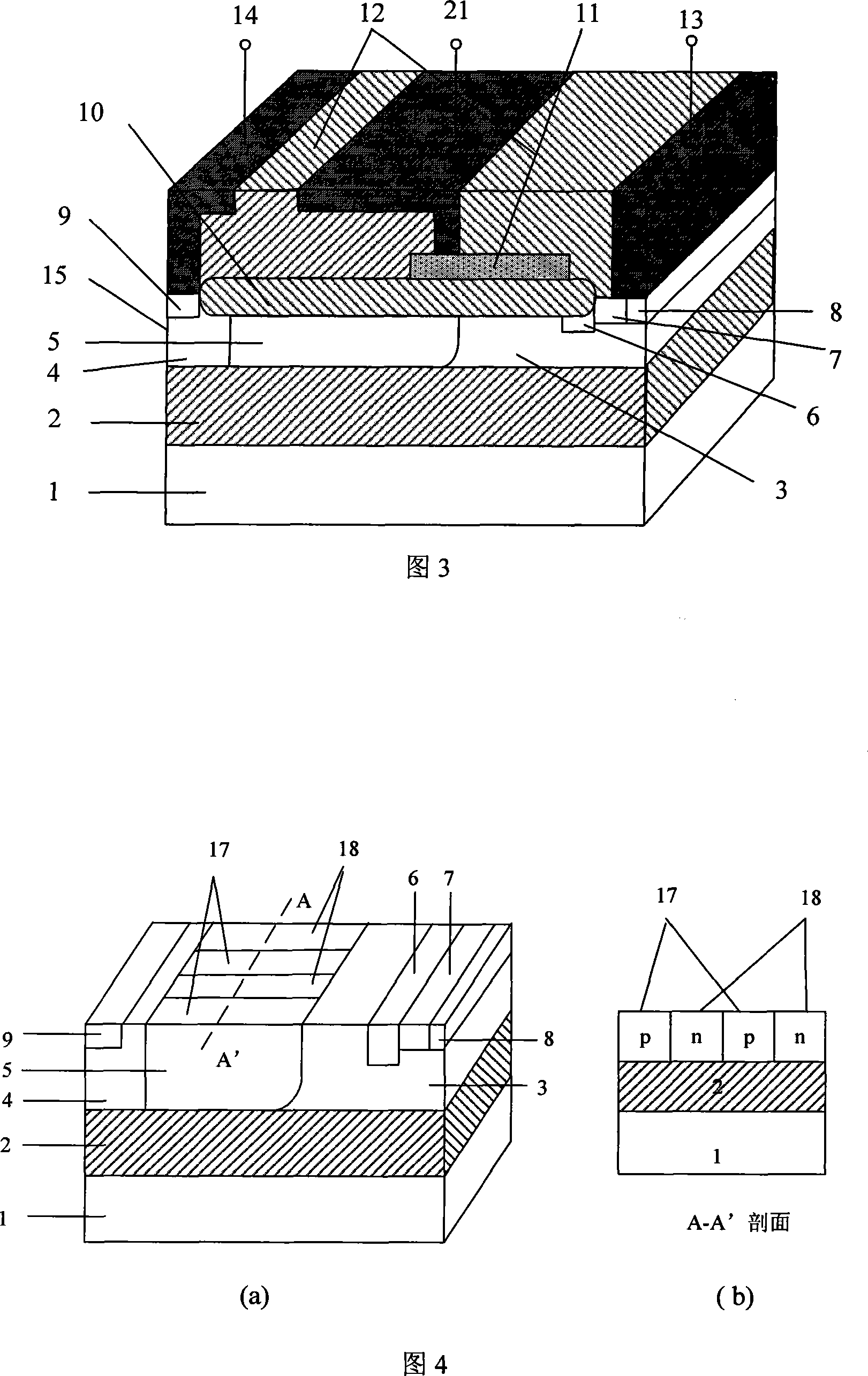

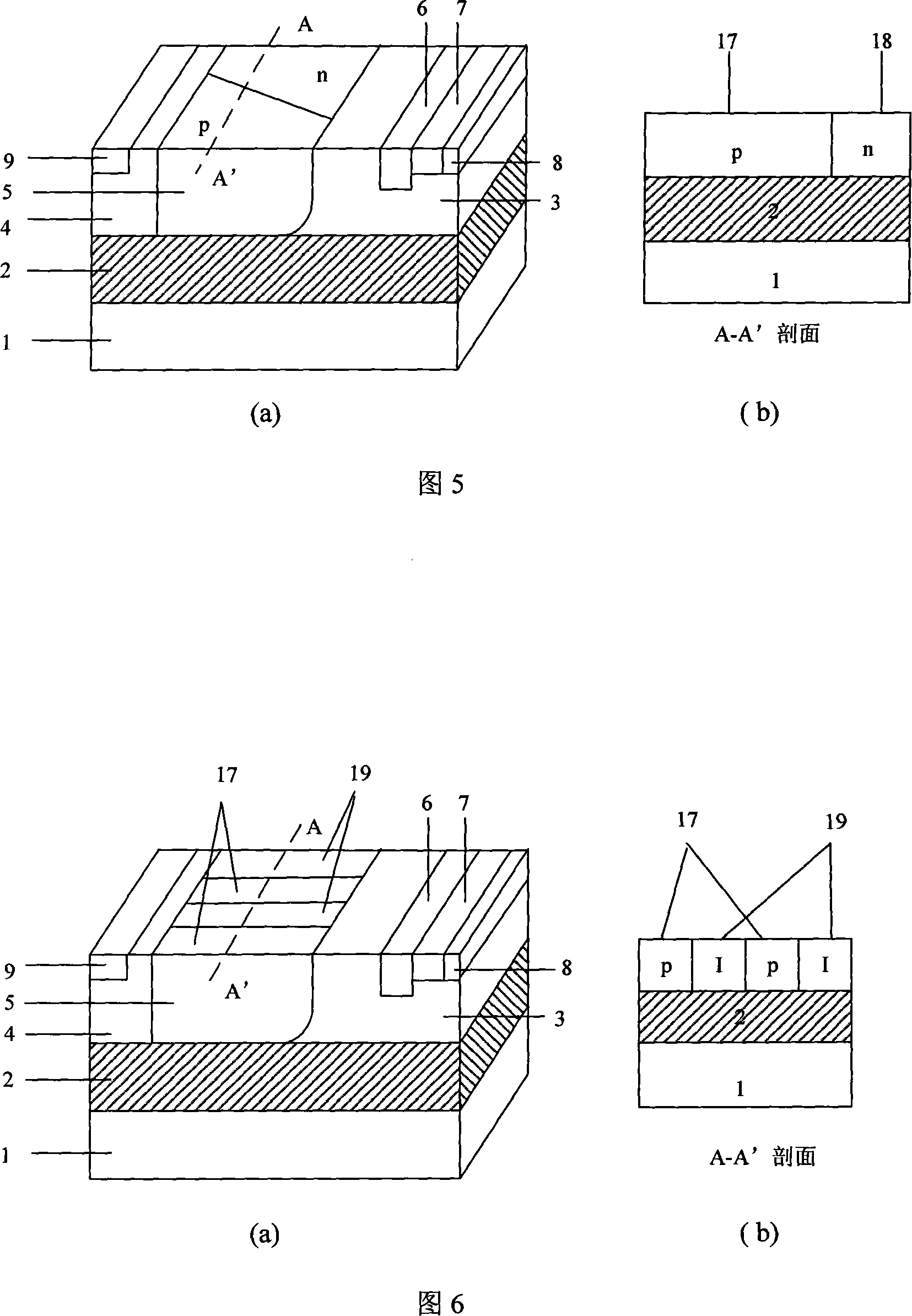

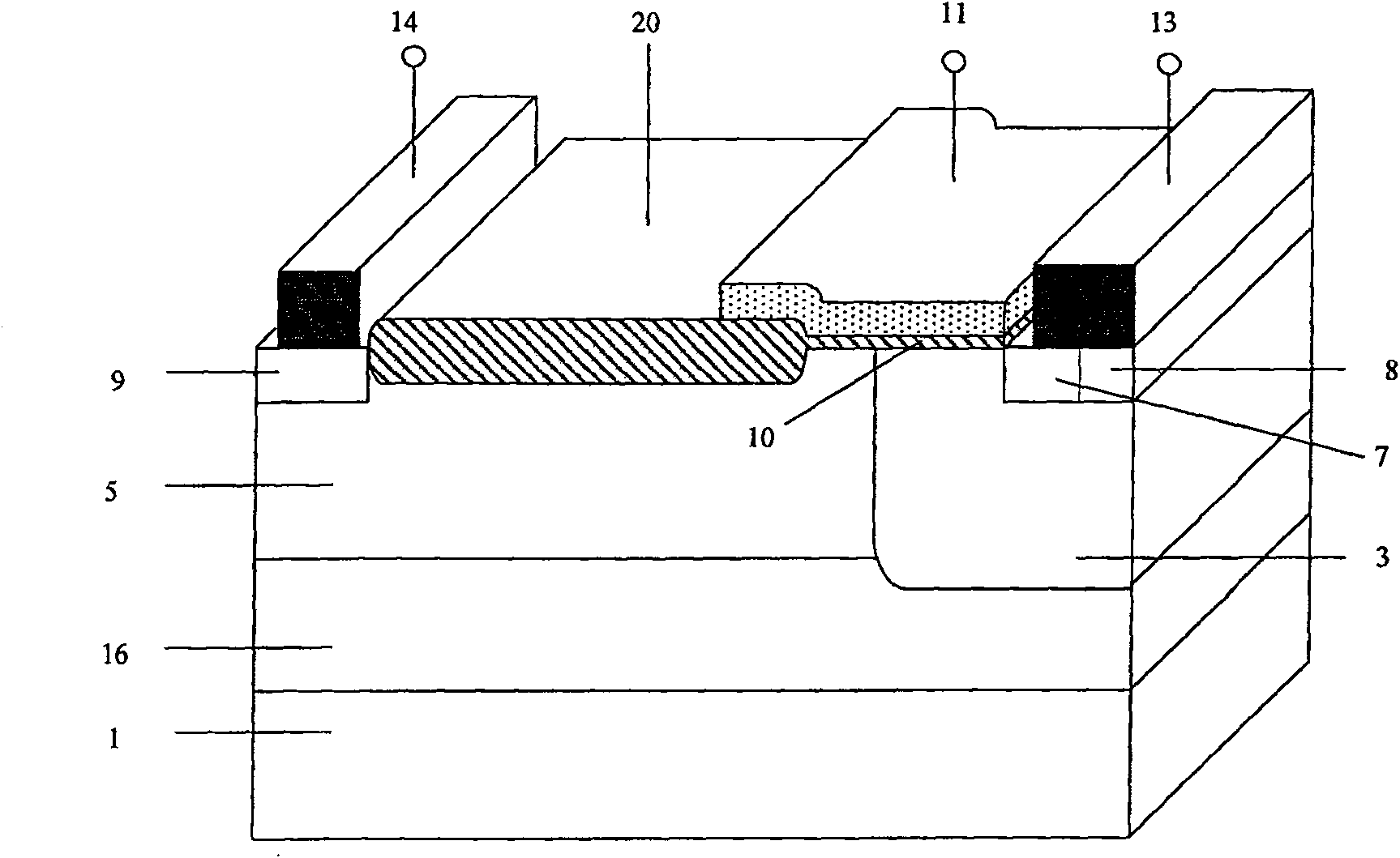

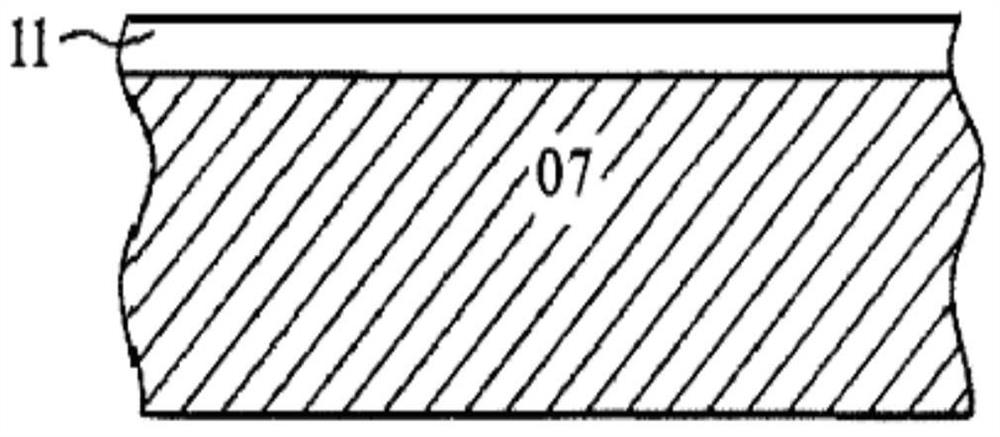

Thin film SOI thick grid oxygen power device with grid field plate

InactiveCN101221986AFast switching speedImprove breakdown characteristicsSemiconductor devicesPeak valueOxygen

The invention belongs to the semi-conductor power device technical field. A SOI layer of the device is thinner (1to 2um); a grid oxide layer is thick (100 to 800nm); a grid field plate gets across a grid and extends above a drift region. An active expansion region positioned below the thick grid oxide layer and connected with a source region can be also arranged in the body of the device to assure the more effective formation of the whole device. The grid oxide layer of the invention is thicker, can bear high grid-source voltage and meet the need of a level displacement circuit; the SIO layer is thinner, can decrease the parasitic effect of the device and reduce consumption; through adding the grid field plate striding over the grid on the surface of the power device, the depletion of the drift region can be increased, the electric field peak value on the silicon surface at the tail end of the grid is decreased, the breakdown characteristic of the device is improved, further more the concentration of the drift region is helped to improve, and the on-state resistance of the device is decreased. The invention has the advantages of low parasitic effect, fast speed, low power consumption, strong radiation-resistant ability and so on, and is compatible with the standard process. By adopting the invention, various high-voltage, high-speed and low conducting loss devices of excellent performance can be produced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

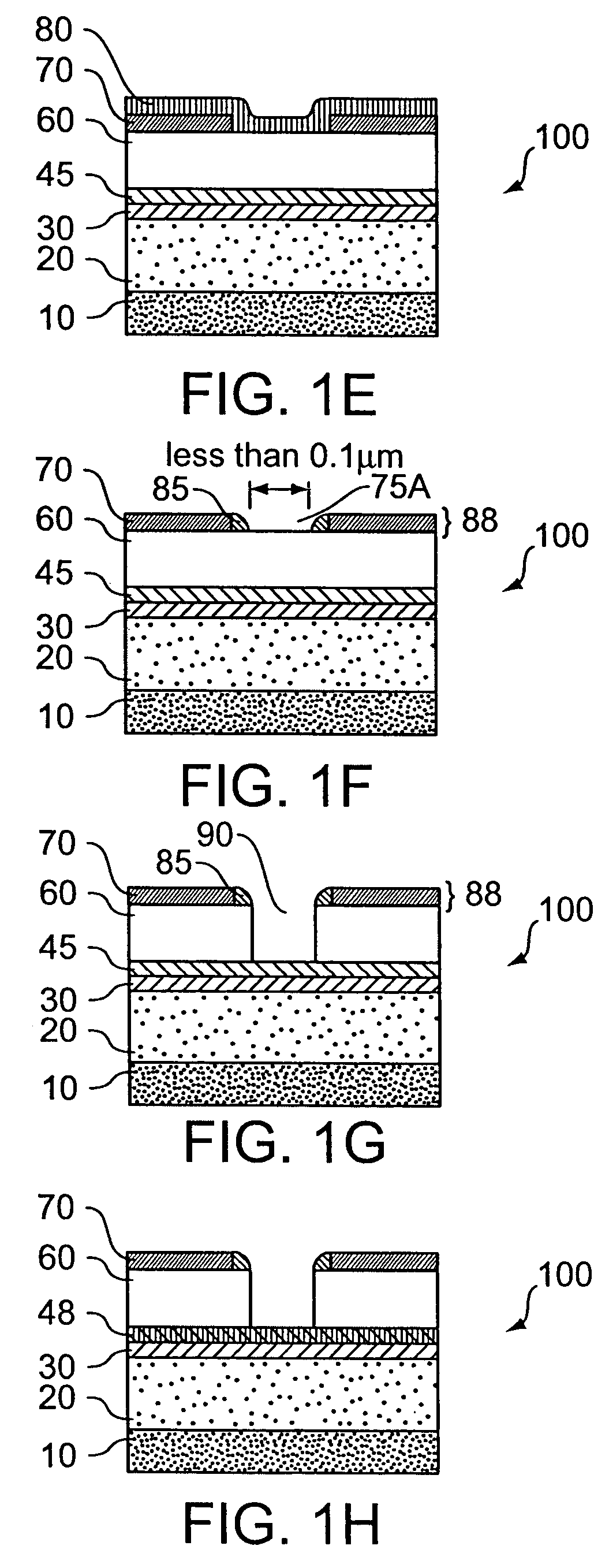

Self-aligned silicone process for low resistivity contacts to thin film silicon-on-insulator mosfets

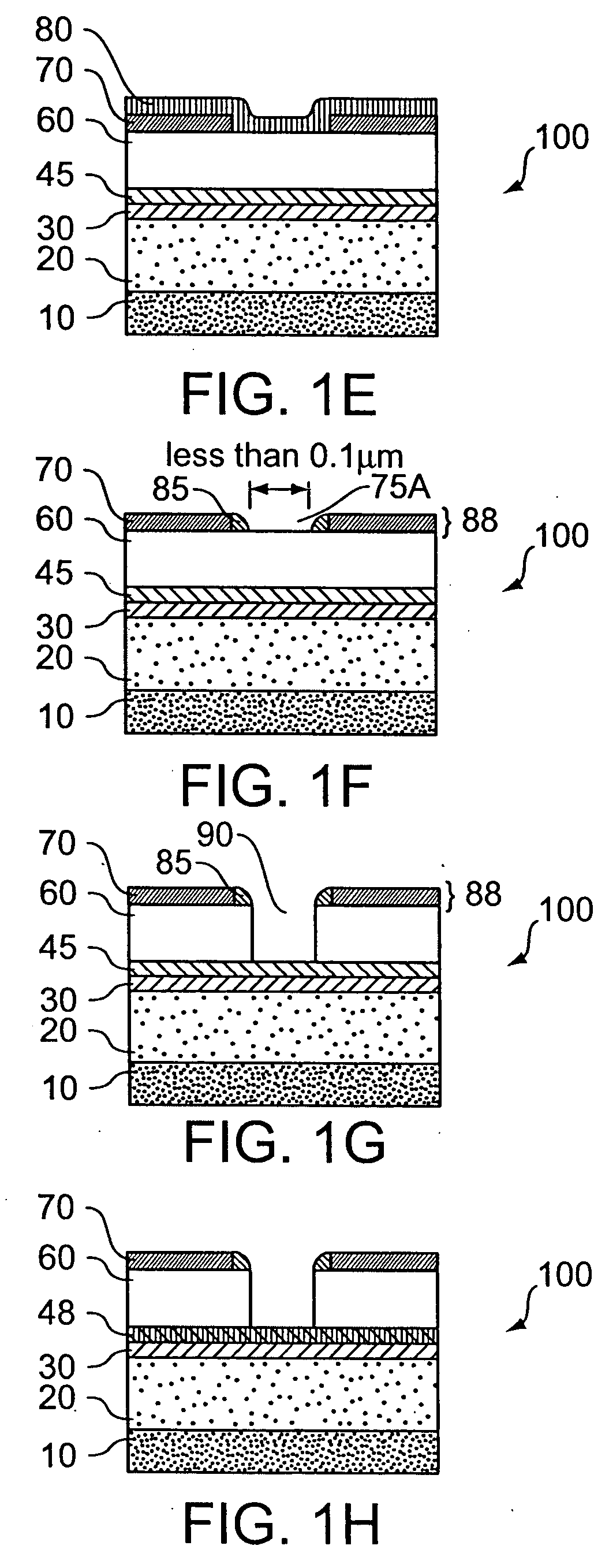

InactiveUS20020031909A1Minimize consumptionConsumption of the thin SOI film is additionally reducedTransistorSemiconductor/solid-state device manufacturingSalicideSilicon membrane

A silicide processing method for a thin film SOI device including depositing a metal or an alloy on a gate and a source / drain structure formed in a silicon-on-insulator film, reacting the metal or alloy at a first temperature with the silicon-on-insulator film to form a first alloy, etching the unreacted layer of the metal (or alloy) selectively, depositing a Si film on the first alloy, reacting the Si film at a second temperature to form a second alloy, and etching the unreacted layer of the Si film selectively.

Owner:INT BUSINESS MASCH CORP

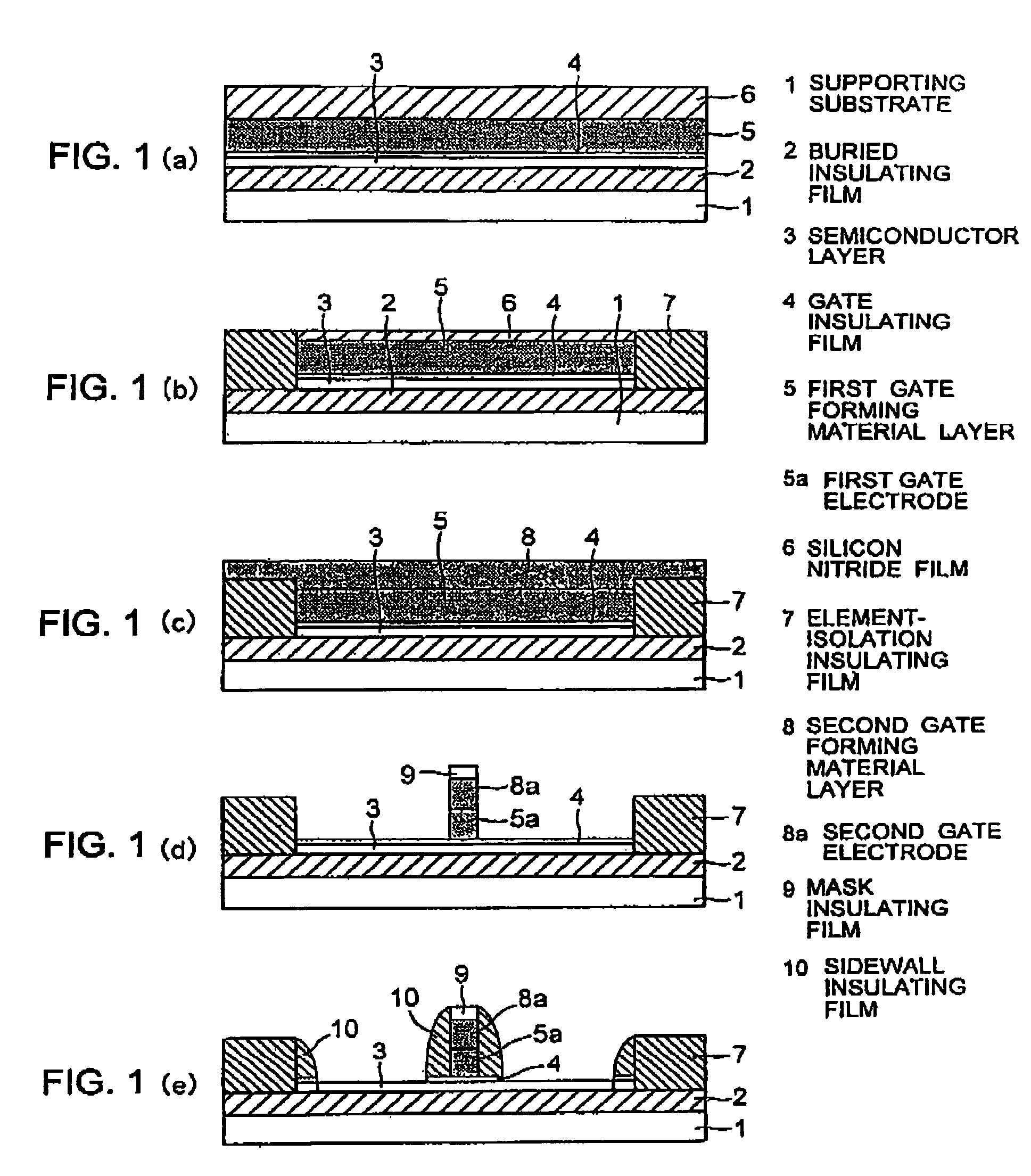

Method of manufacturing semiconductor device

InactiveUS6908820B2Improvement of roll-off characteristicReduce parasitic resistanceTransistorSemiconductor/solid-state device manufacturingSoi substrateEngineering

Disclosed is a method of manufacturing a semiconductor device. A plurality of device separation regions are formed in an SOI layer of an SOI substrate, a desired impurity is implanted into a body portion of an Si active layer region, and therereafter a gate electrode is formed with a gate insulation film therebetween. Thereafter, an impurity is implanted into the Si active layer region to form extension portions of source / drain portions, and then an impurity different in polarity from the impurity in the source / drain portions is halo-implanted to form a reverse-characteristic layer. In the halo implantation, the range of projection is set to reach the inside of a buried oxide film. With this configuration, in a fully depleted SOI-MOSFET or the like provided with a thin film SOI layer, it is made possible to simultaneously achieve an improvement of roll-off characteristic and a reduction in parasitic resistance and to secure a sufficient driving capability.

Owner:SONY CORP

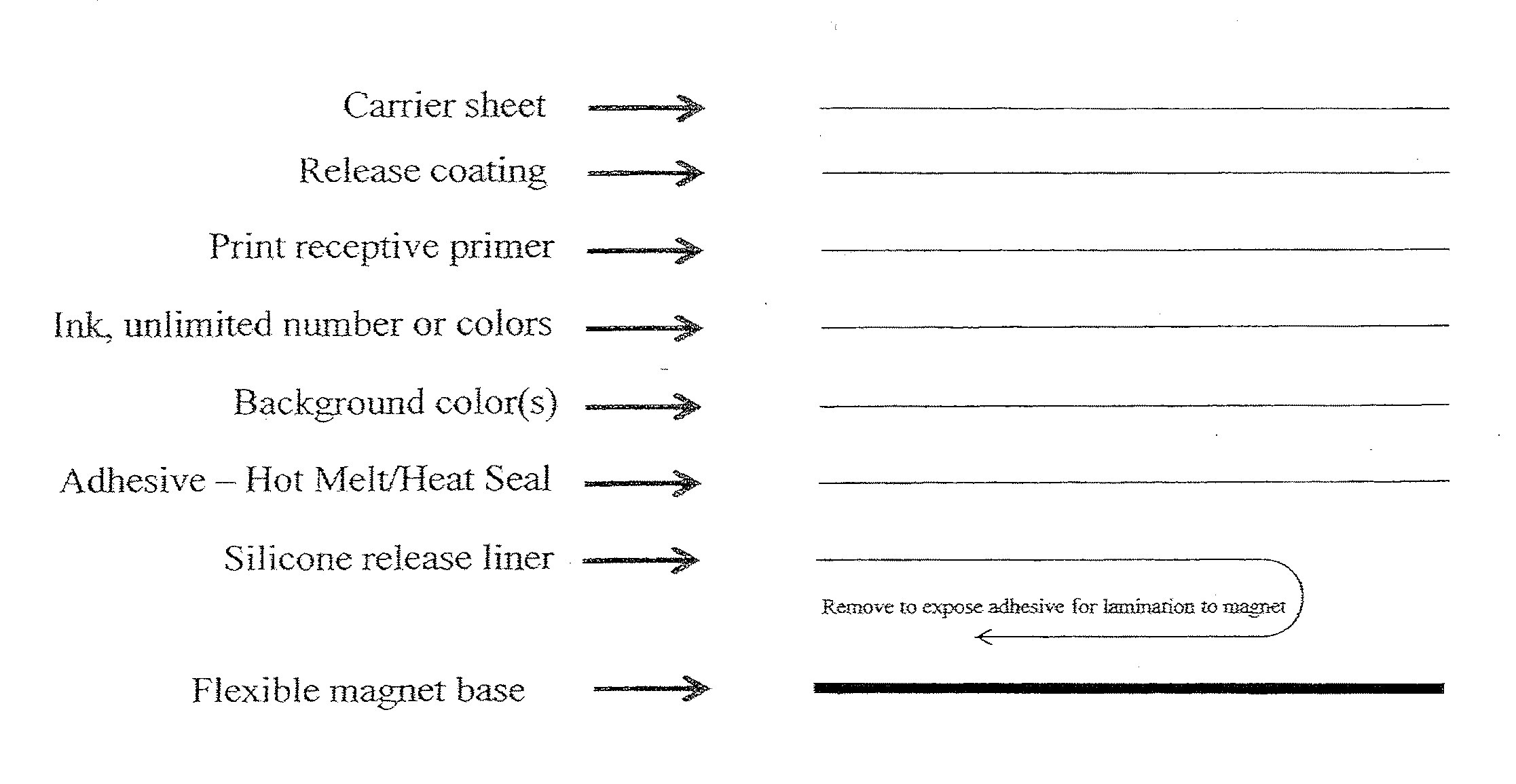

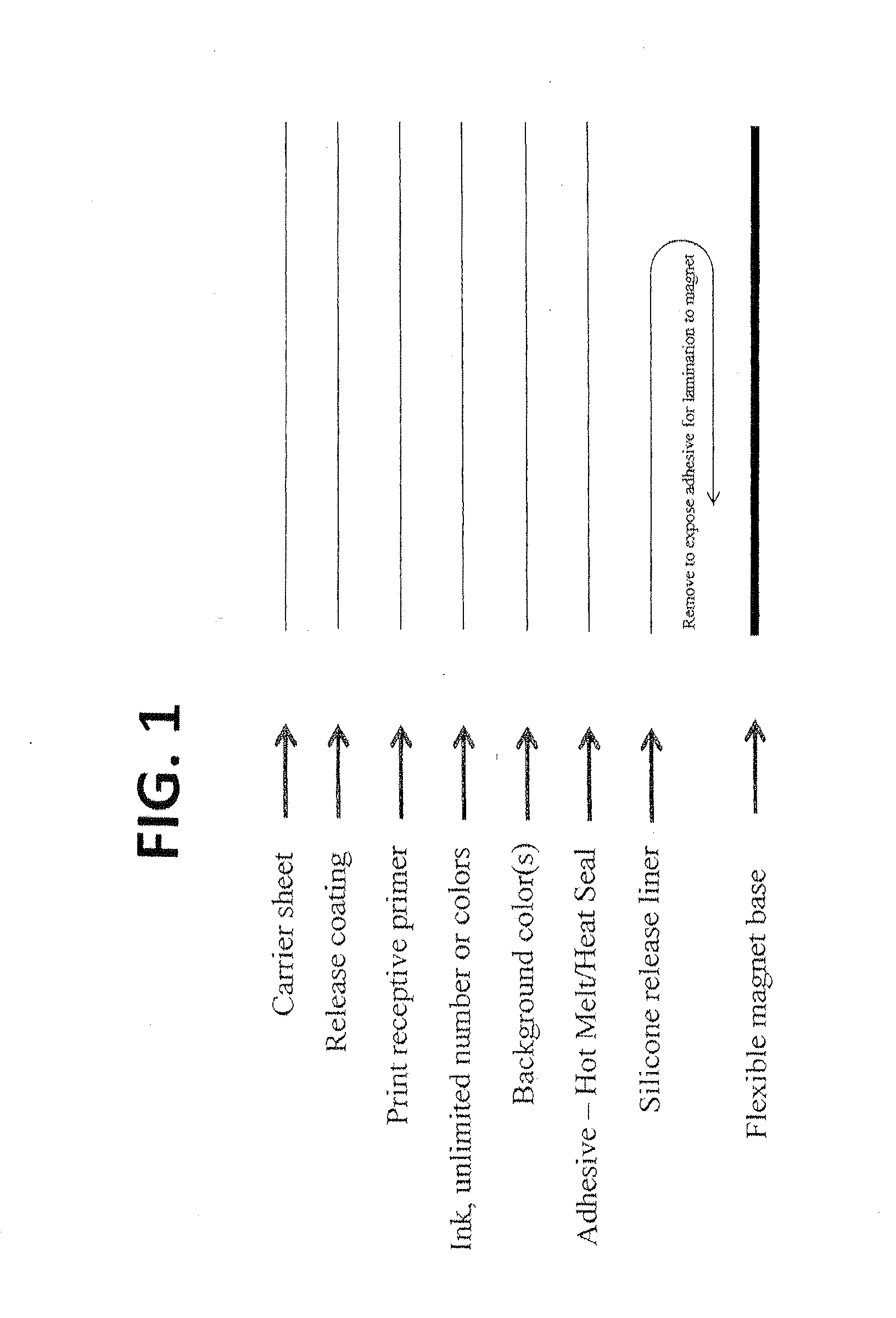

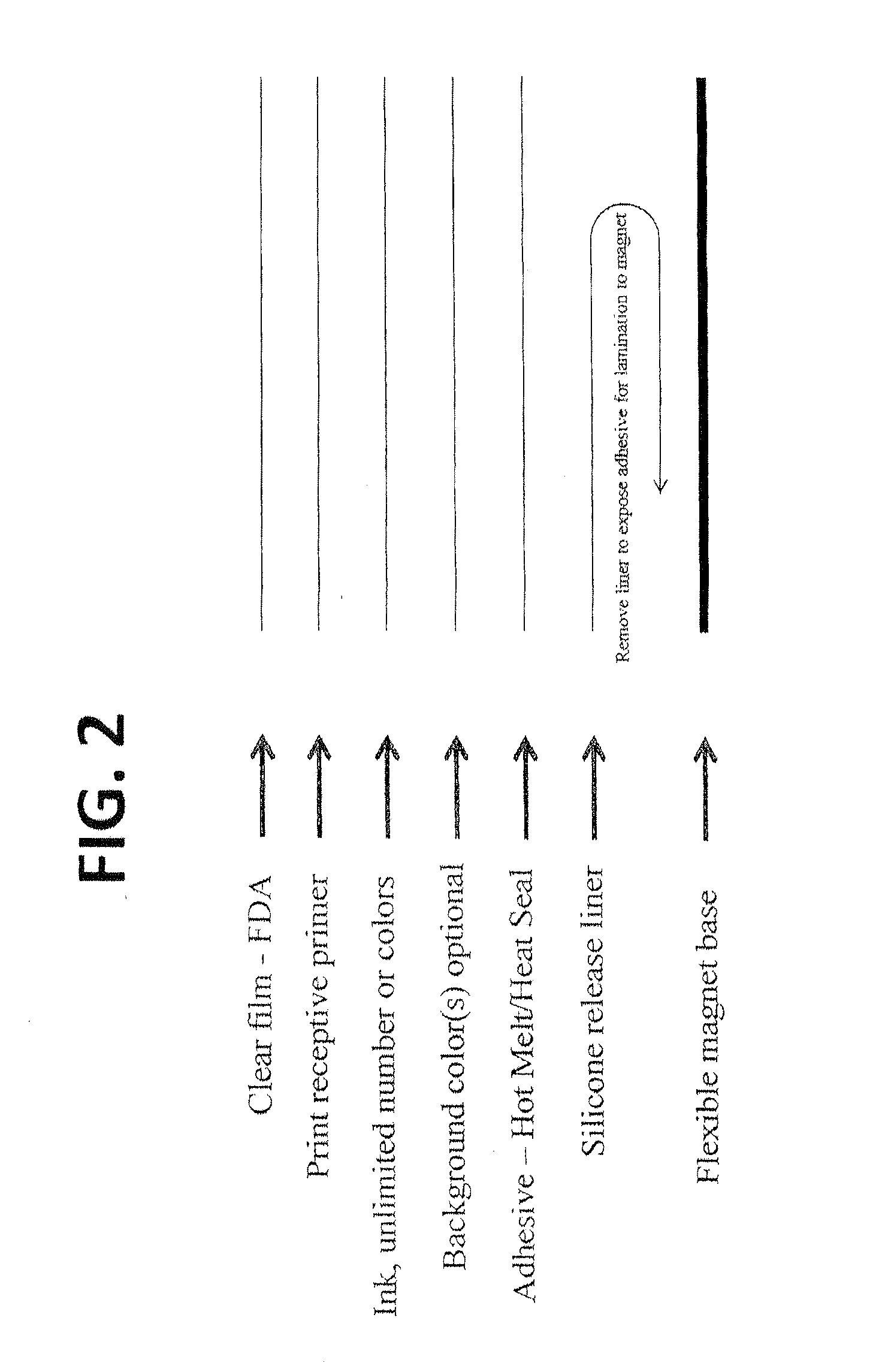

Decorated magnetic substrate

InactiveUS20120207960A1Lamination ancillary operationsLayered product treatmentAdhesiveComposite laminates

A disc having application in a bottom up beverage cup filling process for lifting to receive a beverage through a cup hole and for sealing the hole after filling. A composite laminate includes FDA recognized films, inks and adhesives, and including either a magnet substrate or a flexible magnetic receptive coating for attachment to a substrate. Various constructions, methods and applications are disclosed.

Owner:GENERAL DATA

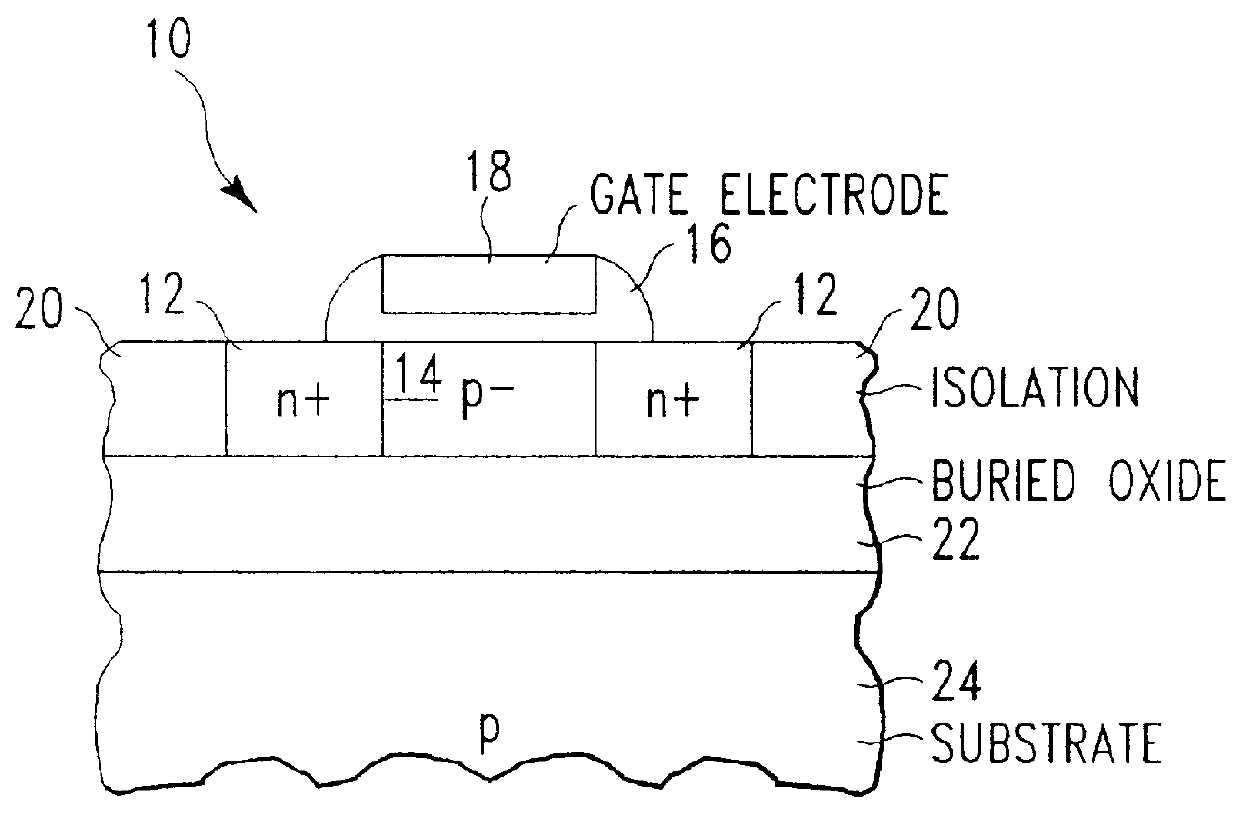

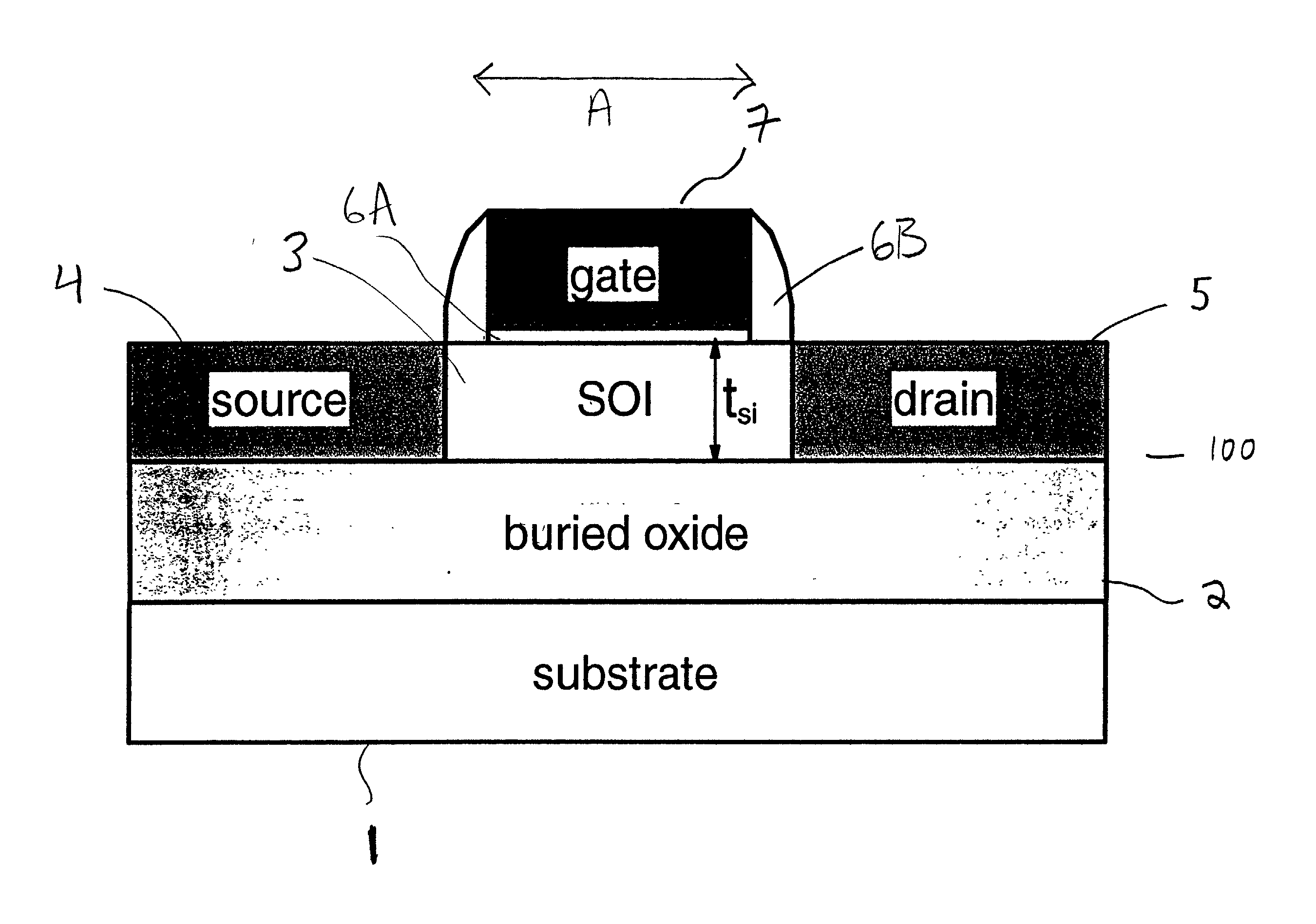

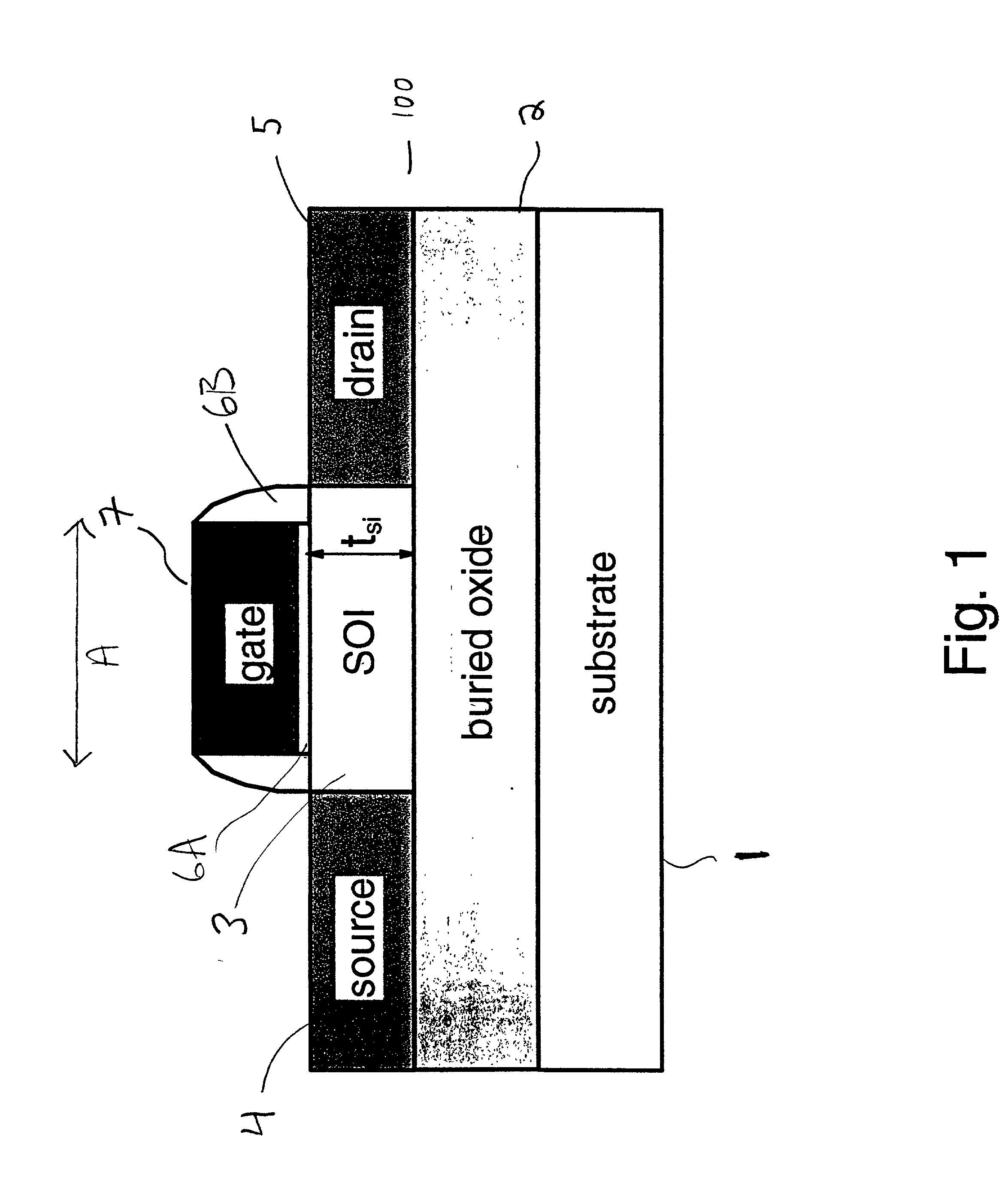

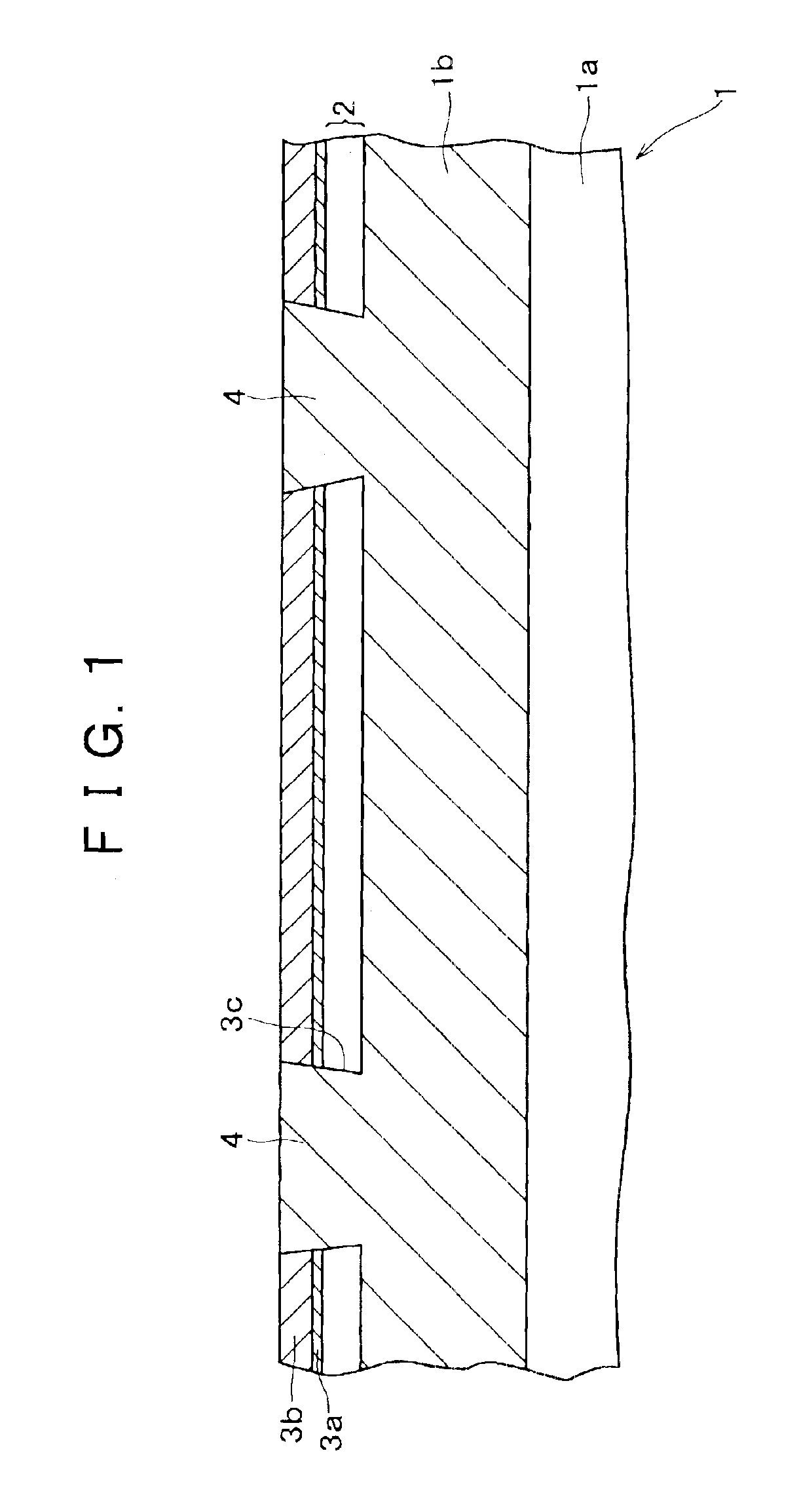

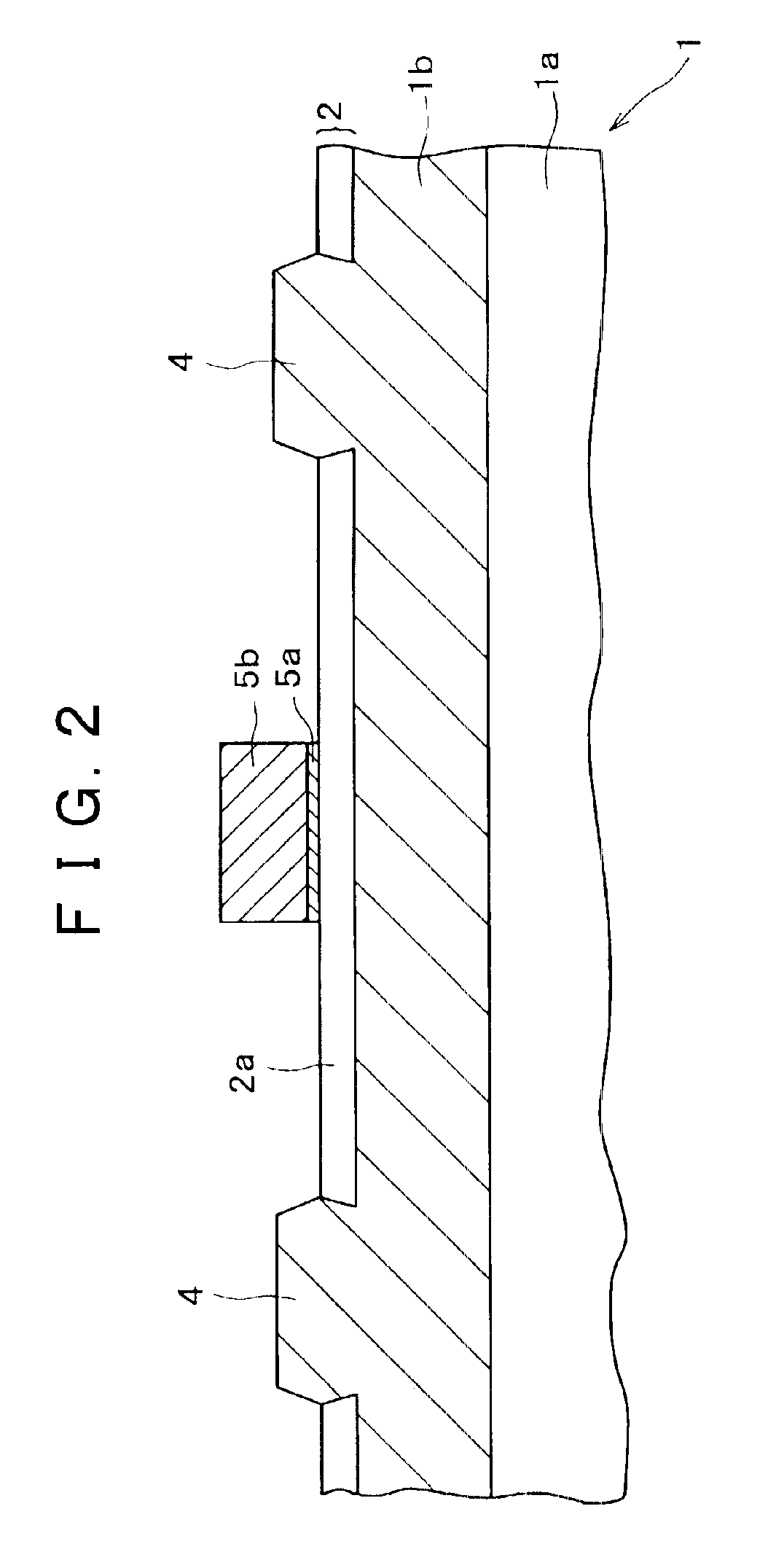

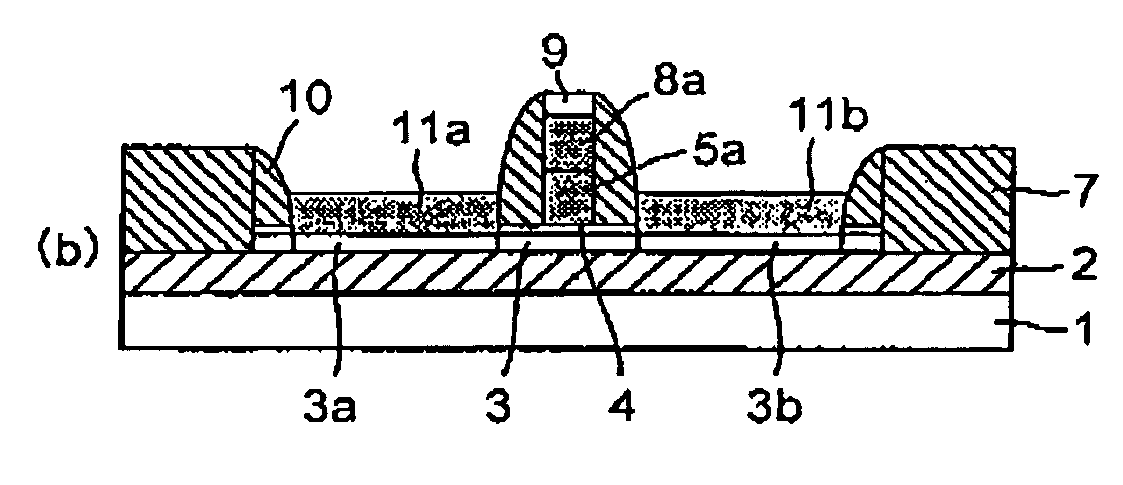

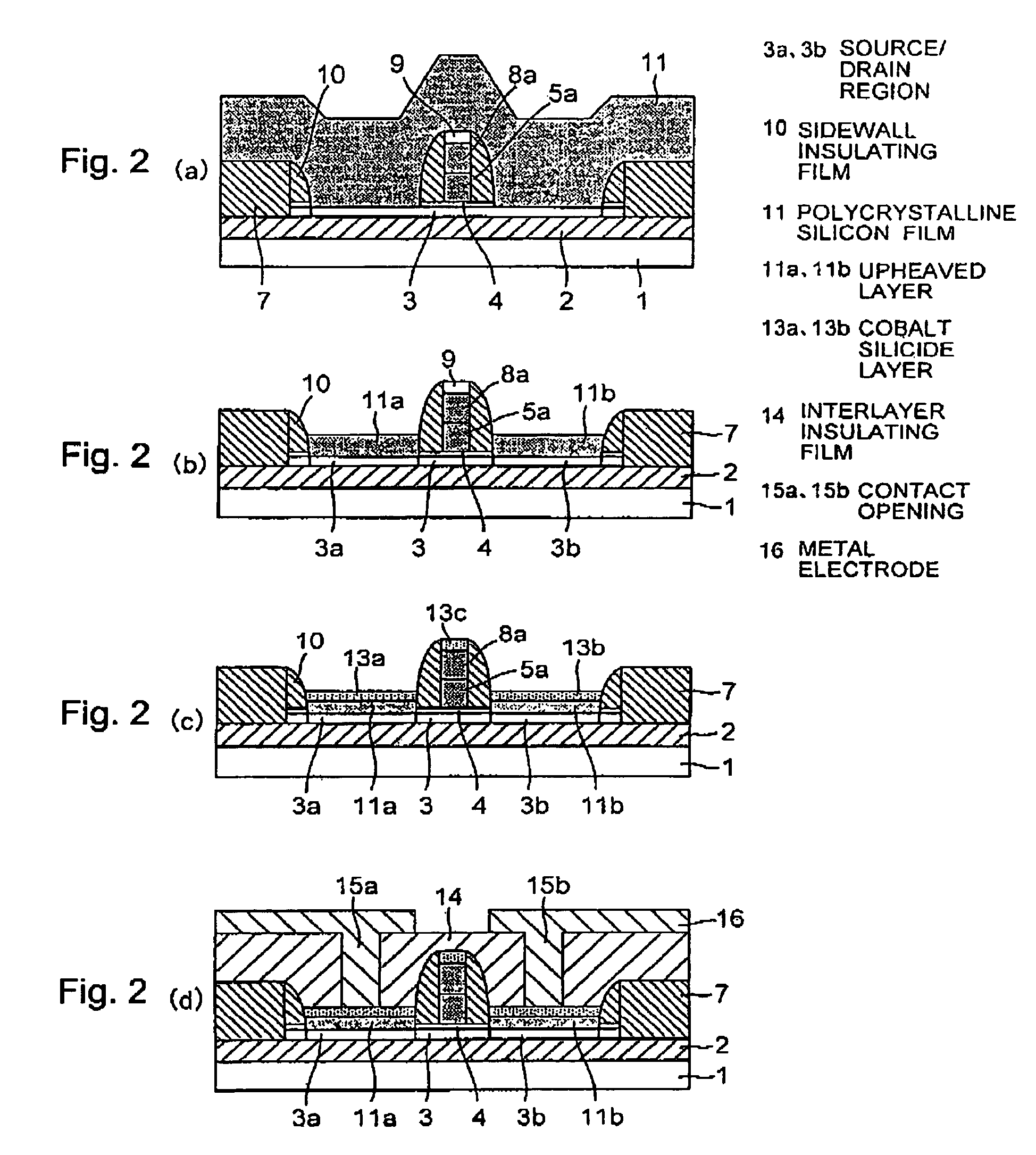

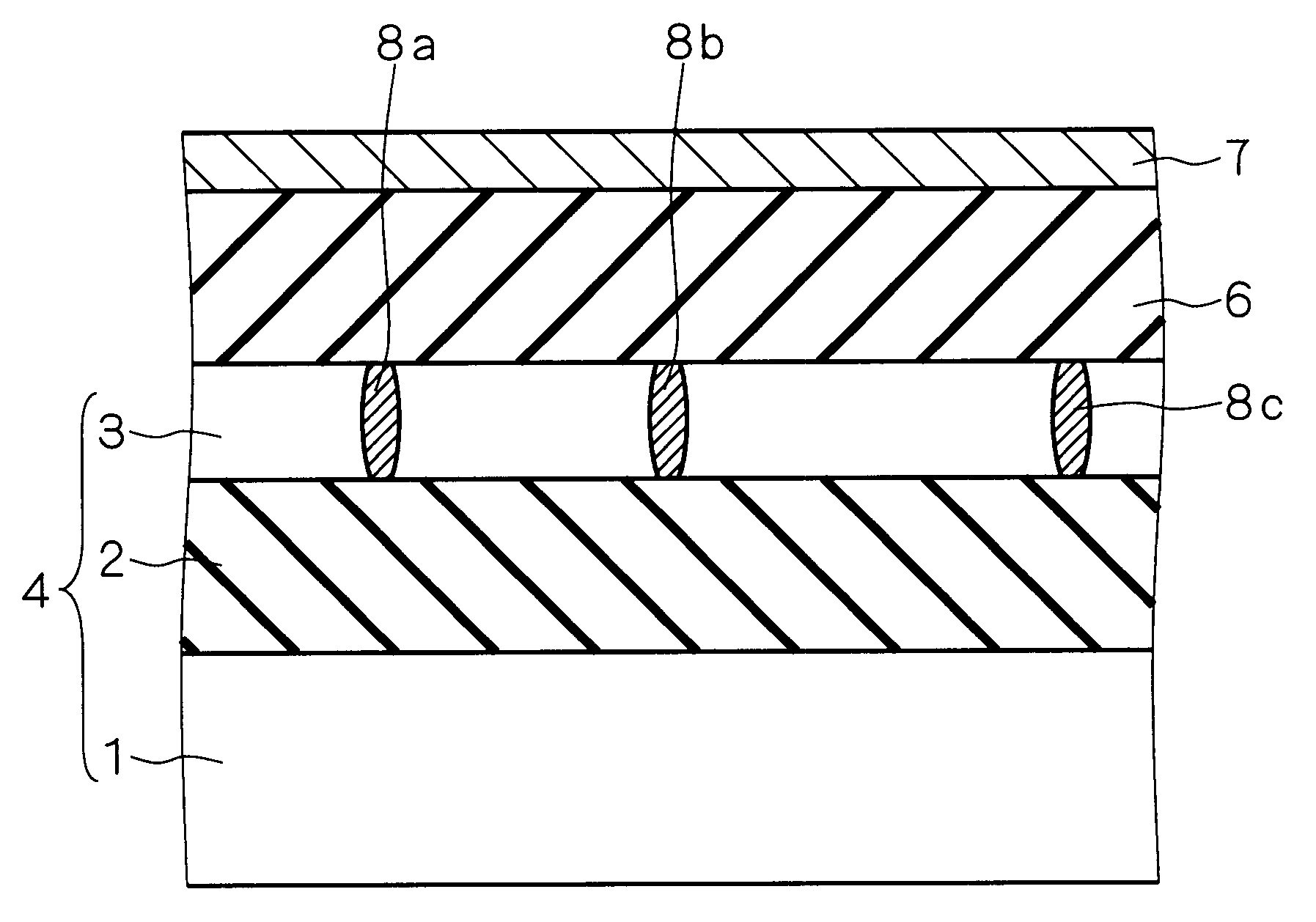

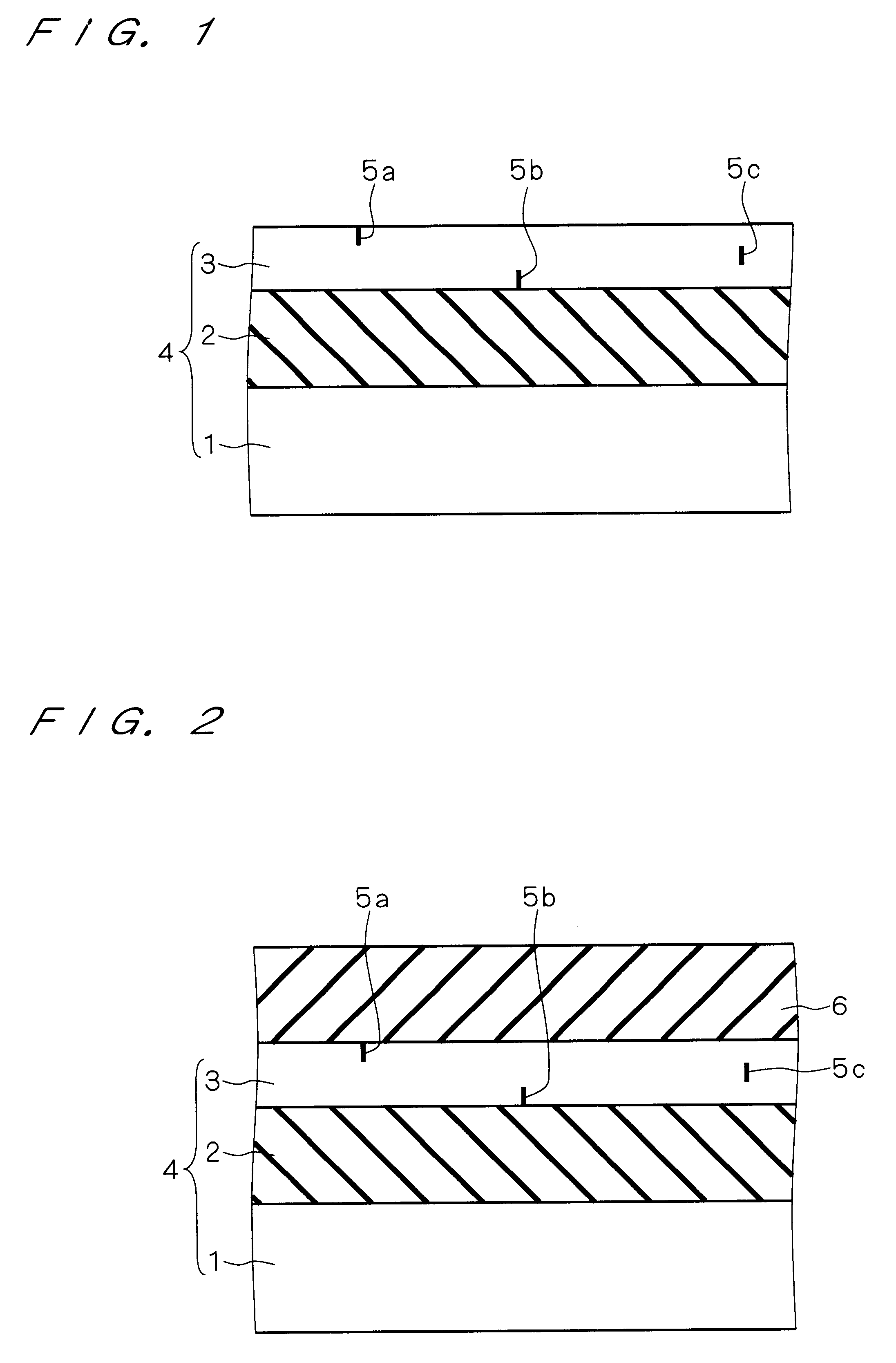

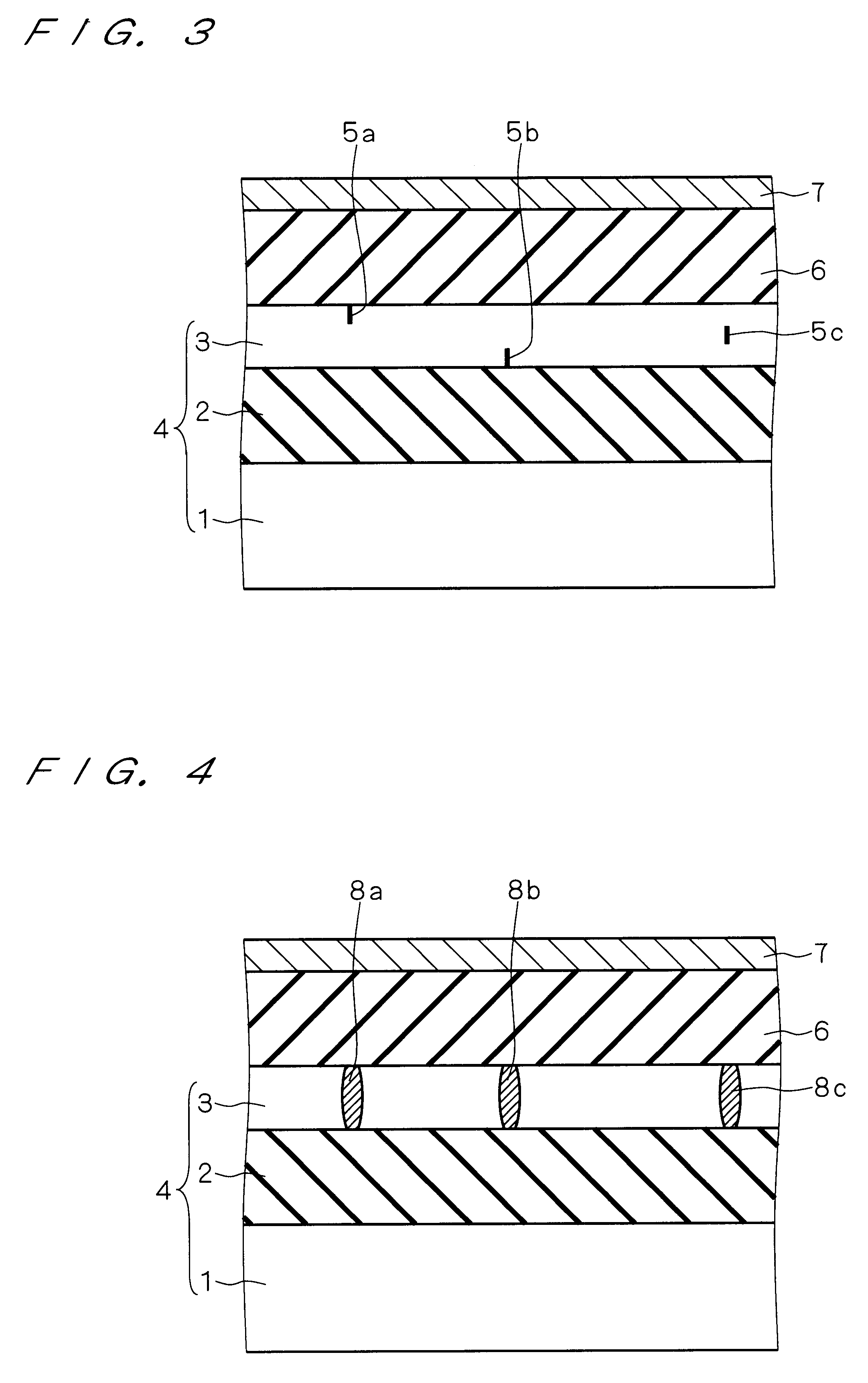

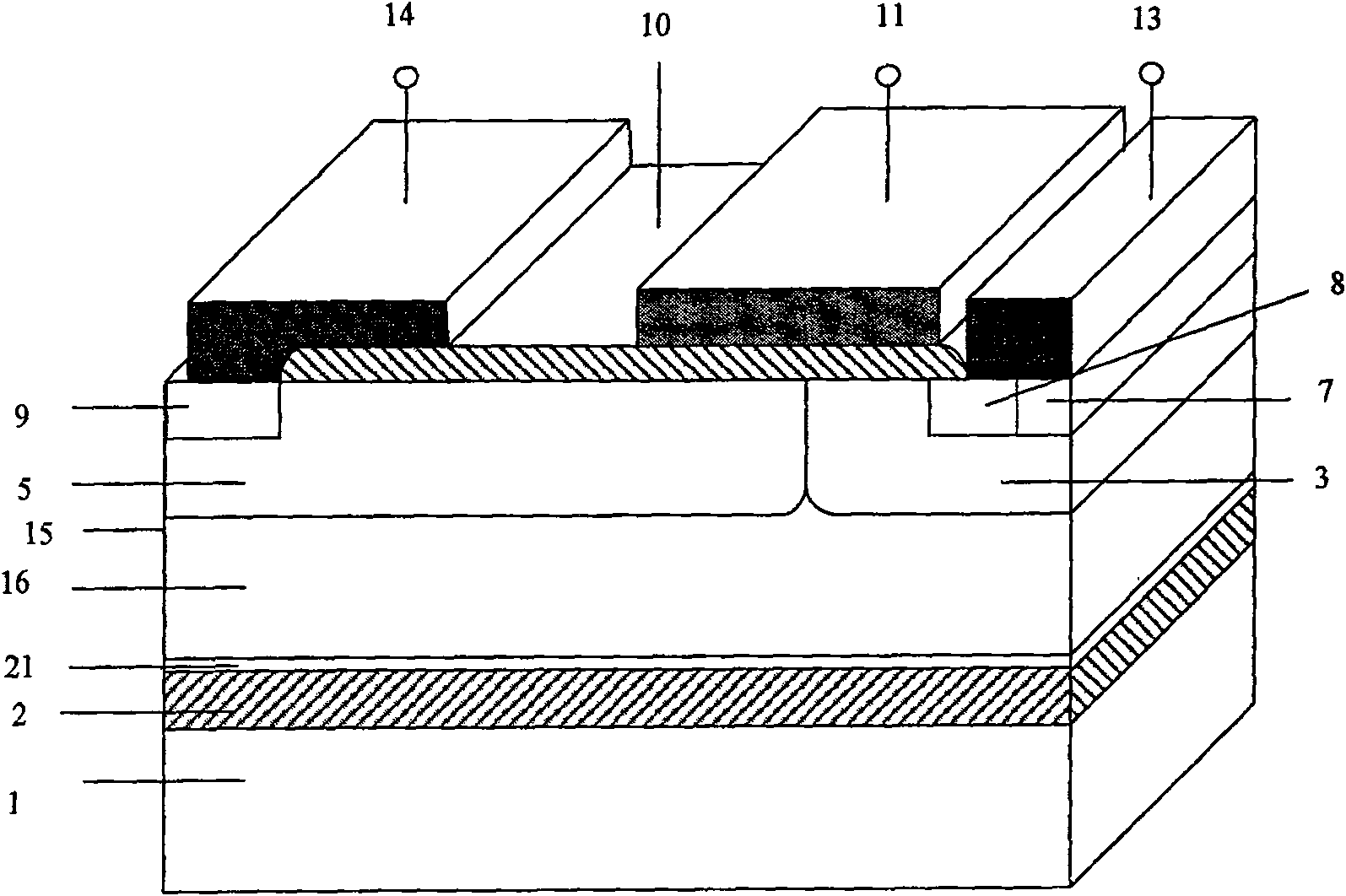

MOSFET formed on a silicon-on-insulator substrate having a SOI layer and method of manufacturing

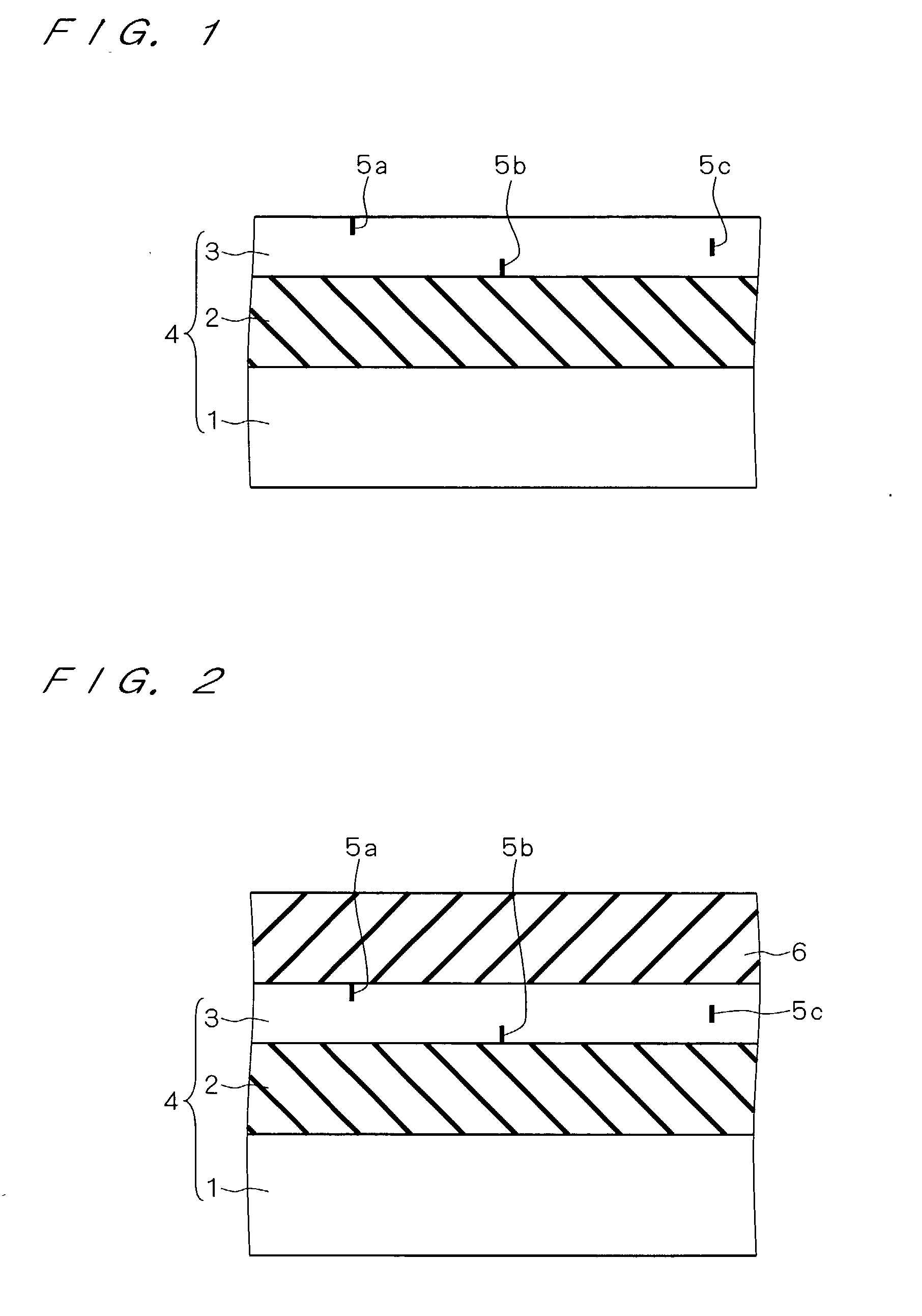

InactiveUS7247910B2TransistorSemiconductor/solid-state device detailsLithography processMetal electrodes

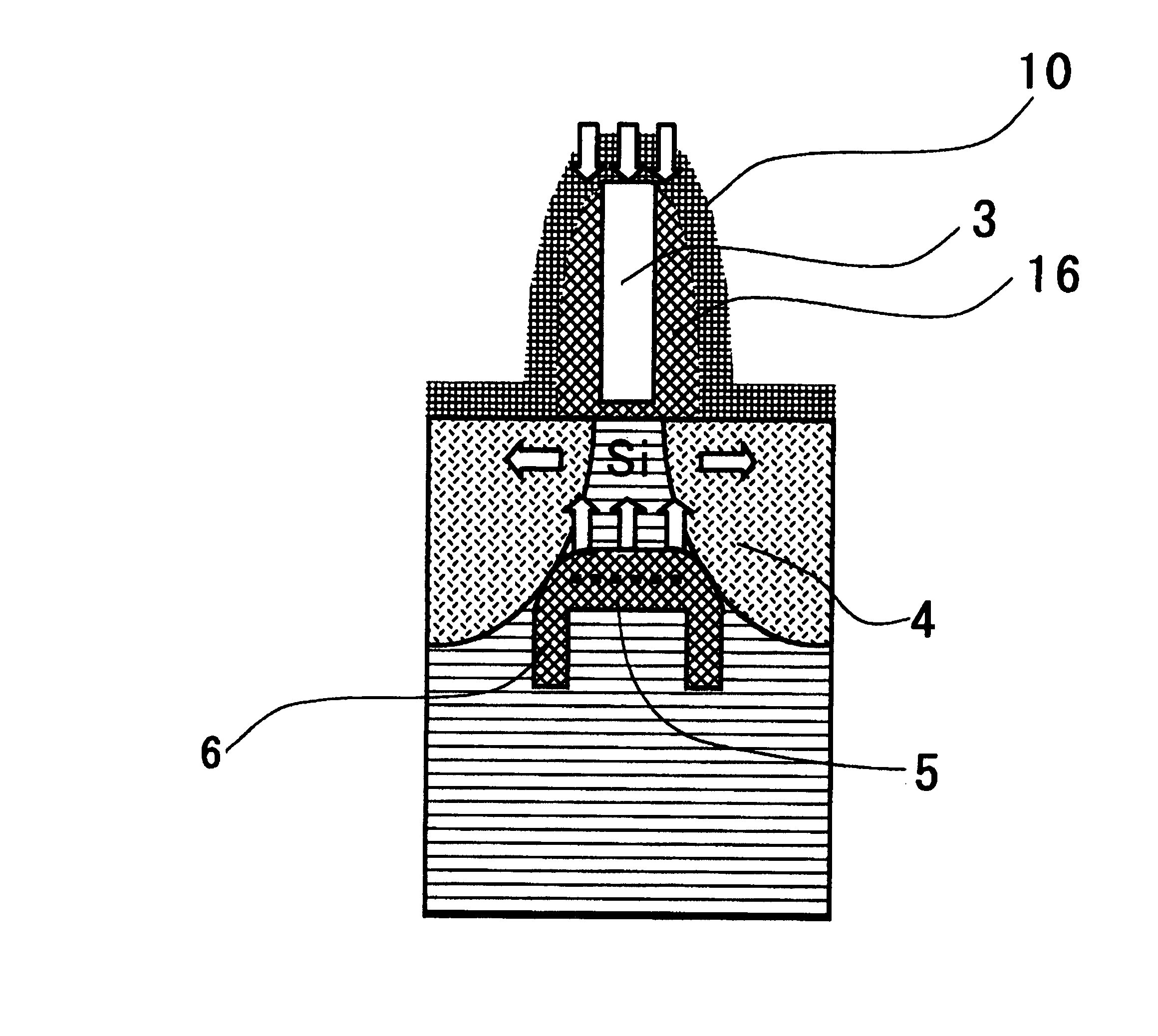

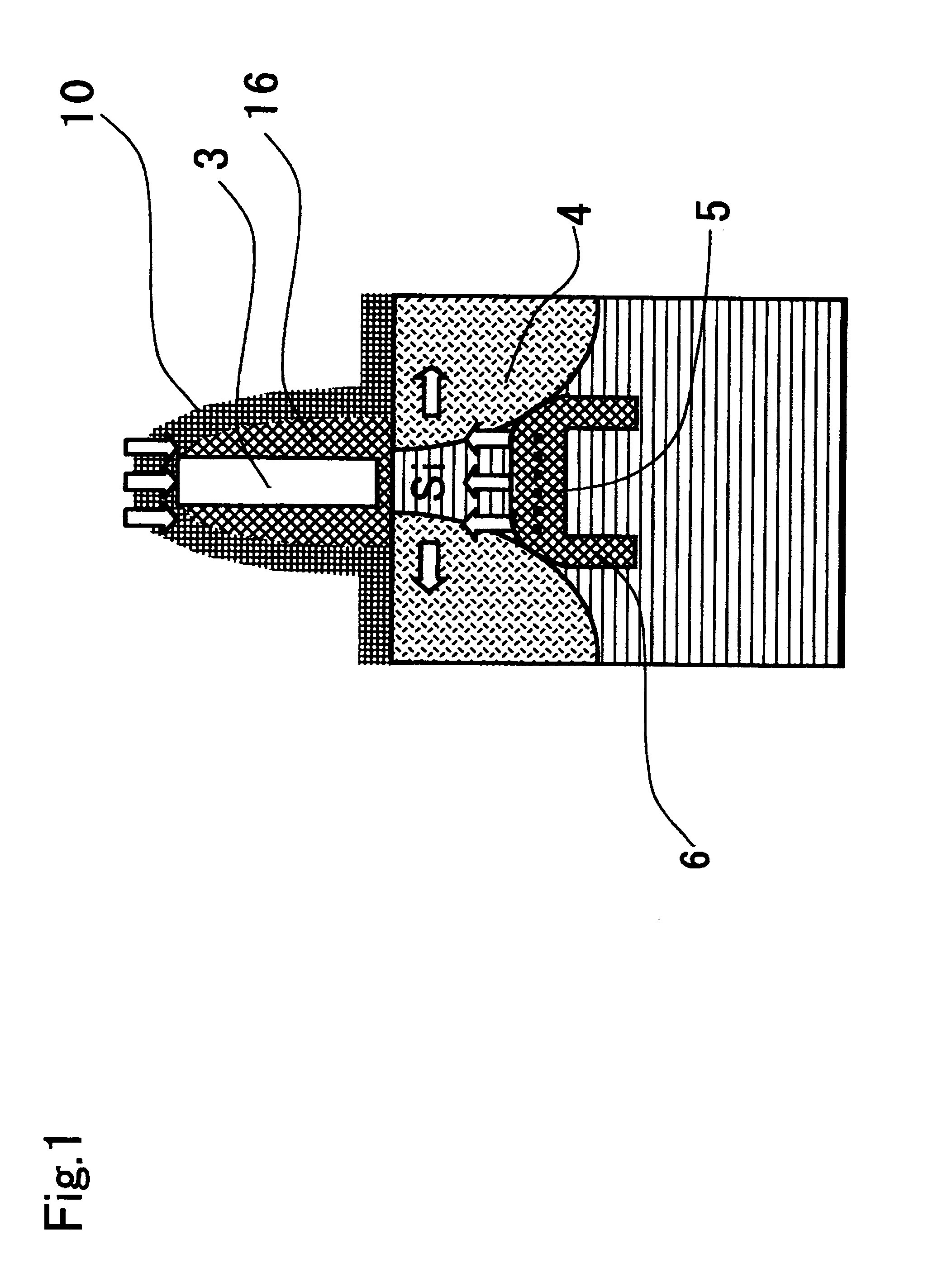

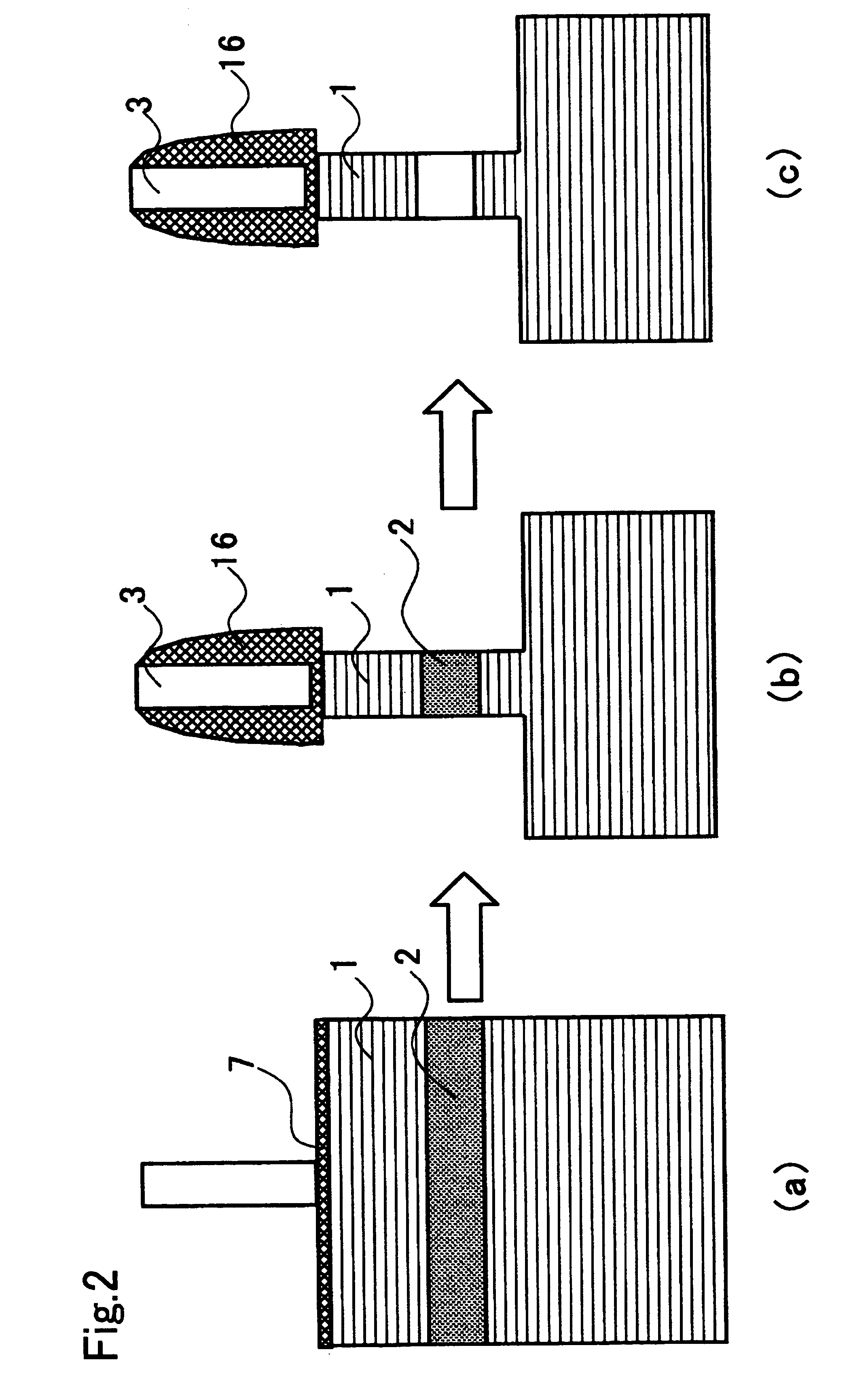

In a FET having a thin-film SOI layer, to prevent a parasitic resistance increase in source / drain regions. To realize an elevated layer to be formed on the source / drain region without using a lithography process and without a fear of a short circuit. Element-isolation insulating films 7, which are taller than a semiconductor layer 3, are formed surrounding the island-shaped semiconductor layer (SOI layer) 3, while gate electrodes 5a, 8a which are taller than the element-isolation insulating films 7 are formed on the semiconductor layer 3. A polycrystalline silicon film 11 is deposited on the whole surface. elevated layers 11a, 11b which are shorter than the element-isolation insulating film 7 are formed on the source / drain regions 3a, 3b by chemical-mechanical polishing and etching back. Silicide layers 13a to 13c are formed on the gate electrode and on the elevated layers. An interlayer insulating film 14 is formed, and a metal electrode 16 is formed.

Owner:NEC CORP

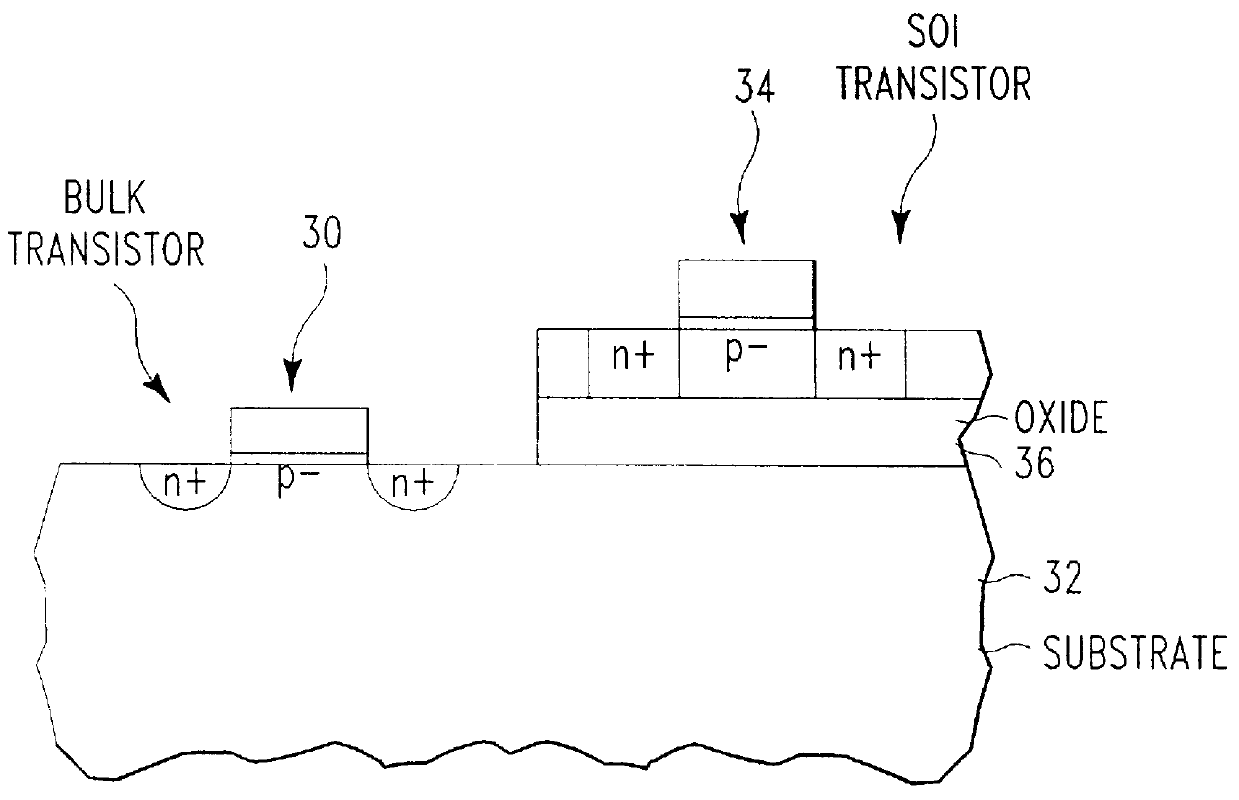

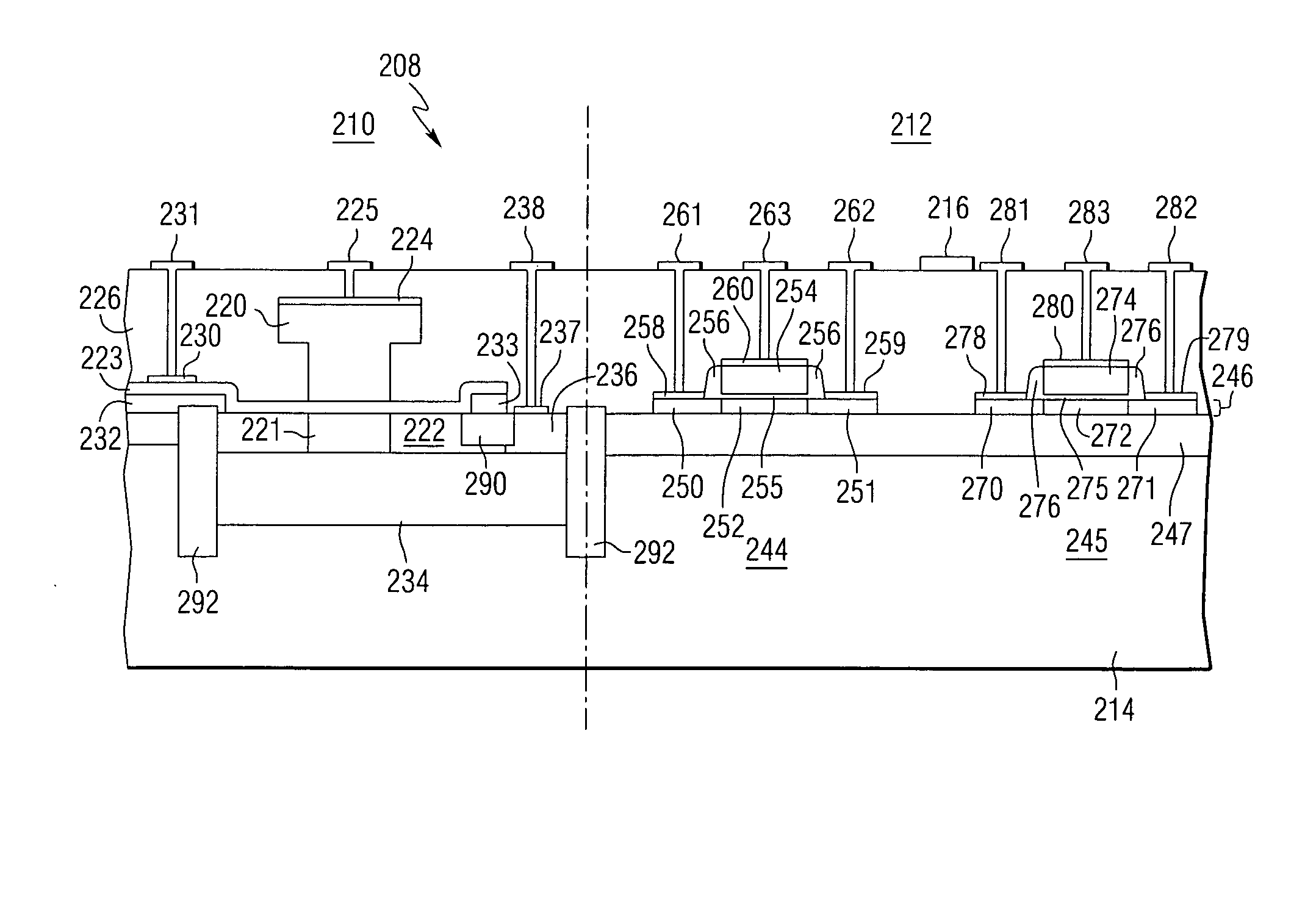

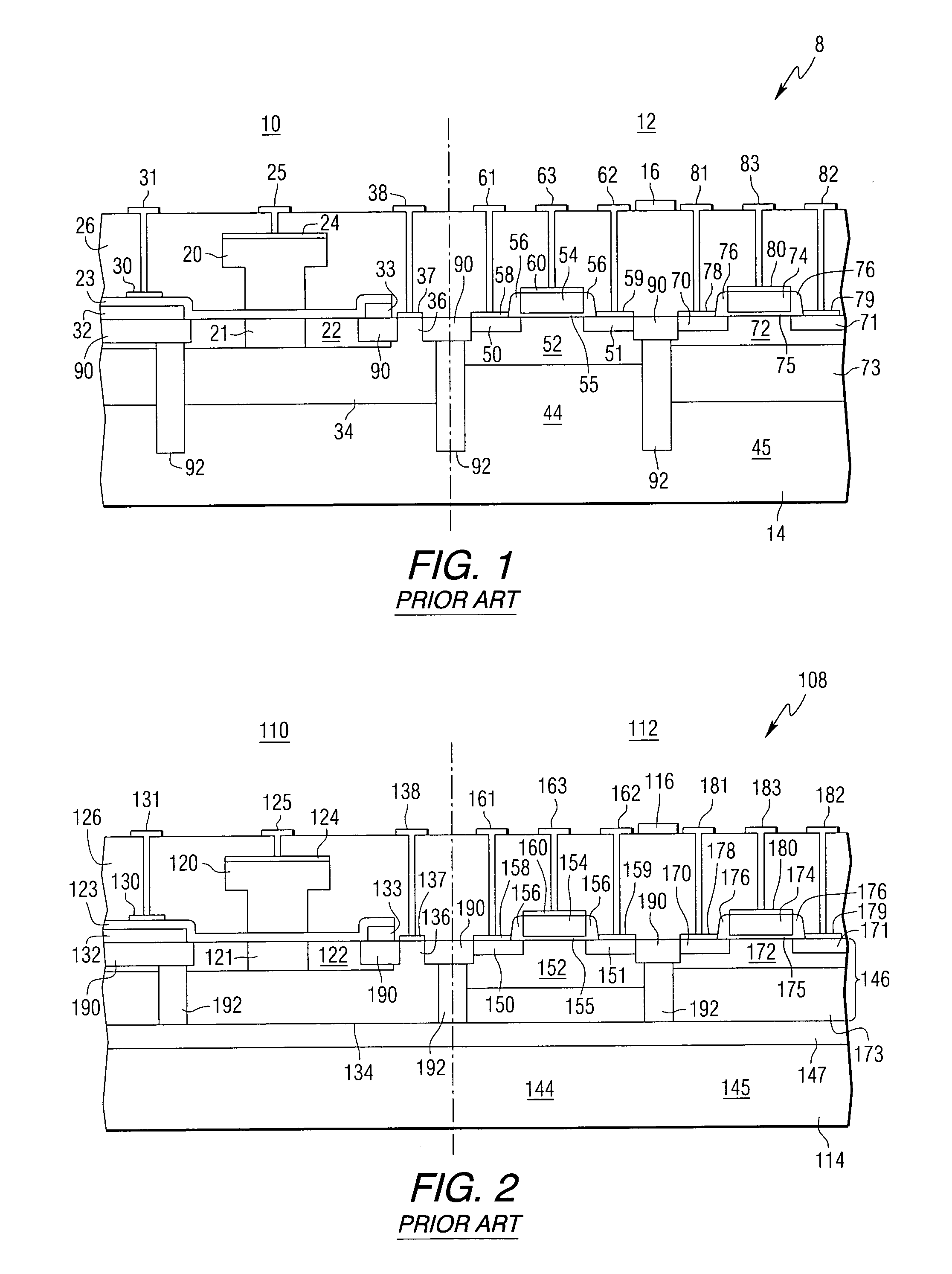

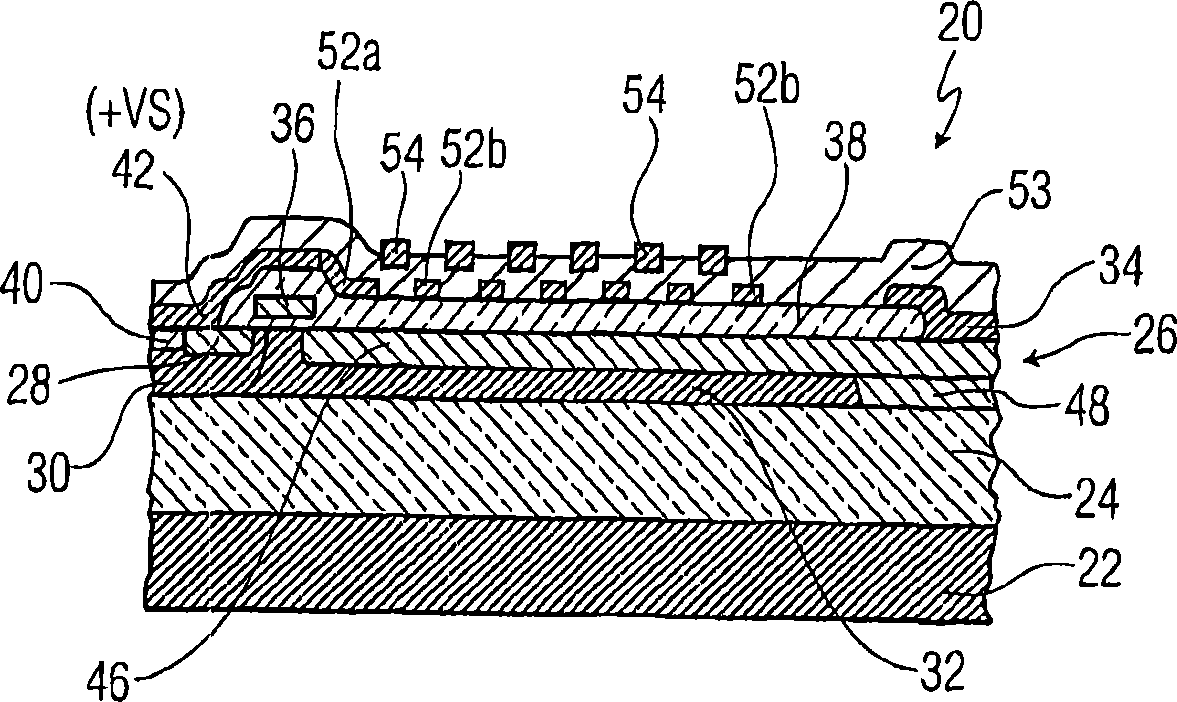

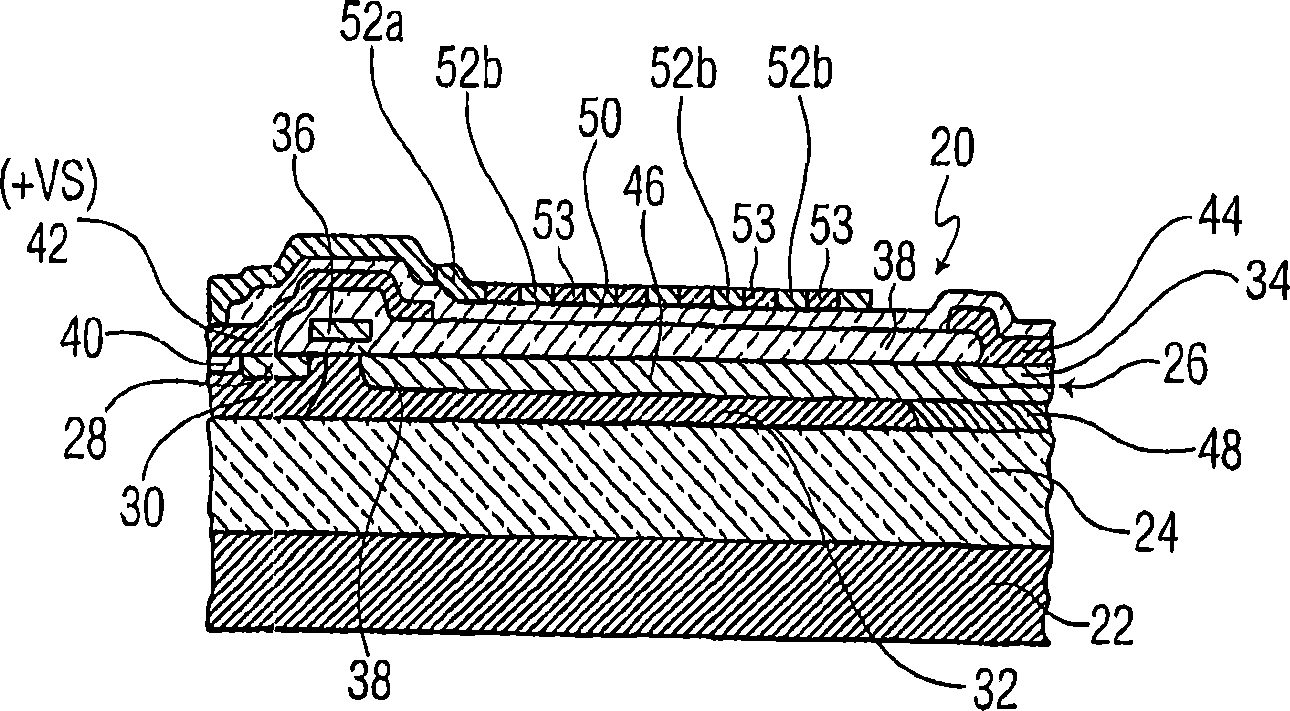

Bipolar/thin film SOI CMOS structure and method of making same

A semiconductor wafer structure which includes at least one bipolar transistor defined in the semiconductor wafer structure as well as at least one CMOS transistor device also defined in the semiconductor wafer structure. The CMOS transistor device is comprised of a thin film of semiconductor on an insulating layer with each transistor of the CMOS transistor device being defined in the thin film. The bipolar transistor has a plurality of semiconductor layers of predetermined conductivities, without any of the semiconductor layers of the bipolar transistor extending into the area occupied by the CMOS transistor device. A method of fabricating the structure is also disclosed.

Owner:NORTHROP GRUMAN CORP

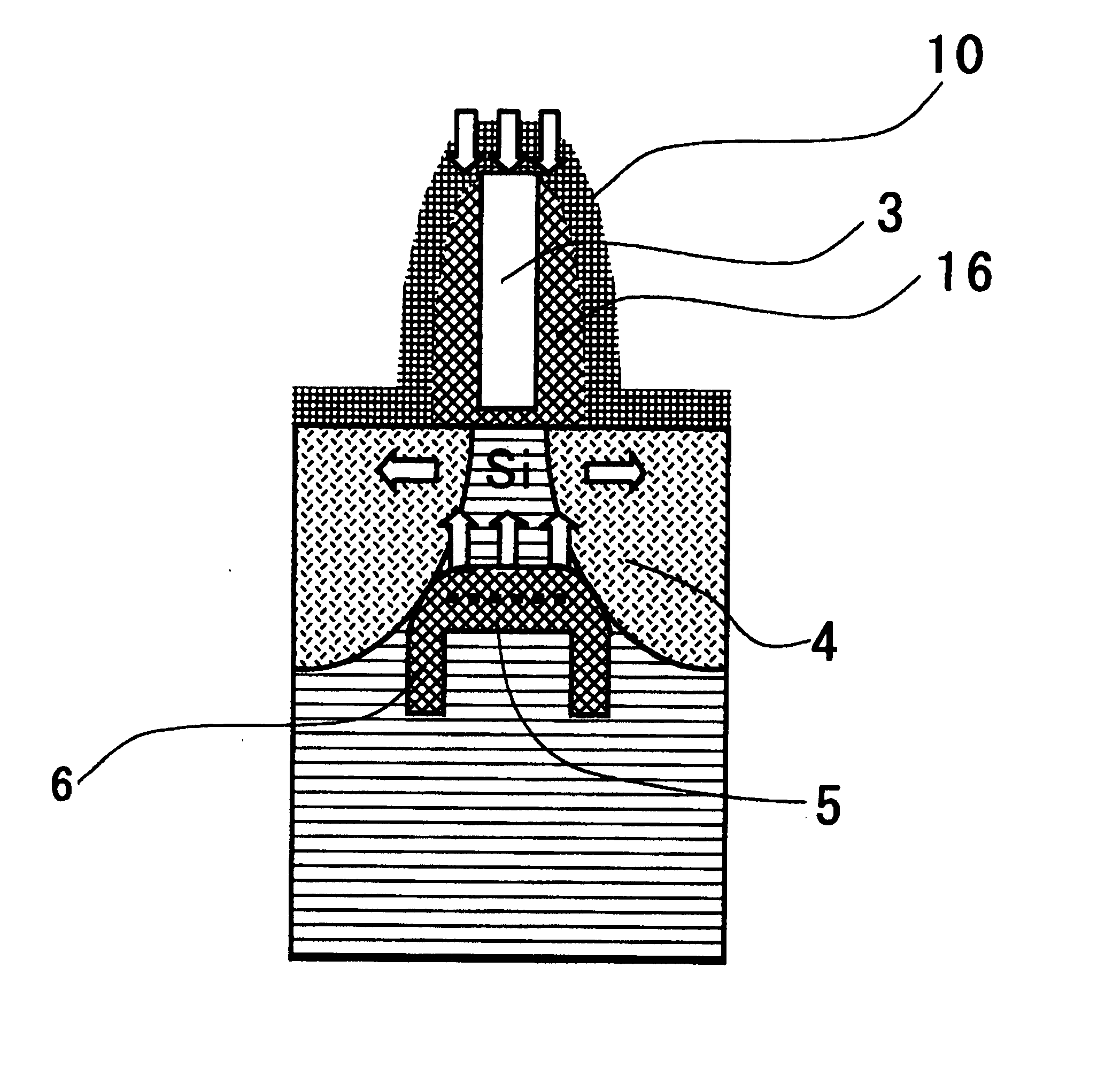

Method of manufacturing semiconductor device for evaluation capable of evaluating crystal defect using in-line test by avoiding using preferential etching process

InactiveUS6673640B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSilicon oxideCrystallographic defect

In order to obtain a method of evaluating a crystal defect which allows crystal defects generated in a thin film SOI layer or a thin film surface layer to be evaluated using an in-line test, an SOI layer 3 has silicide regions 8 formed in the evaluation region consequently upon generation of crystal defects generated in the SOI layer 3. The silicide regions 8 are regions silicided as a result of the crystal defects having gettered metals which are contained in a transition layer 10 and diffuse into the SOI layer 3 upon a heat treatment. A laser beam is irradiated to the evaluation region via the transition layer 10 and the silicon oxide film 6. By monitoring a current flowing between first and second probes using an ampere meter while scanning the evaluation region with a laser beam, it is possible to evaluate the crystal defects in the evaluation region.

Owner:RENESAS TECH CORP

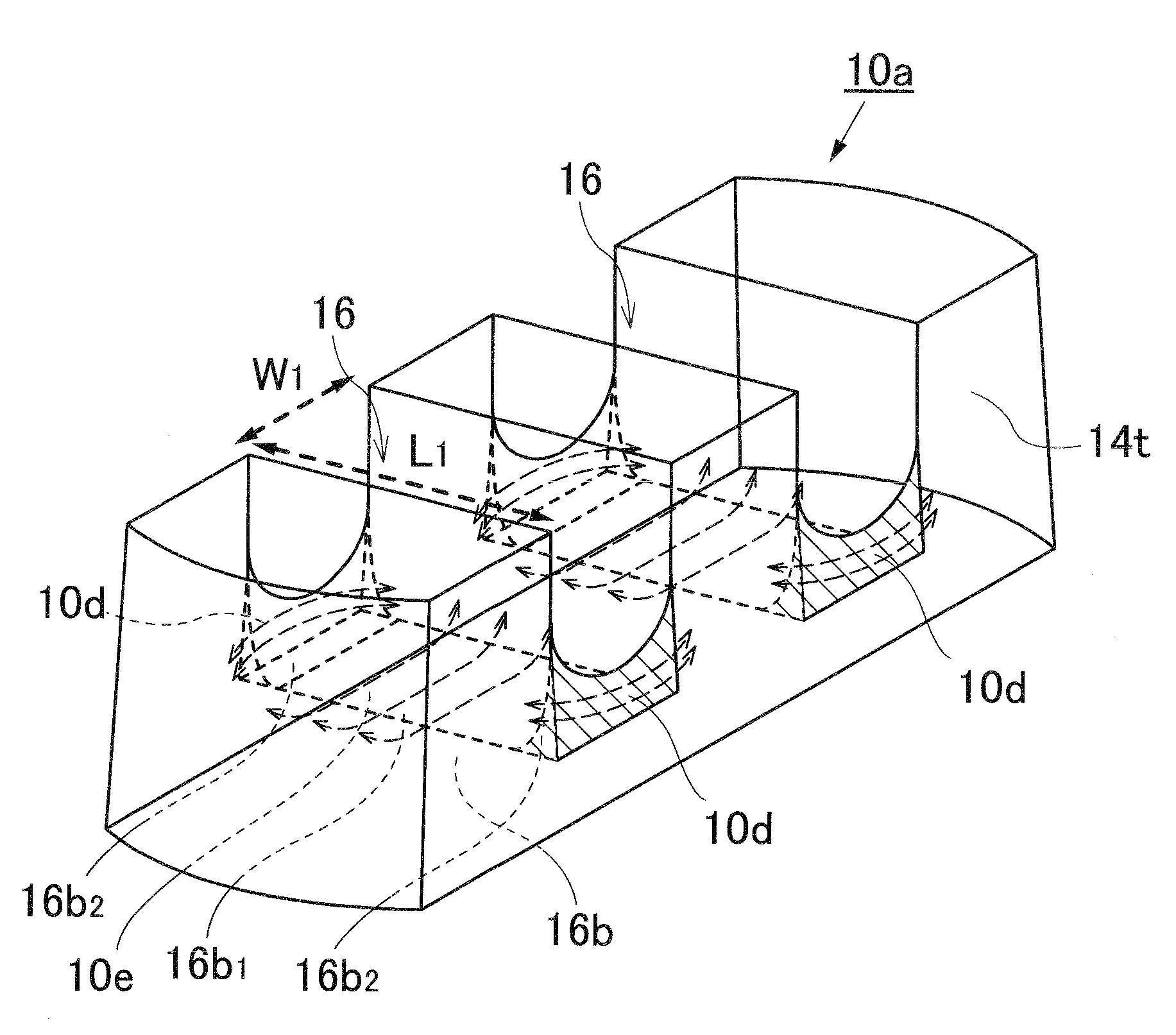

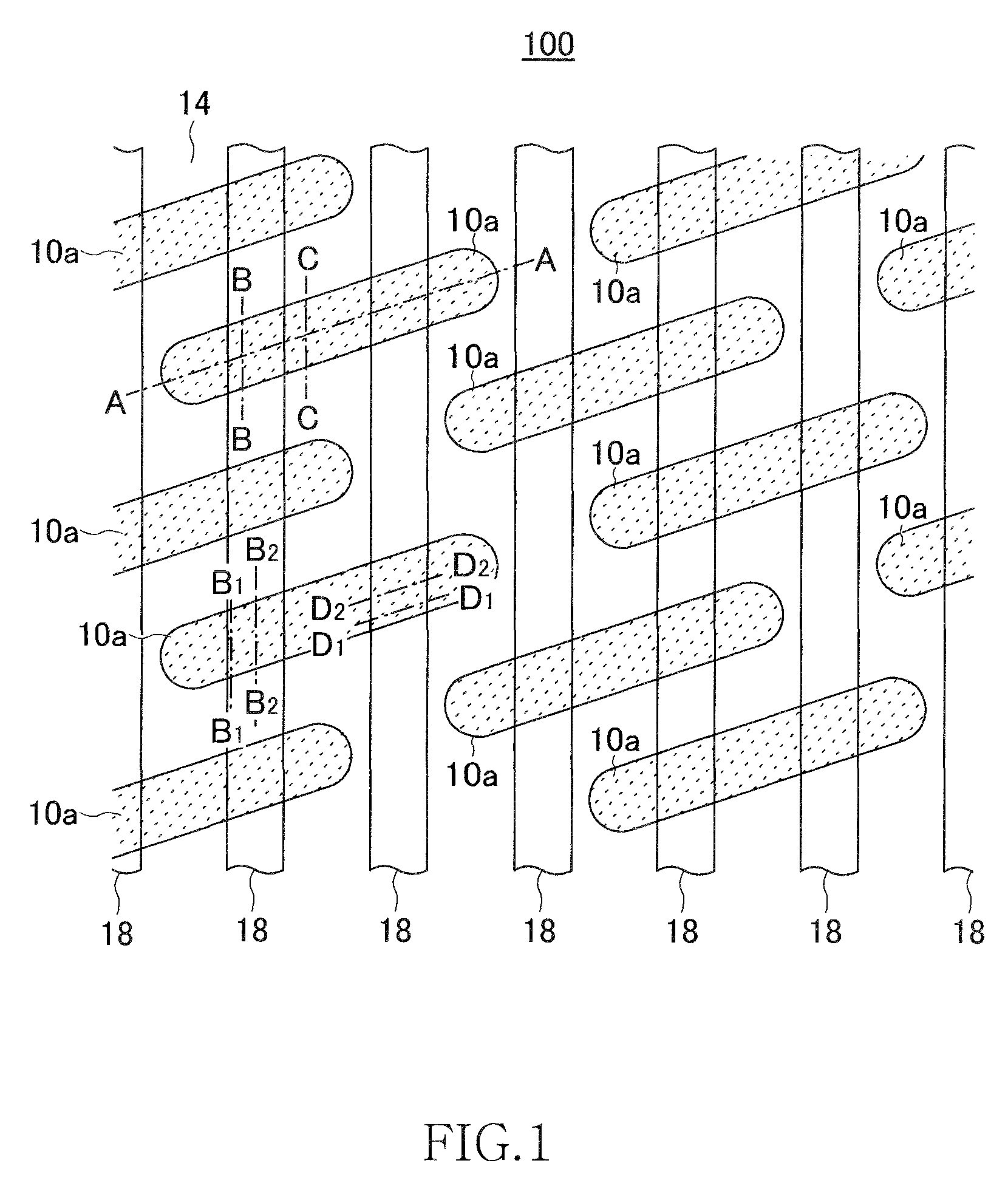

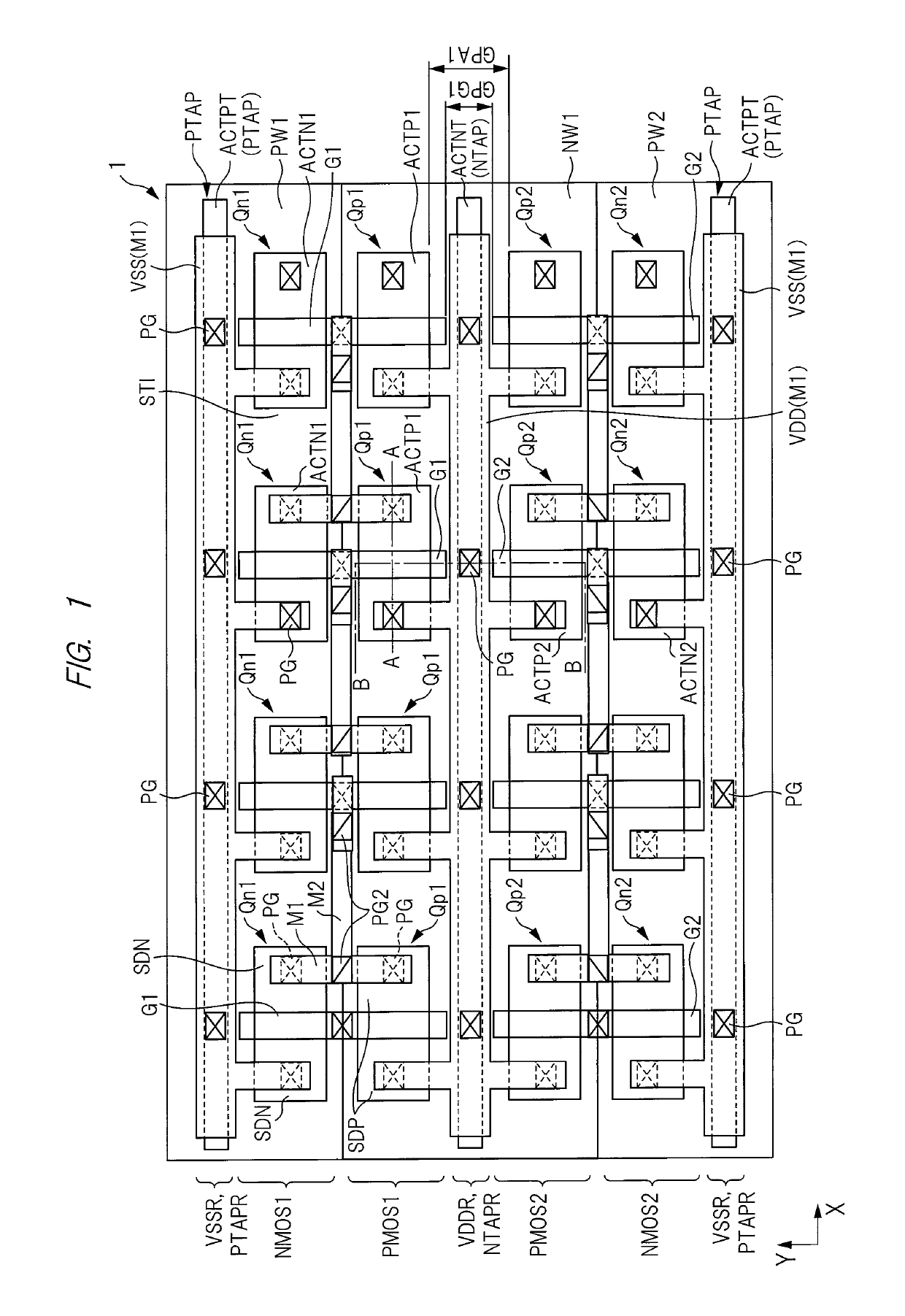

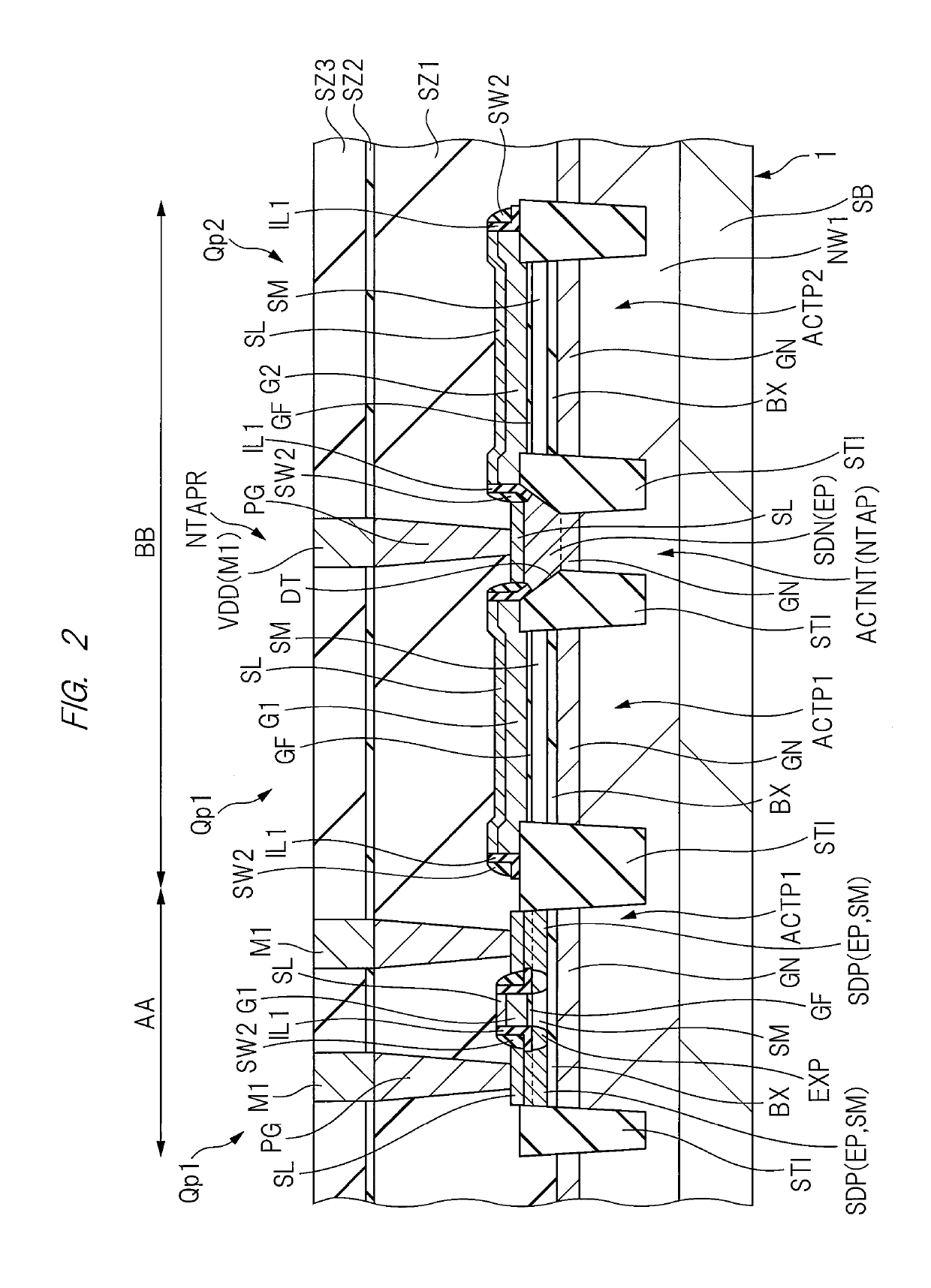

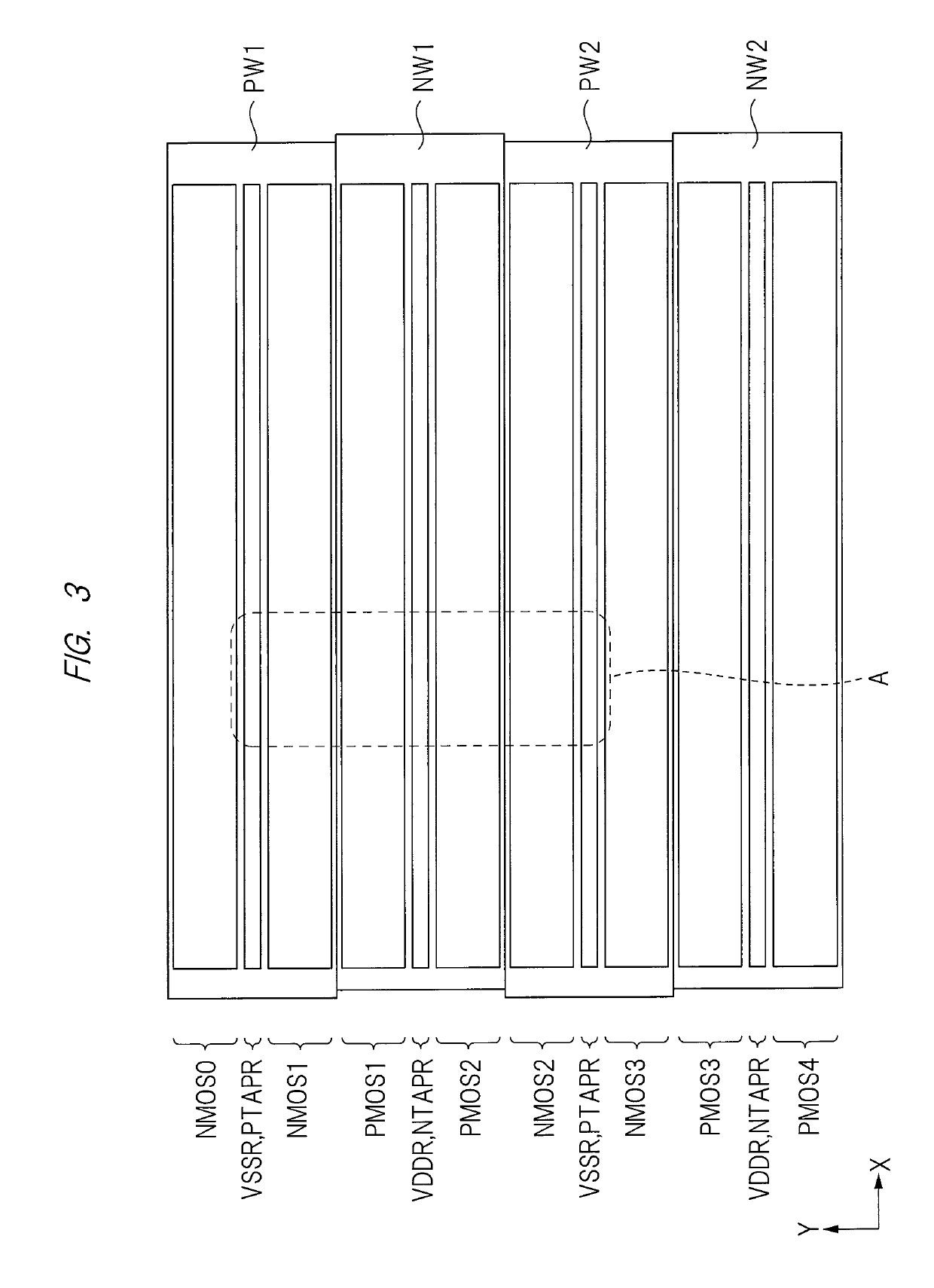

Semiconductor device, manufacturing method thereof, and data processing system

InactiveUS20090101971A1Thin structureImprove featuresSolid-state devicesSemiconductor/solid-state device manufacturingData processing systemEngineering

A bottom of a gate trench has a first bottom relatively far from an STI and a second bottom relatively near from the STI A portion, in an active region, configuring the second bottom of the gate trench configures a side-wall channel region, and has a thin-film SOI structure sandwiched between the gate electrode and the STI. On the other hand, a portion configuring the first bottom of the gate trench functions as a sub-channel region. A curvature radius of the second bottom is larger than a curvature radius of the first bottom. In an approximate center in a width direction of the gate trench, a bottom of a trench is approximately flat, and on the other hand, in ends of the width direction, a nearly whole bottom of the trench is curved.

Owner:LONGITUDE LICENSING LTD

Method of manufacturing semiconductor device for evaluation capable of evaluating crystal defect using in-line test by avoiding using preferential etching process

InactiveUS20030113941A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSilicon oxideCrystallographic defect

In order to obtain a method of evaluating a crystal defect which allows crystal defects generated in a thin film SOI layer or a thin film surface layer to be evaluated using an in-line test, an SOI layer 3 has silicide regions 8 formed in the evaluation region consequently upon generation of crystal defects generated in the SOI layer 3. The silicide regions 8 are regions silicided as a result of the crystal defects having gettered metals which are contained in a transition layer 10 and diffuse into the SOI layer 3 upon a heat treatment. A laser beam is irradiated to the evaluation region via the transition layer 10 and the silicon oxide film 6. By monitoring a current flowing between first and second probes using an ampere meter while scanning the evaluation region with a laser beam, it is possible to evaluate the crystal defects in the evaluation region.

Owner:RENESAS TECH CORP

Biaxially-oriented polyester film with high compound fastness for TTR (thermal transfer ribbon) and preparation method of biaxially-oriented polyester film

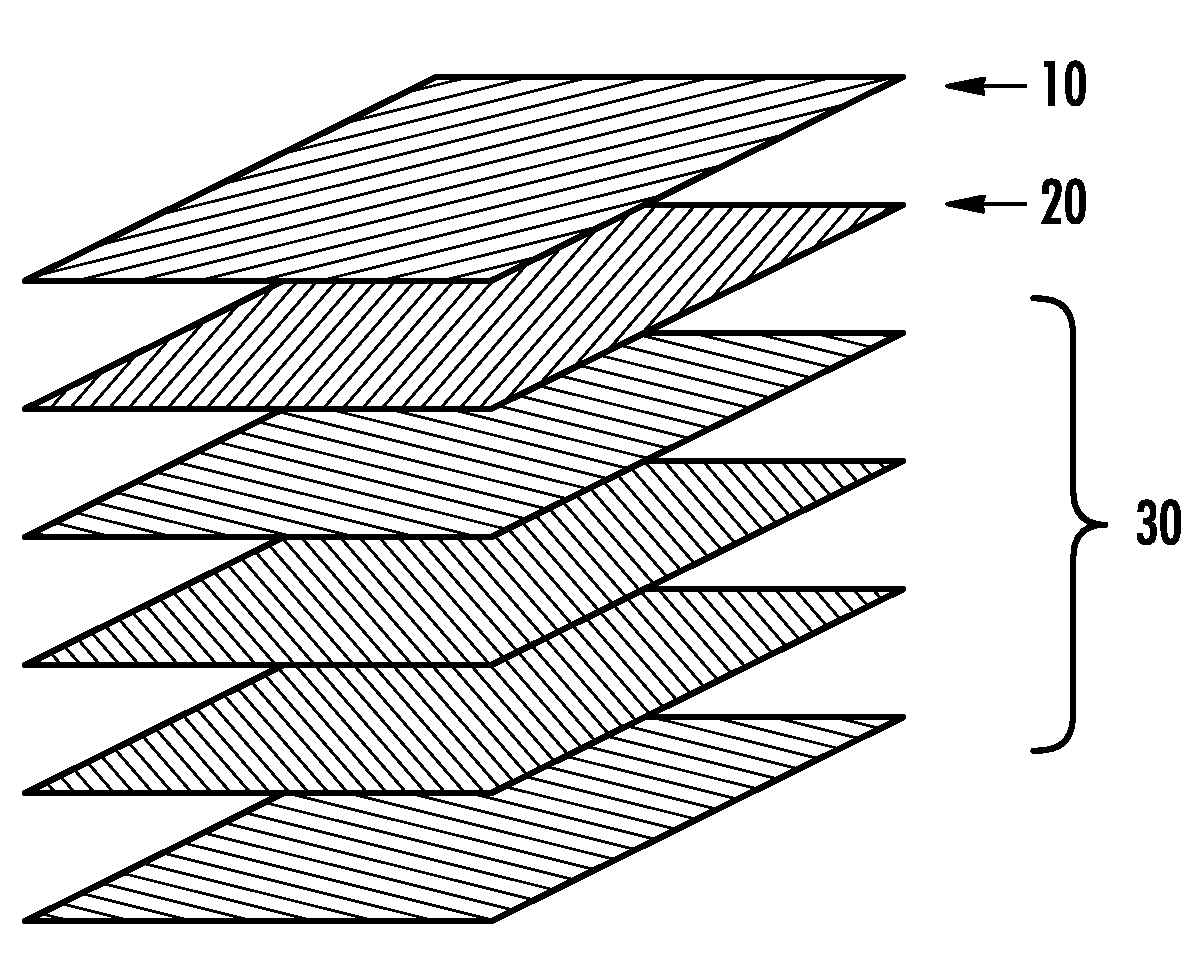

InactiveCN109159514AImprove adhesionFirmly connectedInk ribbonsSynthetic resin layered productsPolyesterSurface layer

The invention discloses a biaxially-oriented polyester film with high compound fastness for a TTR (thermal transfer ribbon) and a preparation method of the biaxially-oriented polyester film. The biaxially-oriented polyester film comprises an upper surface layer, a core layer and a lower surface layer in sequence, wherein each of the upper surface layer and the lower surface layer is prepared fromPET masterbatches and PET chips in a mass ratio being (65-75):(25-35); the PET masterbatches are prepared through steps as follows: a modified inorganic nanoparticle solution is added to a PET reactant and subjected to esterification, polycondensation and drying together with the PET reactant, and content of inorganic nanoparticles is 40000-60000 ppm. The biaxially-oriented polyester film with high compound fastness for the TTR is high in ink compound fastness, excellent in smoothness and good in wear resistance and heat resistance and meets high-quality printing requirements for elaboration,clearness and the like.

Owner:ANHUI GUOFENG PLASTIC

Method of manufacturing semiconductor device having thin film SOI structure

InactiveUS20050019991A1Prevented from reachingTransistorSemiconductor/solid-state device detailsSoi substrateThin film soi

A method of manufacturing a semiconductor device includes the steps of, (1) preparing an SOI substrate, (2) forming a metal layer on the SOI substrate, (3) performing a first anneal treatment to the metal layer at a relatively low temperature in order to transform the metal layer to a first silicide layer, (4) forming an insulating layer on the first silicide layer, and (5) forming a contact hole, which reaches the first silicide layer, in the insulating layer; and (6) performing a second anneal treatment to the silicide layer at a relatively high temperature in order to transform the first silicide layer to a second silicide layer.

Owner:LAPIS SEMICON CO LTD

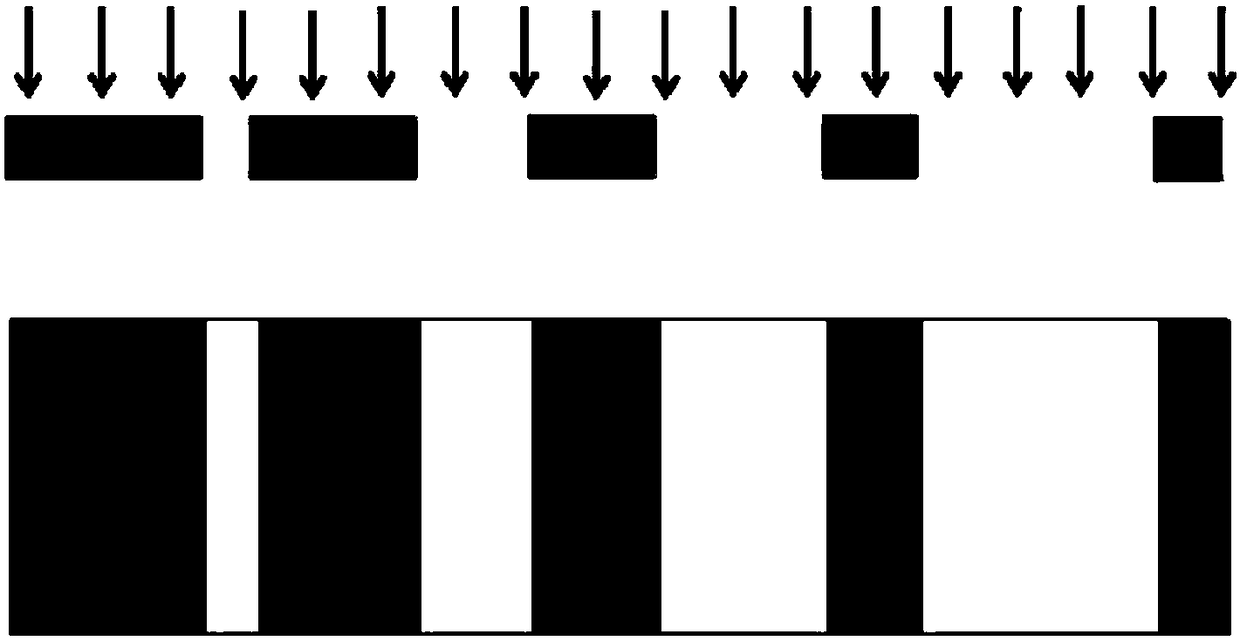

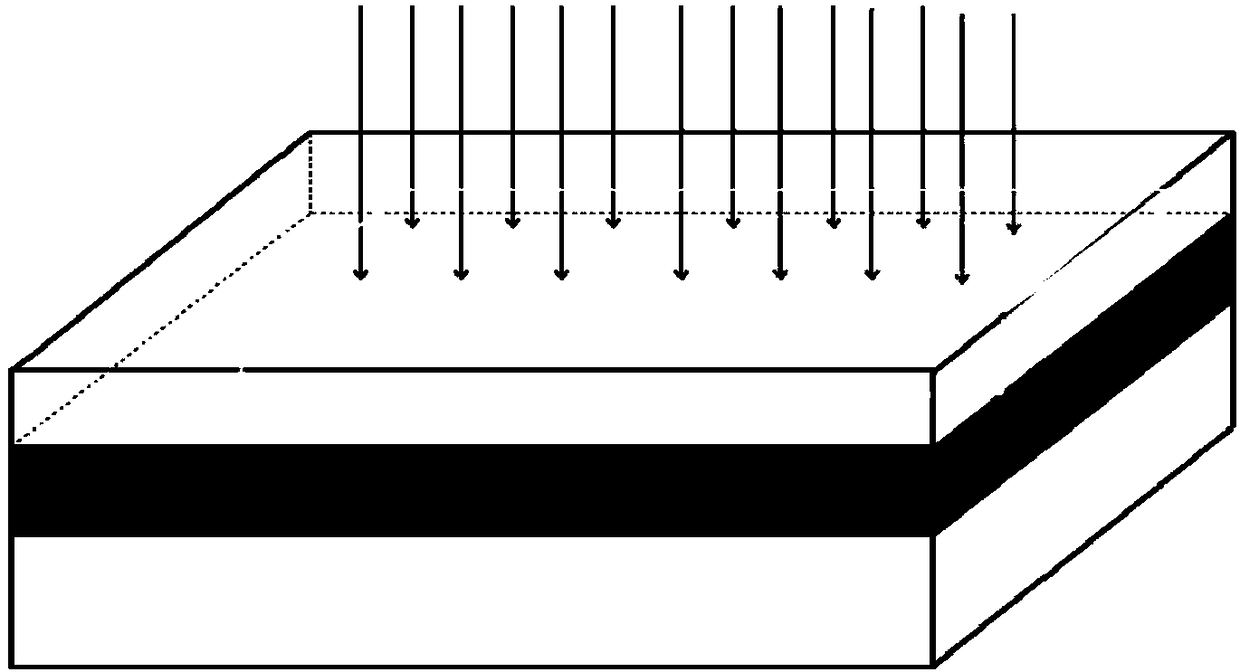

Lateral thin-film soi device having a field plate with isolated metallic regions

In a lateral thin-film Silicon-On-Insulator (SOI) device, a field plate is provided to extend substantially over a lateral drift region to protect the device from package and surface charge effects. In particular, the field plate comprises a layer of plural metallic regions which are isolated laterally from one another by spacing so as to assume a lateral electric field profile which is established by a volume doping gradient in the silicon drift region.

Owner:NXP BV

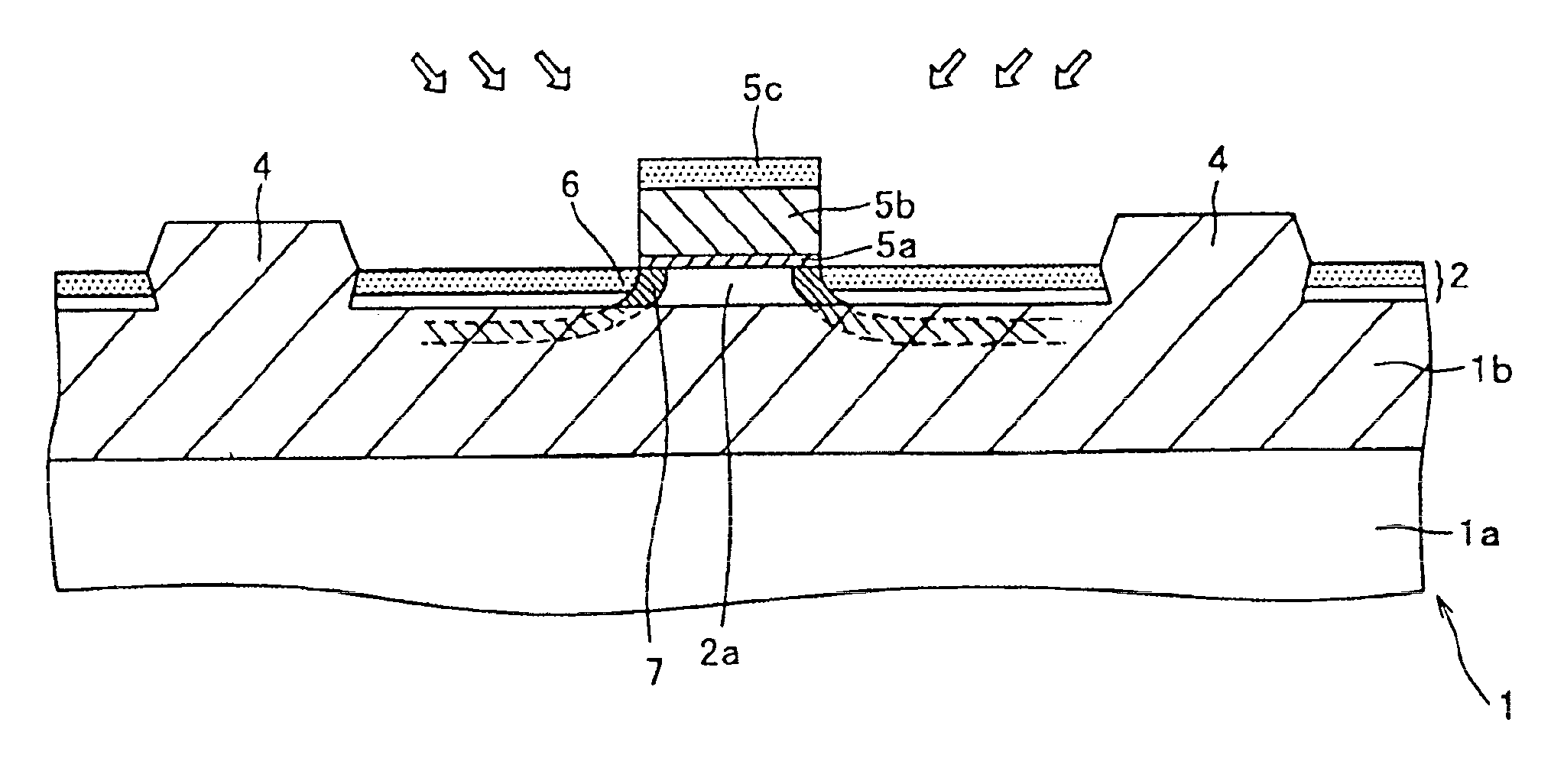

MOS field effect transistor and manufacture method therefor

InactiveUS20060157784A1Easy to operateReduce power consumptionSolid-state devicesSemiconductor devicesField-effect transistorGate oxide

A method of manufacturing an MOS field effect transistor, which achieves a faster operation and lower power consumption by using a thin film SOI structure, is provided. The method of manufacturing an MOS field effect transistor to be formed on a semiconductor substrate having a channel layer on a buried oxide film, comprises the steps of forming: a gate electrode on the semiconductor substrate via a gate oxide film; forming a first sidewall which covers a side wall of the gate electrode; forming a box oxide film by etching the buried oxide film; and forming a second sidewall which covers a side wall of the box oxide film in such a way that the second sidewall extends downward along the side wall of the box oxide film.

Owner:FUJITSU SEMICON LTD

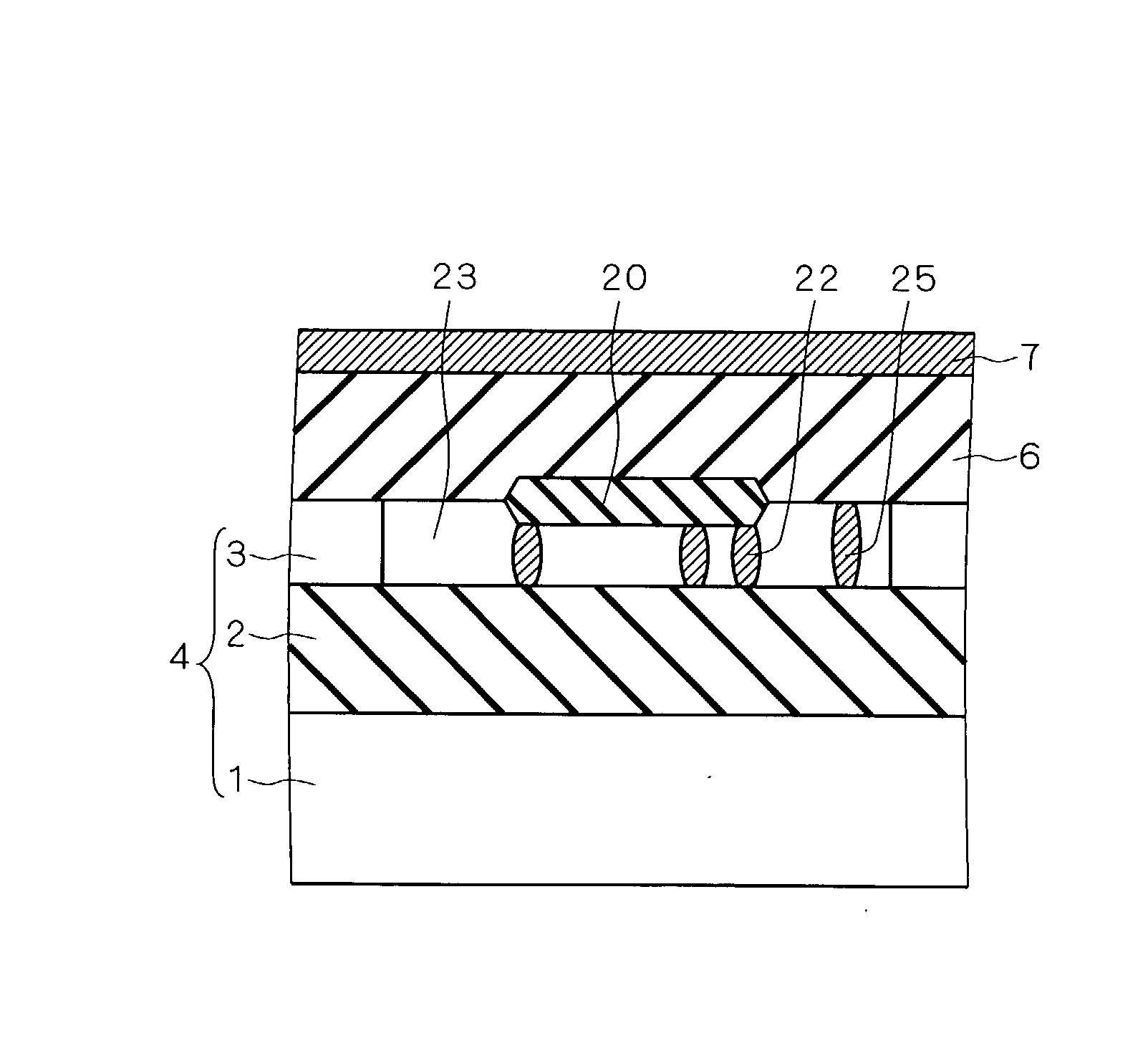

CMOS pixels comprising epitaxial layers for light-sensing and light emission

ActiveUS8963169B2Improves intrinsic and extrinsic efficiencySolid-state devicesDiodeLight sensingPhotonics

Photonic devices monolithically integrated with CMOS are disclosed, including sub-100 nm CMOS, with active layers comprising acceleration regions, light emission and absorption layers, and optional energy filtering regions. Light emission or absorption is controlled by an applied voltage to deposited films on a pre-defined CMOS active area of a substrate, such as bulk Si, bulk Ge, Thick-Film SOI, Thin-Film SOI, Thin-Film GOI.

Owner:QUANTUM SEMICON

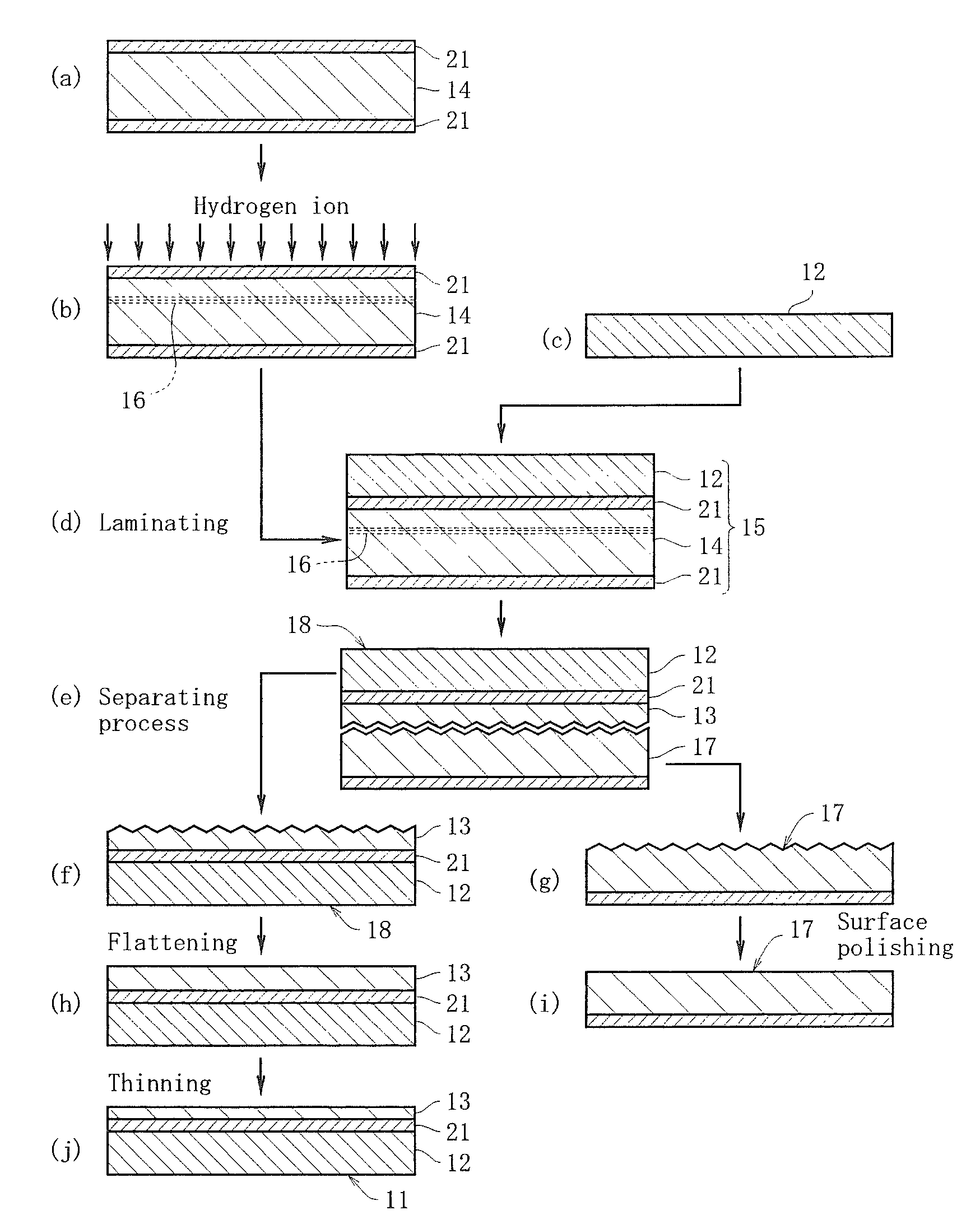

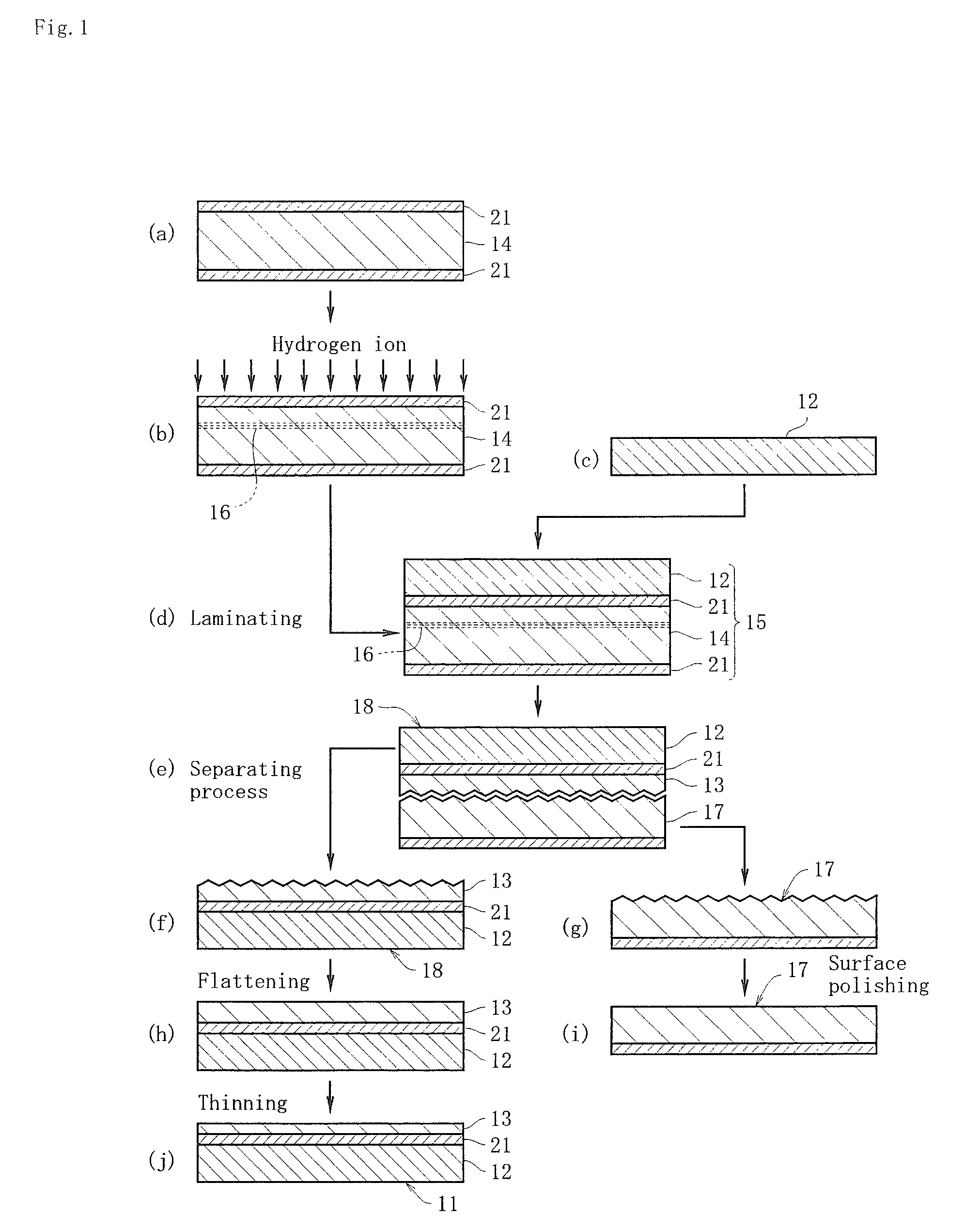

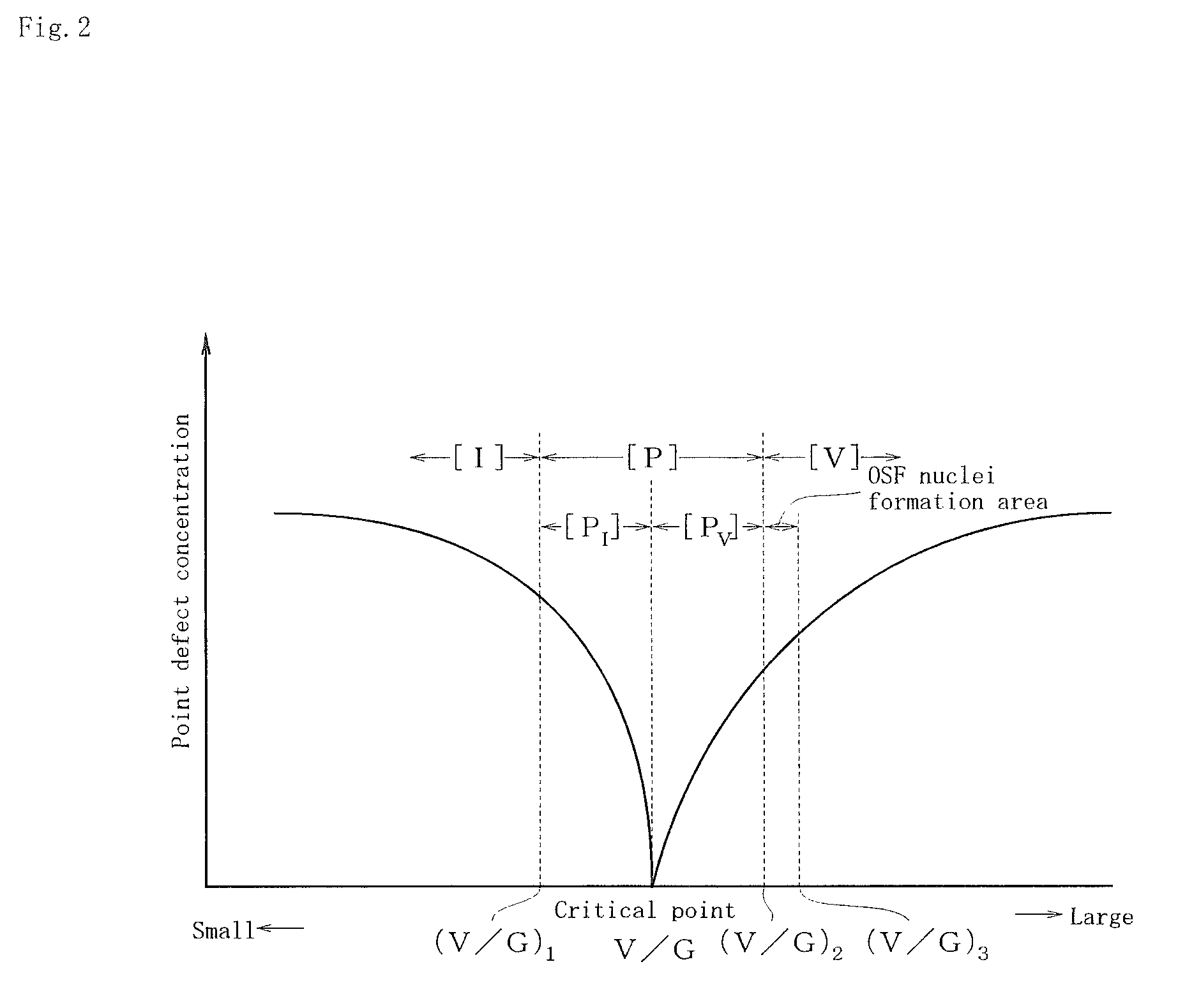

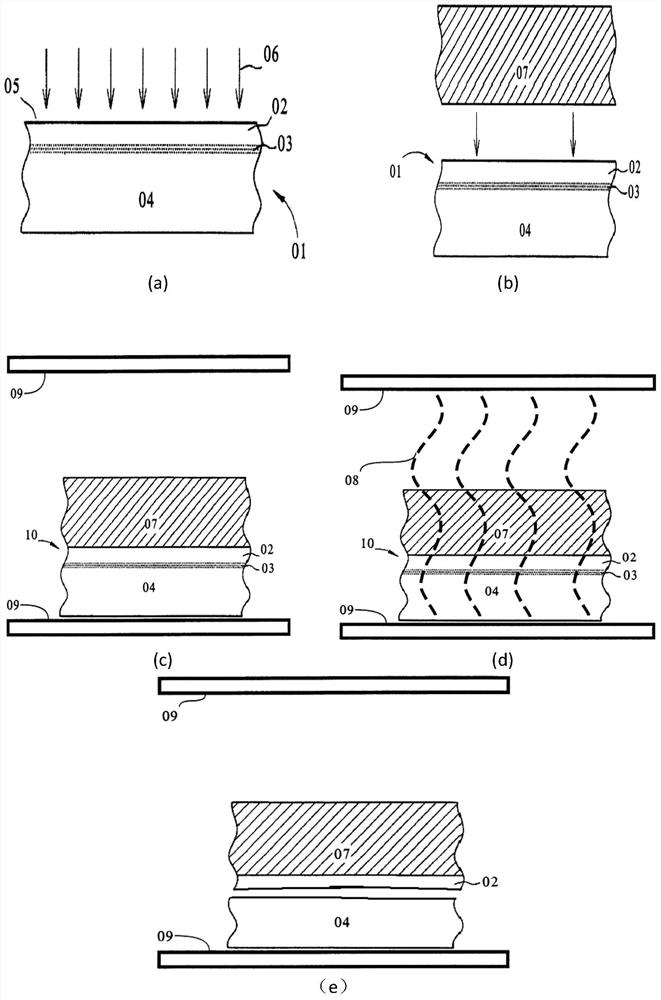

Process for producing SOI substrate and process for regeneration of layer transferred wafer in the production

InactiveUS7790573B2Blocking may occurEasy to getPolycrystalline material growthAfter-treatment detailsHydrogenWafering

A process for producing an SOI substrate includes the steps of forming an oxide film on at least the front surface of a first silicon substrate, implanting hydrogen ion from the surface of the first silicon substrate and thereby forming an ion implantation area in the inside of the first silicon substrate, laminating a second silicon substrate onto the first silicon substrate via the oxide film and thereby forming a laminated body of the first silicon substrate and the second silicon substrate bonded with each other, and heating the laminated body at a predetermined temperature and thereby separating the first silicon substrate at the ion implantation area and thereby obtaining an SOI substrate wherein a thin film SOI layer is formed on the second silicon substrate via the oxide film. The first silicon substrate is formed by slicing an ingot free of an agglomerate of vacancy type point defects and an agglomerate of interstitial silicon type point defects grown by a CZ method in an inorganic atmosphere including hydrogen. The layer transferred wafer separated from the SOI layer is used again as the first silicon substrate.

Owner:SUMCO CORP

Thin film SOI thick grid oxygen power device with grid field plate

The invention belongs to the semi-conductor power device technical field. A SOI layer of the device is thinner (1to 2um); a grid oxide layer is thick (100 to 800nm); a grid field plate gets across a grid and extends above a drift region. An active expansion region positioned below the thick grid oxide layer and connected with a source region can be also arranged in the body of the device to assure the more effective formation of the whole device. The grid oxide layer of the invention is thicker, can bear high grid-source voltage and meet the need of a level displacement circuit; the SIO layer is thinner, can decrease the parasitic effect of the device and reduce consumption; through adding the grid field plate striding over the grid on the surface of the power device, the depletion of the drift region can be increased, the electric field peak value on the silicon surface at the tail end of the grid is decreased, the breakdown characteristic of the device is improved, further more the concentration of the drift region is helped to improve, and the on-state resistance of the device is decreased. The invention has the advantages of low parasitic effect, fast speed, low power consumption, strong radiation-resistant ability and so on, and is compatible with the standard process. By adopting the invention, various high-voltage, high-speed and low conducting loss devices of excellent performance can be produced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

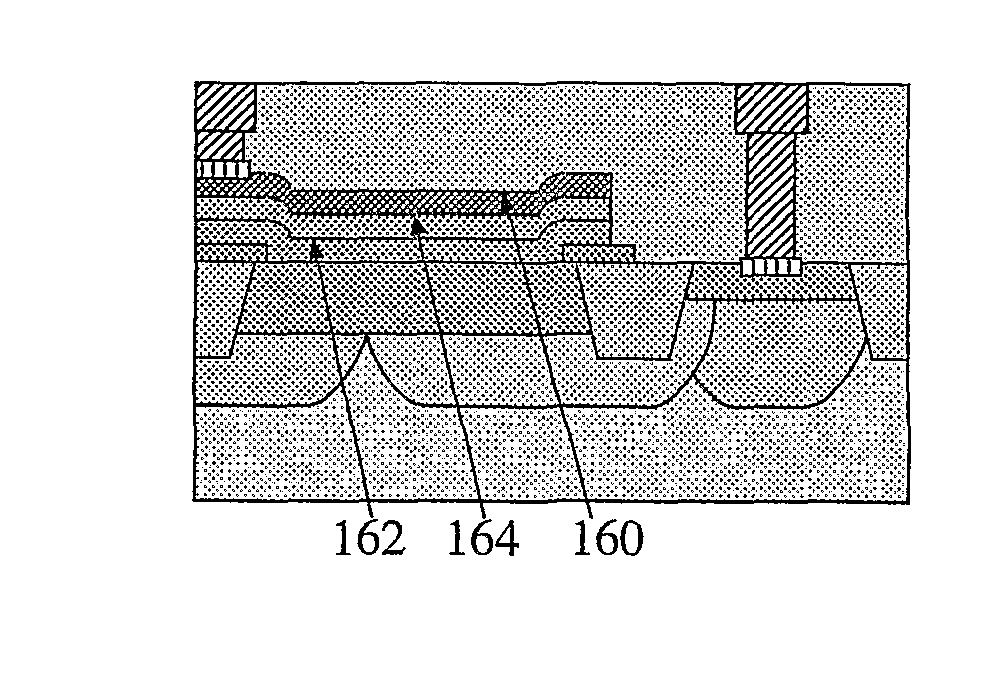

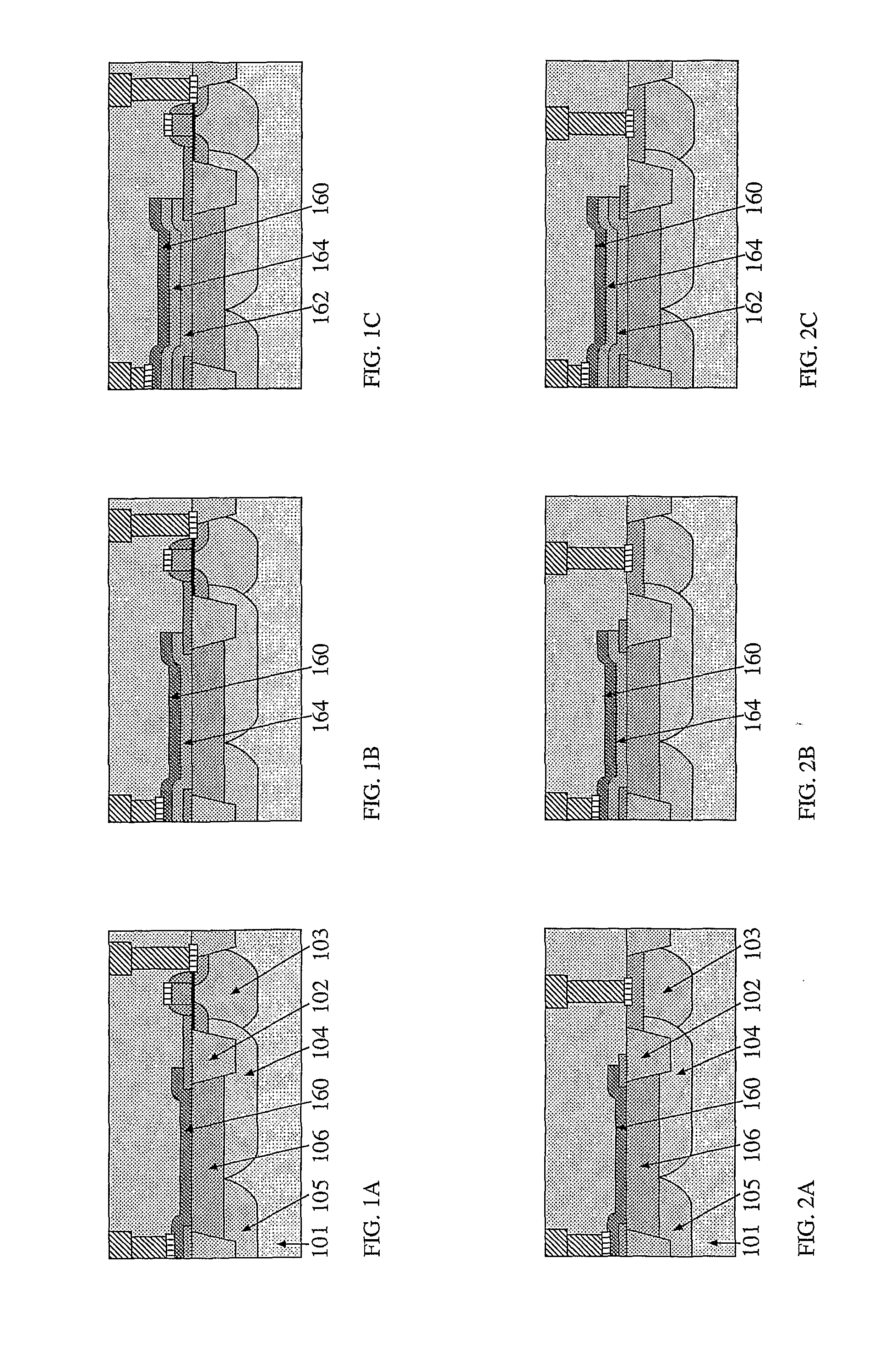

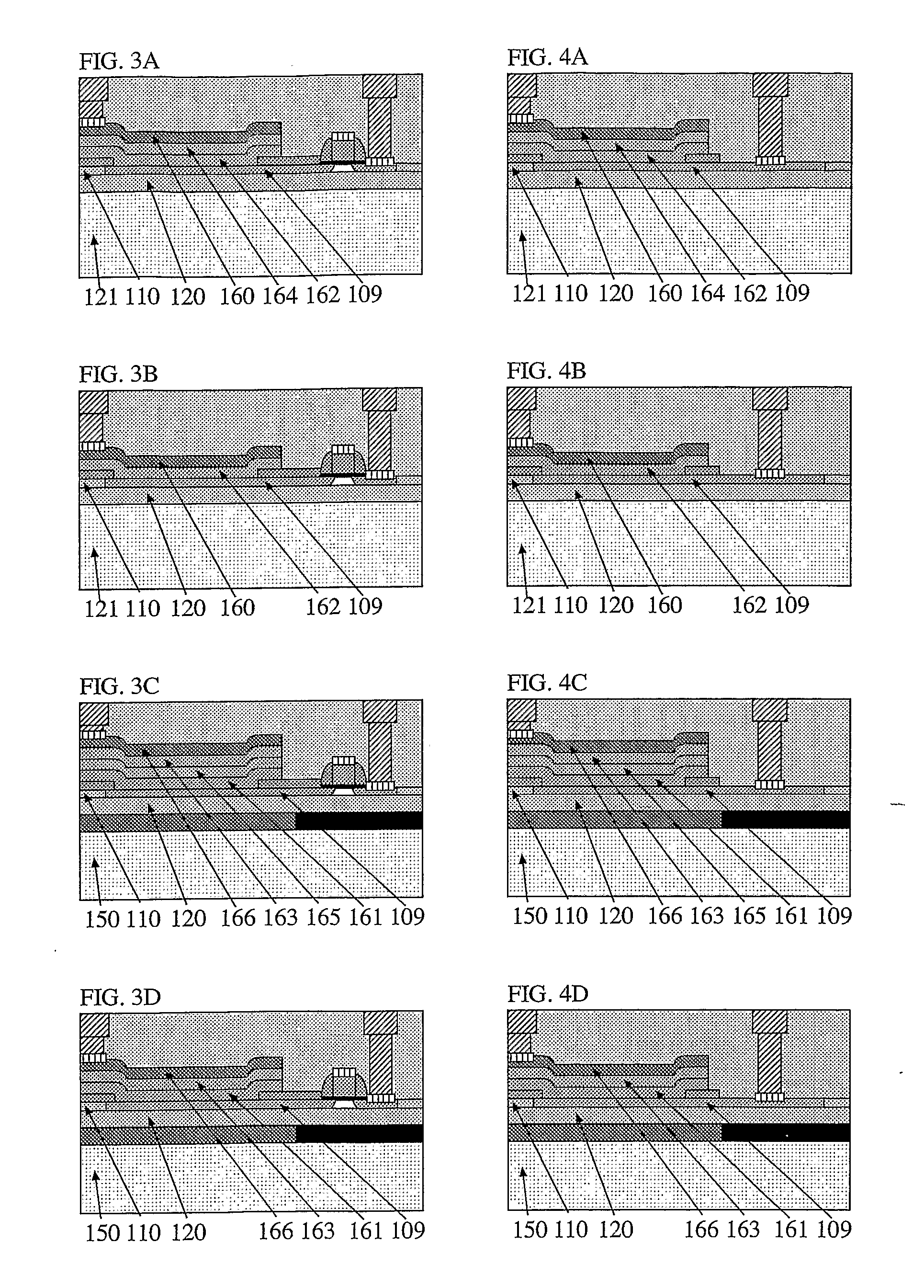

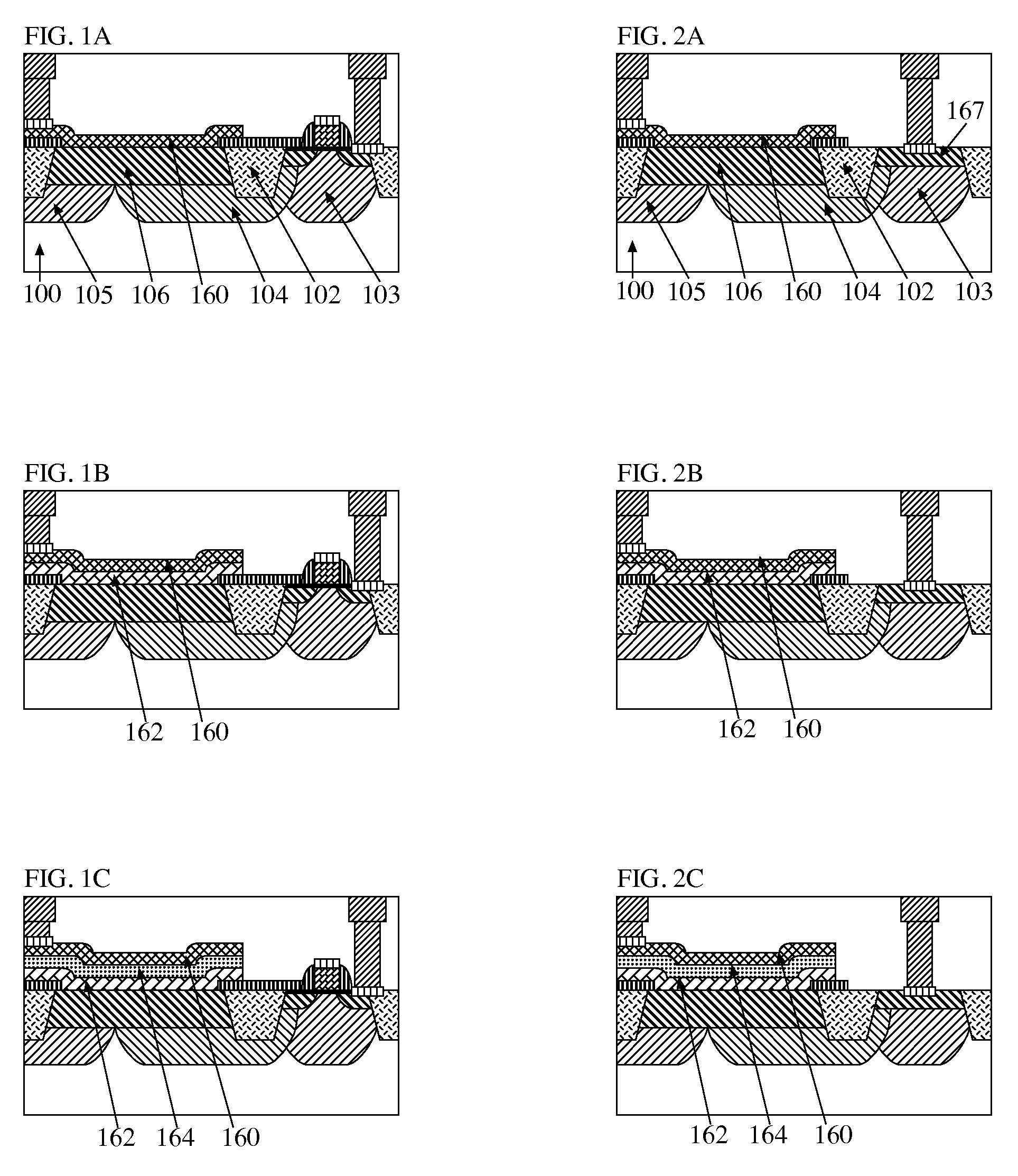

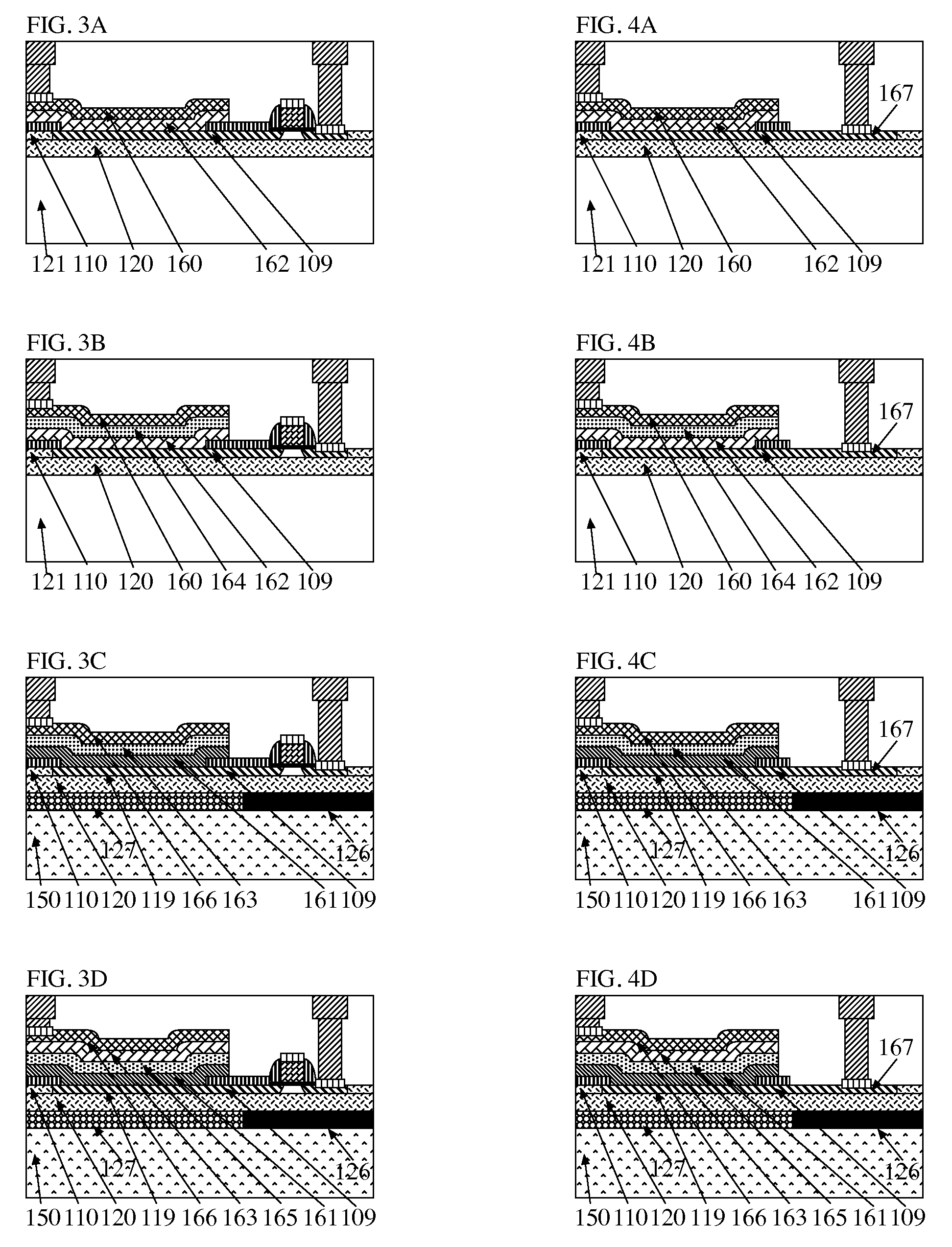

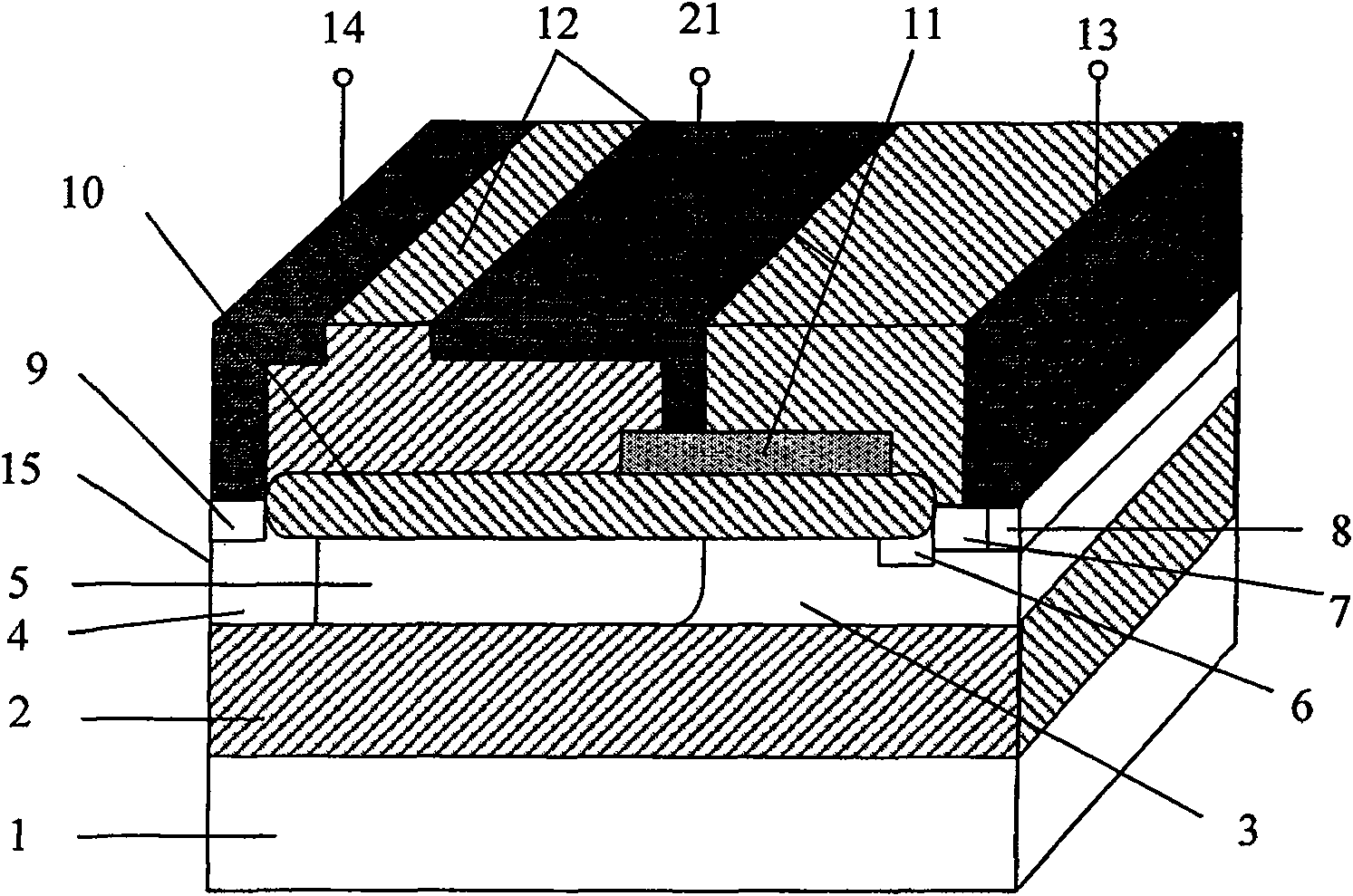

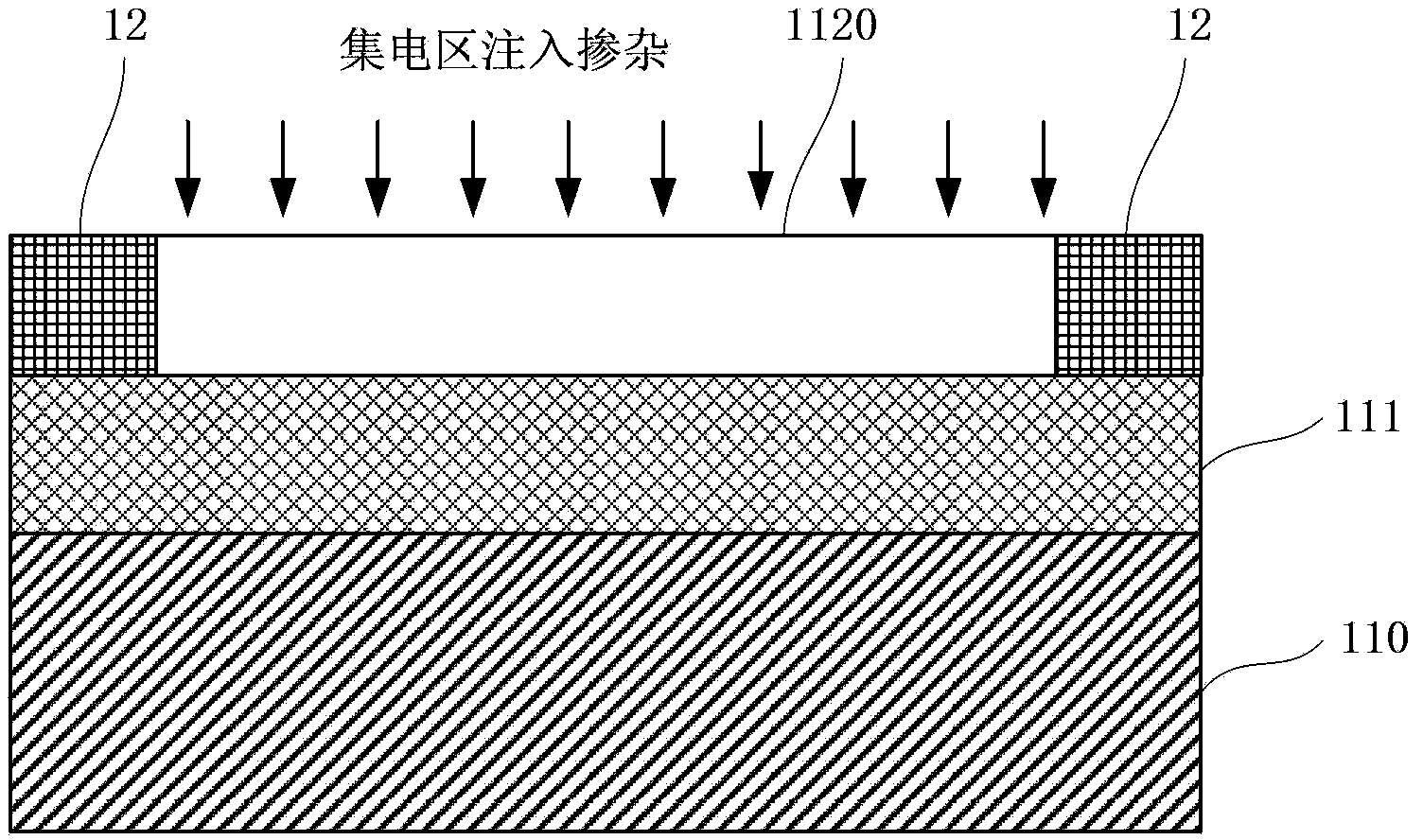

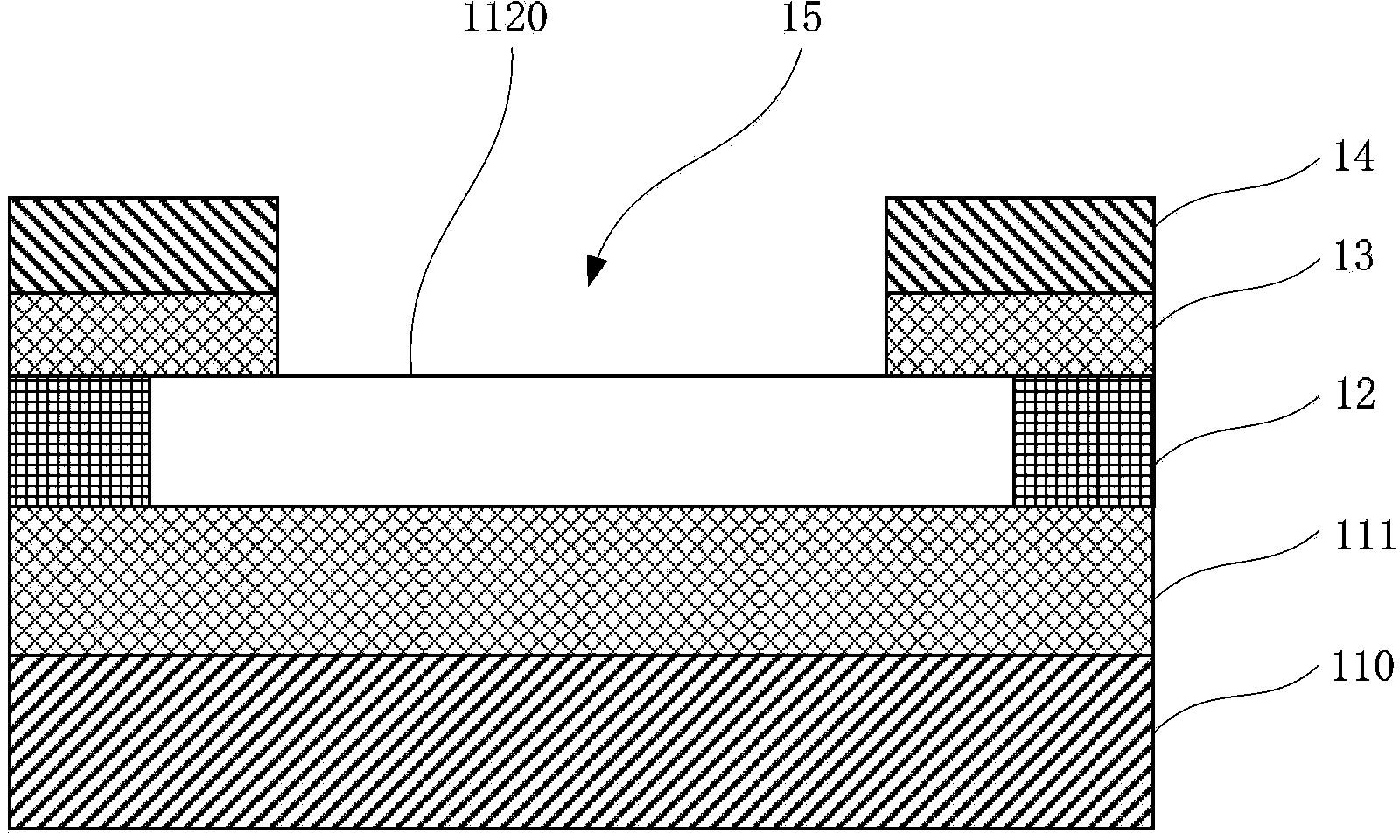

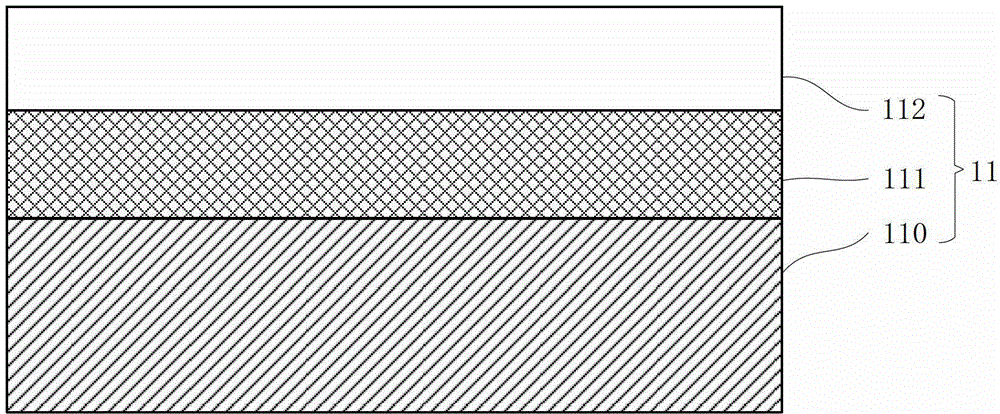

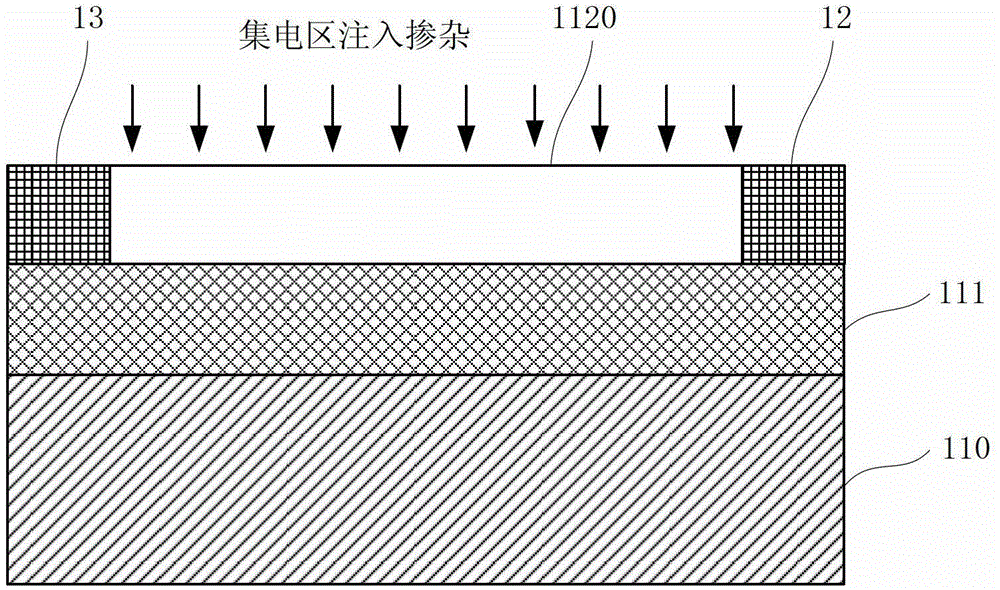

A kind of preparation method of sige-hbt transistor based on soi

InactiveCN102800589BSimple preparation processSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceEngineering

Provided is a method of manufacturing an SOI-based silicon-germanium heterojunction bipolar transistor (SiGe-HBT). In the method, the impurity injected in an outer base region (161) is changed from boron to boron fluoride, and the injection energy and amount are defined in specific ranges, thereby effectively solving the problems of significantly increased collector resistance and an apparently reduced maximum cut-off frequency Ft parameter for SiGe-HBT devices on a thin-film SOI. Also, compared with other methods of increasing an injection amount and a doping concentration in a collector region, the method avoids lowered voltage endurance of devices because of an increased doping concentration in a collector region. In addition, the manufacturing process is simple and is easy to implement.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method of manufacturing semiconductor device having thin film SOI structure

A method of manufacturing a semiconductor device includes the steps of, (1) preparing an SOI substrate, (2) forming a metal layer on the SOI substrate, (3) performing a first anneal treatment to the metal layer at a relatively low temperature in order to transform the metal layer to a first silicide layer, (4) forming an insulating layer on the first silicide layer, and (5) forming a contact hole, which reaches the first silicide layer, in the insulating layer; and (6) performing a second anneal treatment to the silicide layer at a relatively high temperature in order to transform the first silicide layer to a second silicide layer.

Owner:LAPIS SEMICON CO LTD

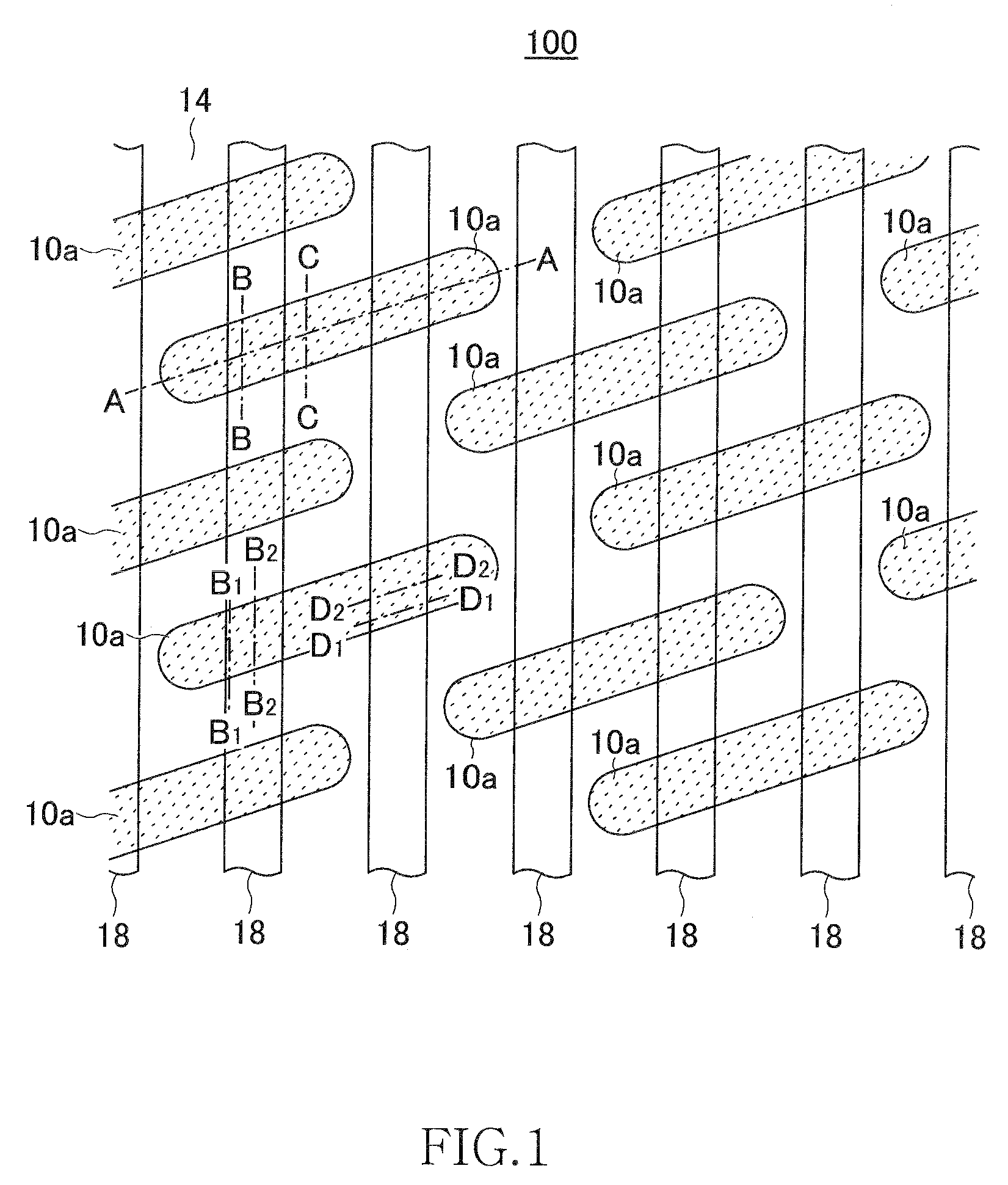

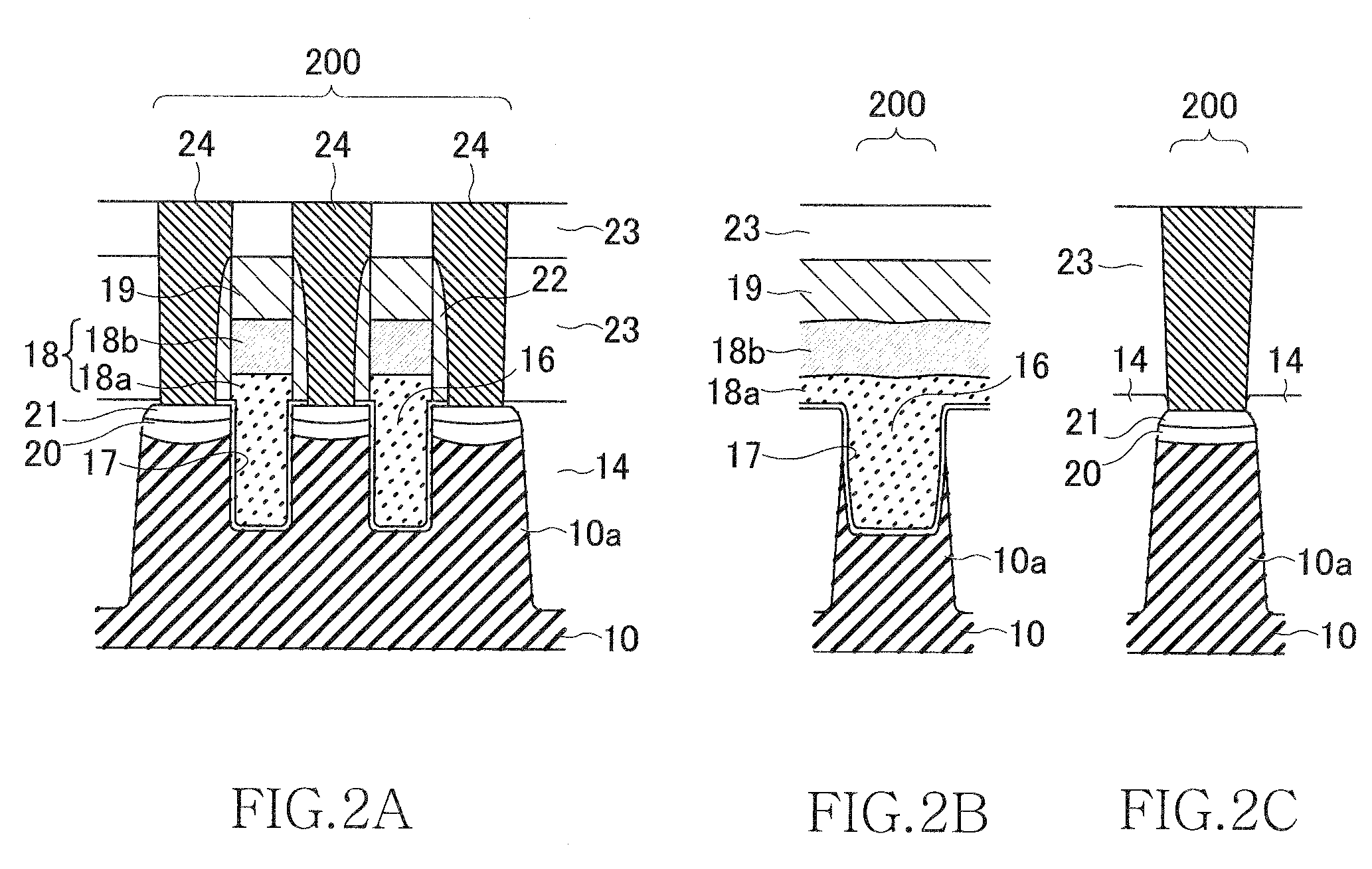

Semiconductor device, manufacturing method thereof, and data processing system

InactiveUS7923773B2Thin structureImprove featuresSolid-state devicesSemiconductor/solid-state device manufacturingData processing systemThin film soi

A bottom of a gate trench has a first bottom relatively far from an STI and a second bottom relatively near from the STI. A portion, in an active region, configuring the second bottom of the gate trench configures a side-wall channel region, and has a thin-film SOI structure sandwiched between the gate electrode and the STI. On the other hand, a portion configuring the first bottom of the gate trench functions as a sub-channel region. A curvature radius of the second bottom is larger than a curvature radius of the first bottom. In an approximate center in a length direction of the gate trench, a bottom of a trench is approximately flat, and on the other hand, in ends of the length direction, a nearly whole bottom of the trench is curved.

Owner:LONGITUDE LICENSING LTD

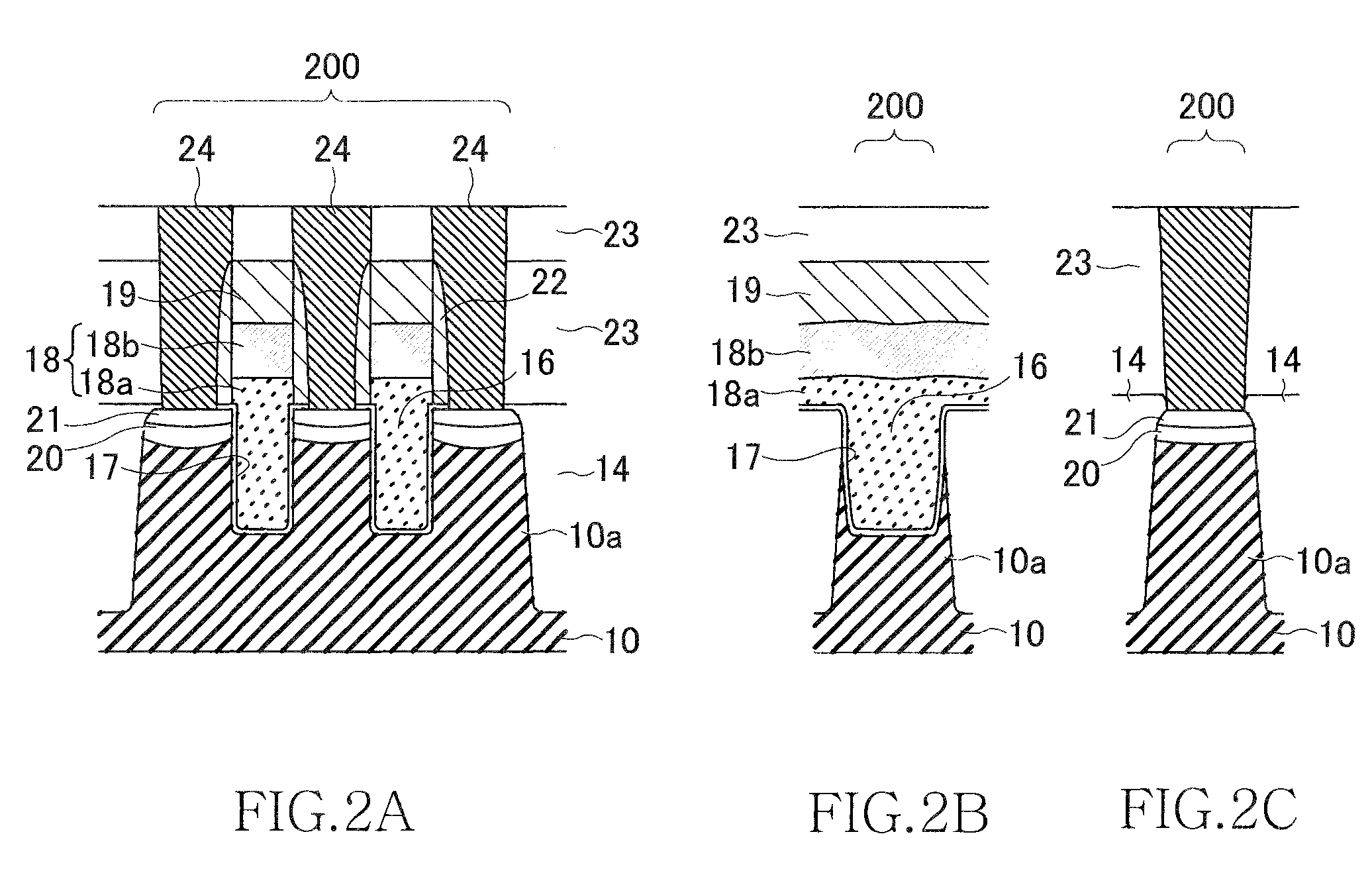

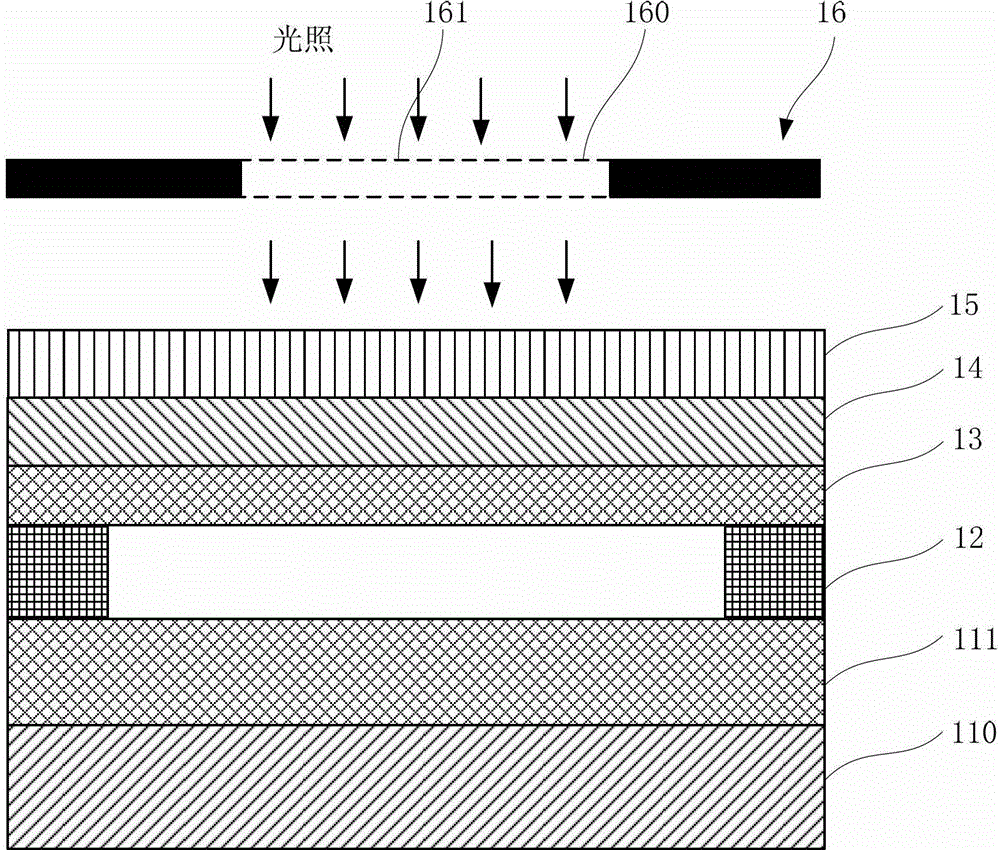

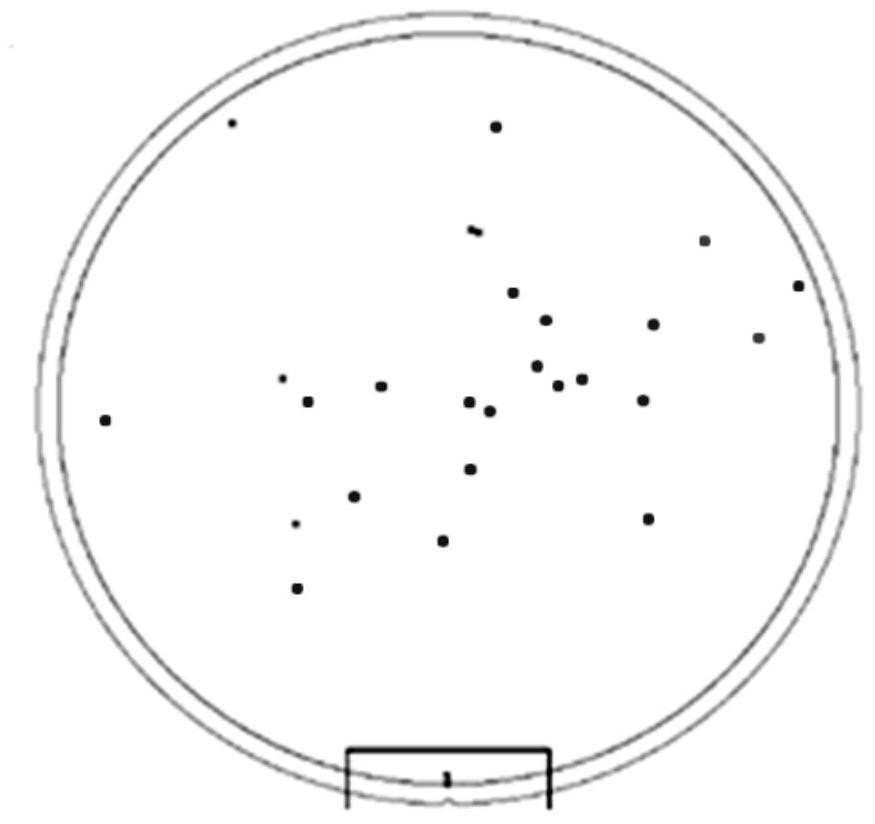

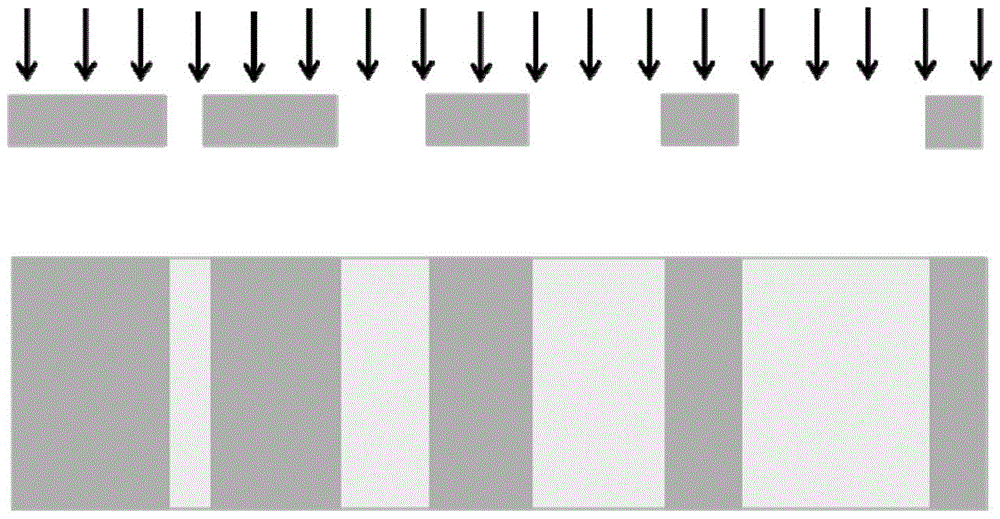

Preparation method of SOI (silicon on insulator)-based SiGe-HBT (heterojunction bipolar transistor)

InactiveCN102800590BPrevent voltage dropEasy to prepareSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceEngineering

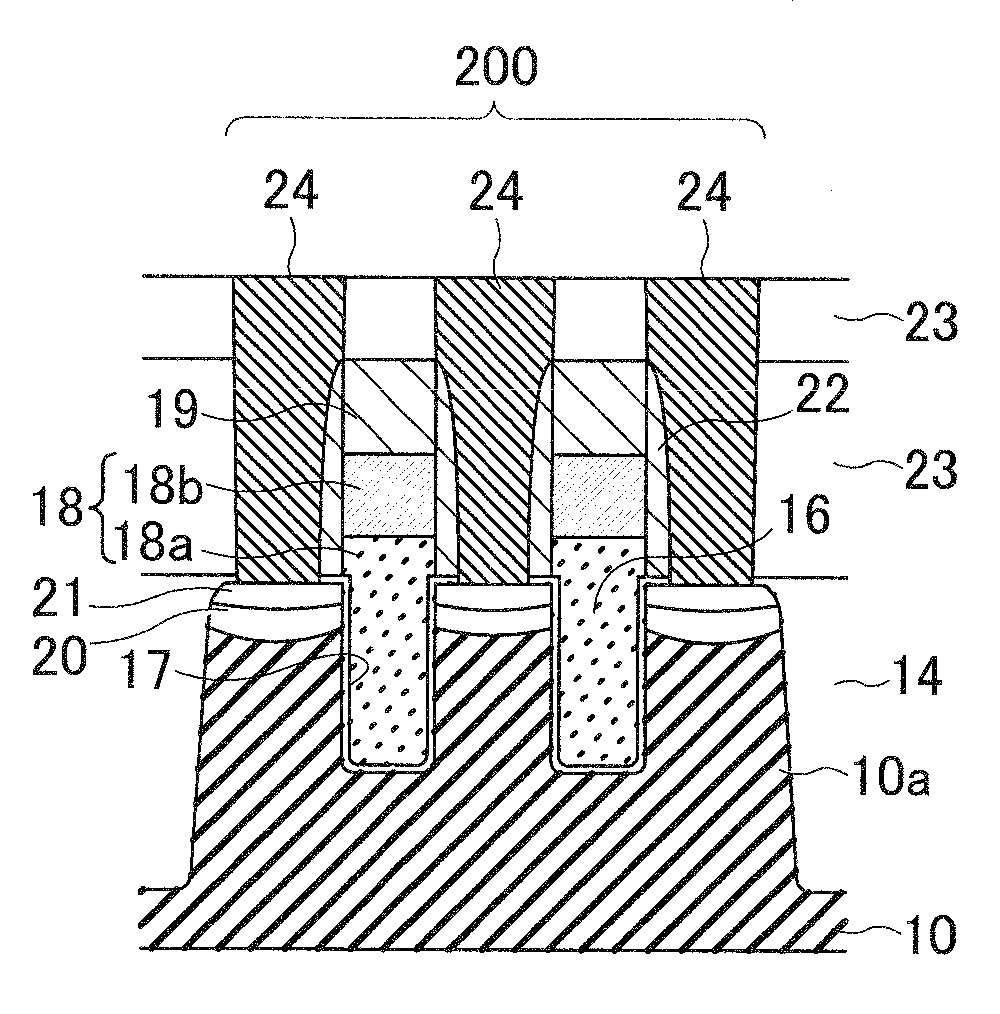

A method of manufacturing an SOI-based SiGe-HBT transistor. A specific photomask (24) is added in a doping and injection process for an outer base region (181). The photomask has the same pattern as that of the mask (16) used in forming a base region window, so as to define the injection of the outer base region within a specified region, thereby solving the problems of increased collector resistance and a reduced maximum cut-off frequency Ft parameter for SiGe BJT devices on a thin-film SOI, and also avoiding the problem of lowered voltage endurance of devices because of an increased doping concentration in a collector region.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

A method for removing silicon defects in the top layer of tm-soi

ActiveCN106981451BFix bugsQuality improvementSemiconductor/solid-state device manufacturingThin membraneSurface roughness

The invention discloses a method for removing silicon defects in the top layer of TM-SOI, belonging to the technical field of SOI preparation. The method is to chemically etch the SOI silicon wafer formed by TM-SOI to remove the damaged layer on the surface of the thin-film SOI silicon wafer. After repairing, high-quality SOI silicon wafers are obtained. The SOI prepared by this method can not only improve the surface roughness, but most importantly, can repair SOI defects, and prepare SOI materials with excellent electrical properties.

Owner:SHENYANG SILICON TECH

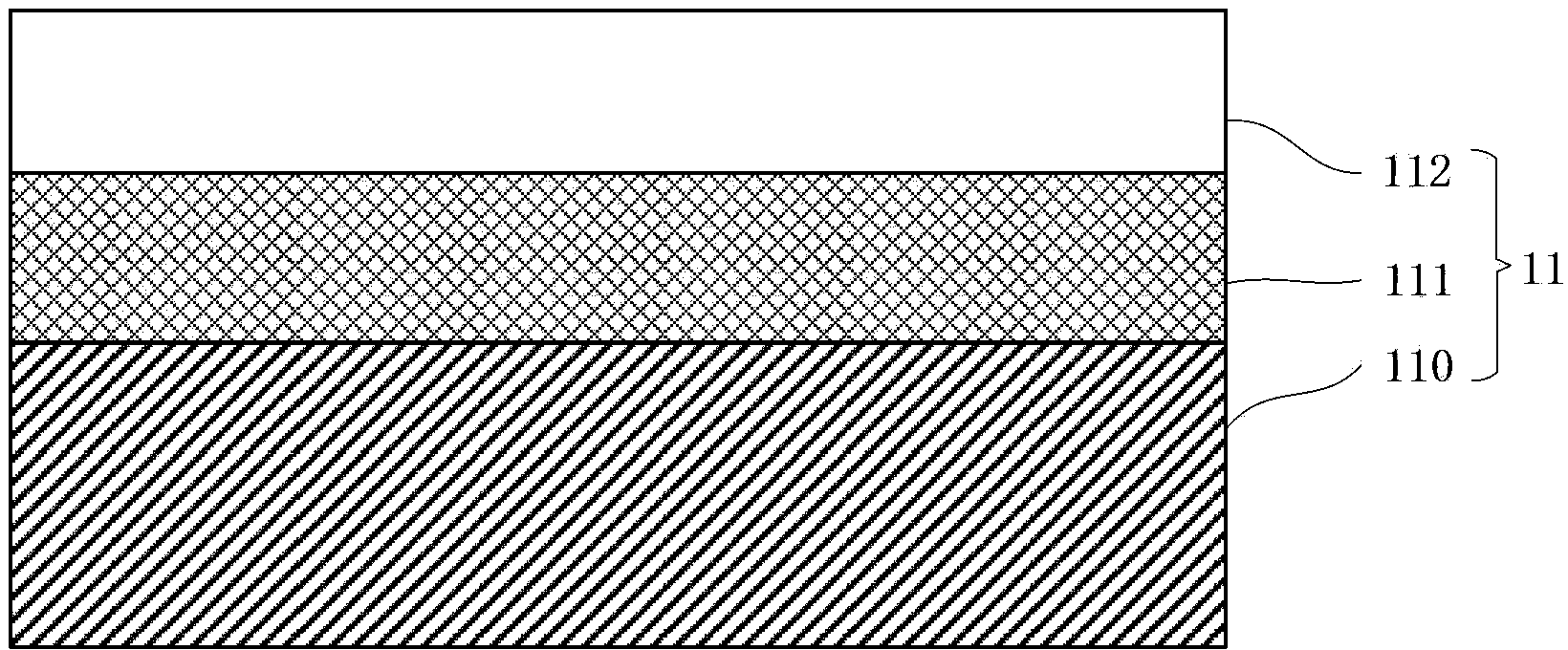

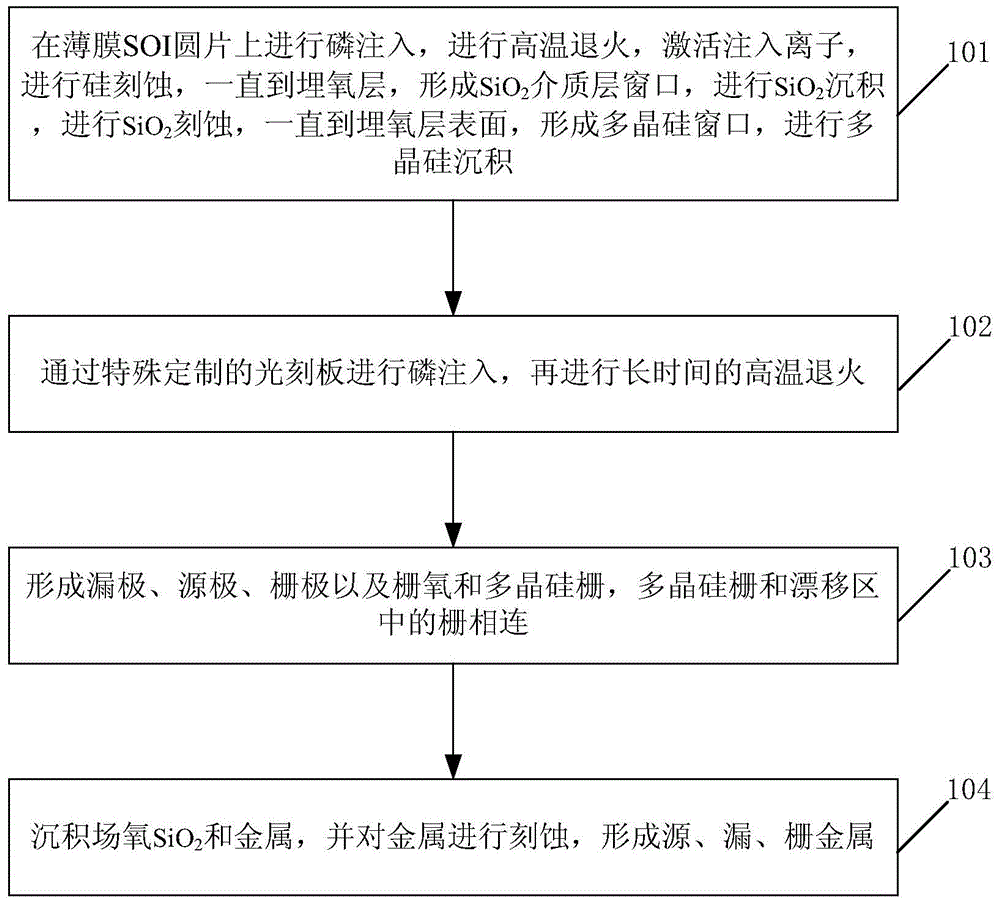

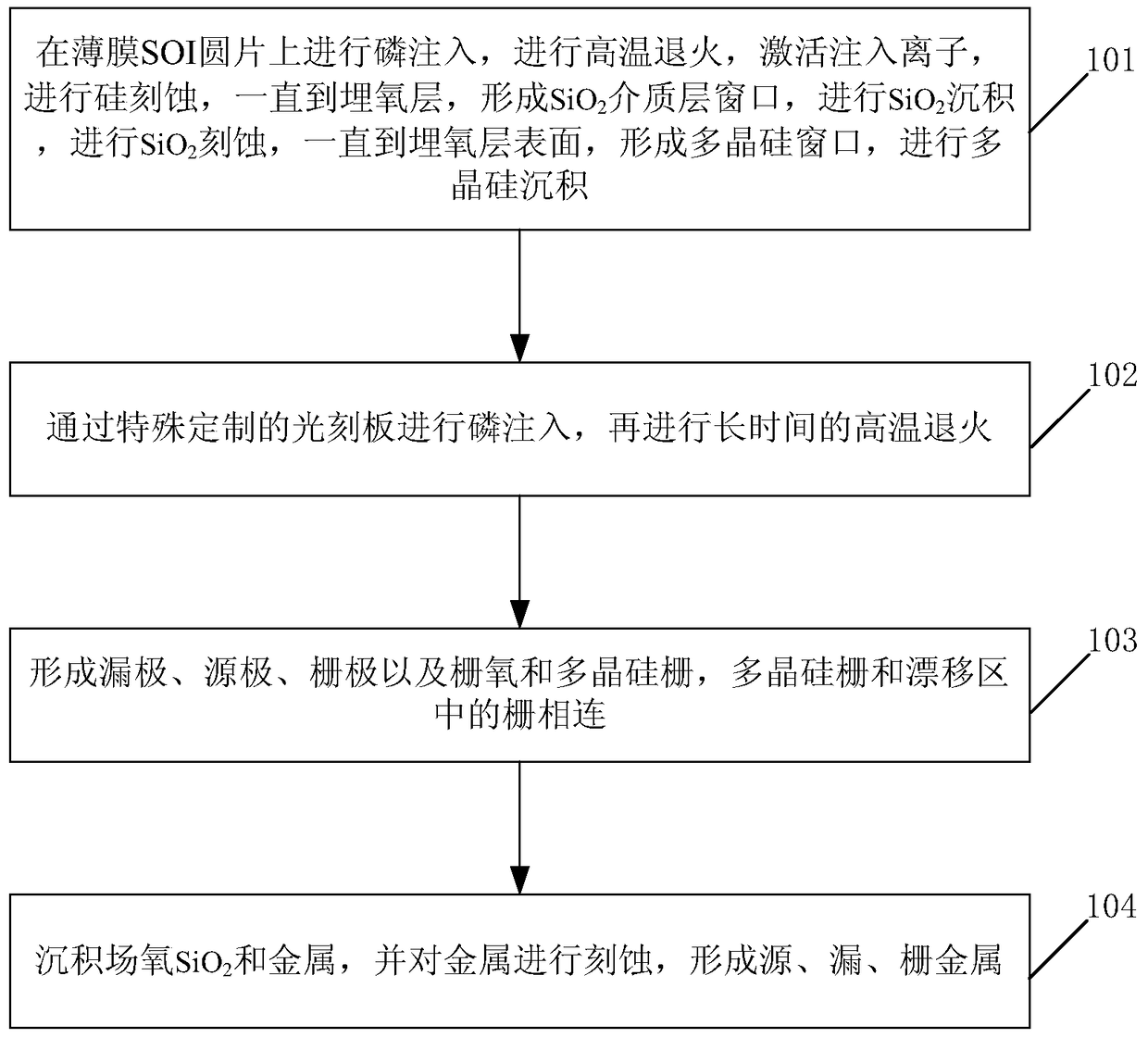

Preparation method for power device structure, and structure

ActiveCN105070661AImprove breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPolysilicon gateBreakdown voltage

The embodiment of the invention discloses a preparation method for a power device structure, and the method comprises the steps: injecting phosphorus onto a thin film SOI wafer, carrying out high-temperature annealing, activating injected ions, and carrying out heavy doping of an n-type drift region from the surface of the device to the upper surface of a buried oxide layer; carrying out silicon etching till the buried oxide layer, forming a SiO2 dielectric layer window, carrying out SiO2 deposition, carrying out SiO2 etching till the surface of the buried oxide layer, forming a polycrystalline silicon window, and carrying out polycrystalline silicon deposition; carrying out phosphorus injection through a specially-customized photoetching plate, and then carrying out long-time high-temperature annealing; forming a drain electrode, a source electrode, a grid electrode, a gate-oxide, and a polysilicon gate, wherein the polysilicon gate is connected with a gate in the drift region; depositing field oxide SiO2 and metal, carrying out the etching of the metal, and forming source, drain and grid metal, thereby effectively improving the breakdown voltage of a device, and reducing the conduction resistance of the device.

Owner:工业和信息化部电子第五研究所华东分所

MOS field effect transistor and manufacture method thereof

InactiveUS7456473B2Easy to operateReduce power consumptionSolid-state devicesSemiconductor devicesOrganic field-effect transistorEngineering

A method of manufacturing an MOS field effect transistor, which achieves a faster operation and lower power consumption by using a thin film SOI structure, is provided. The method of manufacturing an MOS field effect transistor to be formed on a semiconductor substrate having a channel layer on a buried oxide film, comprises the steps of forming: a gate electrode on the semiconductor substrate via a gate oxide film; forming a first sidewall which covers a side wall of the gate electrode; forming a box oxide film by etching the buried oxide film; and forming a second sidewall which covers a side wall of the box oxide film in such a way that the second sidewall extends downward along the side wall of the box oxide film.

Owner:FUJITSU SEMICON LTD

Semiconductor device

ActiveUS10340291B2Improve reliabilityTransistorSolid-state devicesPower semiconductor deviceSoi substrate

Owner:RENESAS ELECTRONICS CORP