Preparation method for power device structure, and structure

A technology for power devices and polysilicon, which is used in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc. It can solve the problems of limited improvement in device performance, increased device reliability, and high surface electric field of devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

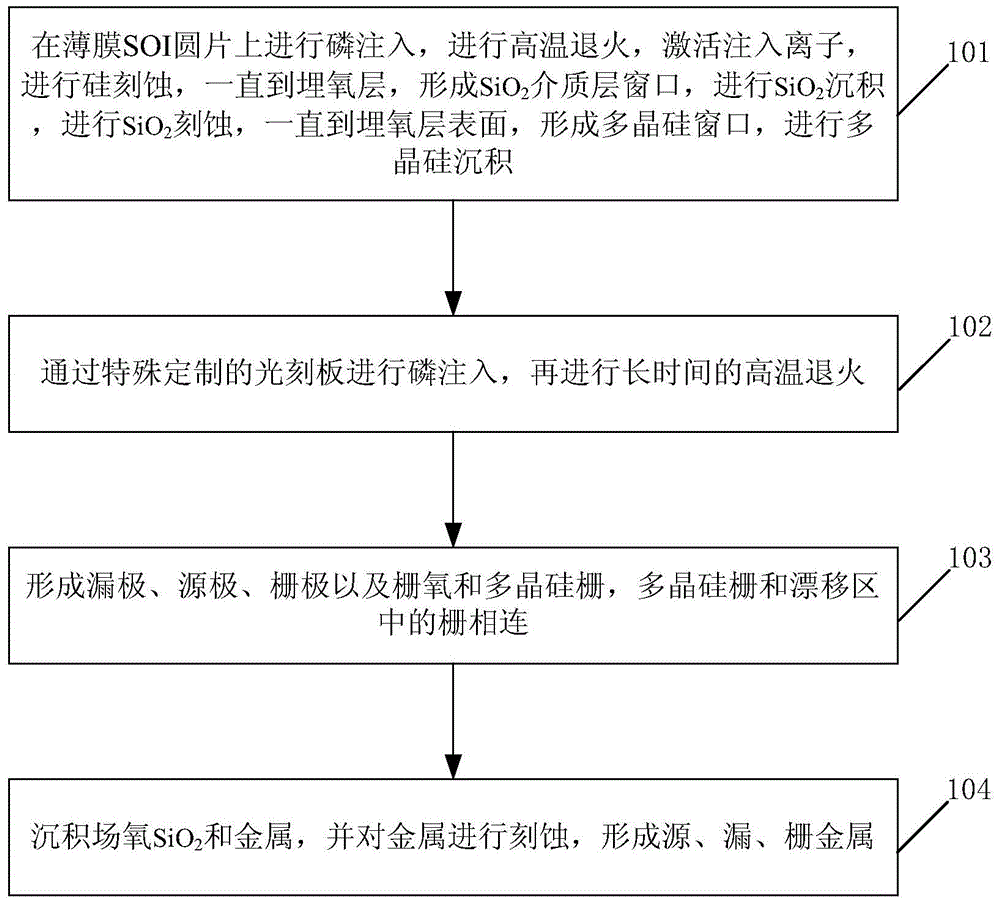

[0034] refer to figure 1 , figure 1 It is a schematic flow chart of the preparation method of the power device structure according to the embodiment of the present invention.

[0035] In Embodiment 1, the preparation method of the power device structure includes:

[0036] Step 101, perform phosphorus implantation on the thin-film SOI wafer, perform high-temperature annealing, activate implanted ions, perform silicon etching, until the buried oxide layer is formed to form SiO 2 Dielectric window, made of SiO 2 deposited, SiO 2 Etching, until the surface of the buried oxide layer, forming a polysilicon window for polysilicon deposition;

[0037] Step 102, performing phosphorus implantation through a specially customized photolithography plate, and then performing long-term high-temperature annealing;

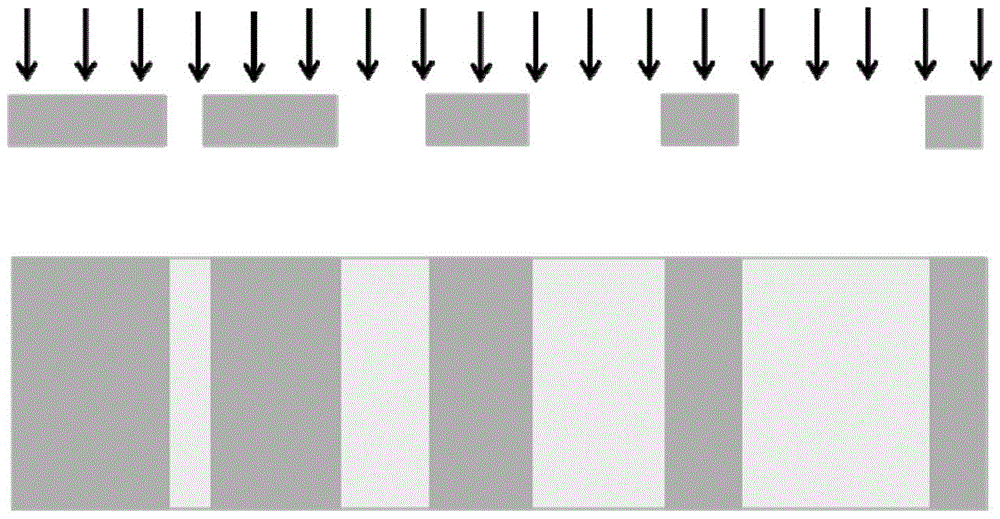

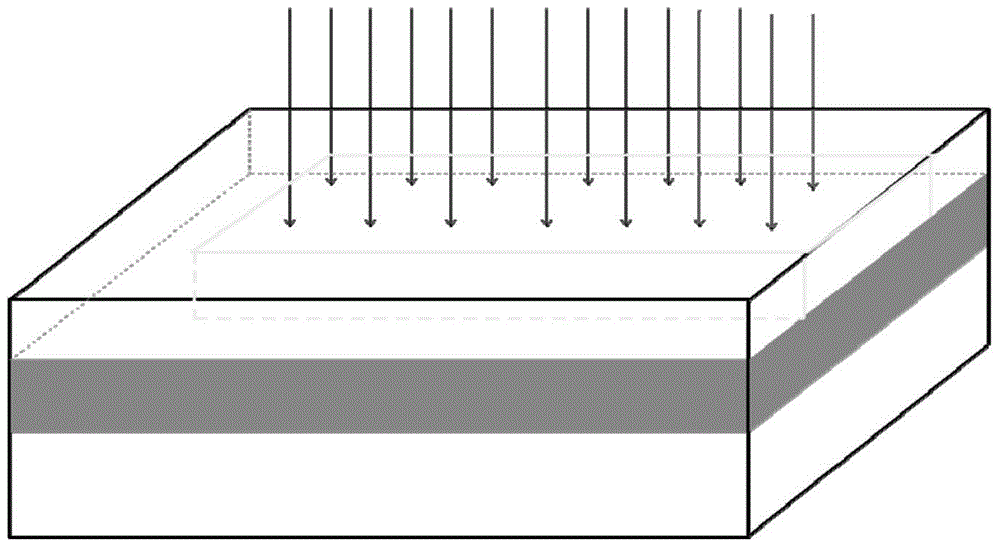

[0038] Specifically, the lithograph reference figure 2 as shown, figure 2 It is a schematic structural diagram of a photoresist plate provided by an embodiment of the pre...

Embodiment 2

[0053] refer to Figure 10 , Figure 10 is a schematic diagram of the power device structure of the embodiment of the present invention.

[0054] In Embodiment 2, the power device structure includes:

[0055] P-type substrate, buried oxide layer, source, gate, n-type offset region, linear doped polysilicon layer, heavily doped n-type layer, SiO 2 and drain;

[0056] The P-type substrate is at the bottom of the power device, the buried oxide layer is on the P-type substrate, and the doping concentration inside the linearly doped polysilicon changes from that near the source to gradually increases from one end to the end near the drain, linearly distributed, and the SiO 2 An n-type layer with high doping concentration is formed on both sides of the groove.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More