A method for removing silicon defects in the top layer of tm-soi

A TM-SOI, top-layer silicon technology, used in electrical components, circuits, semiconductor/solid-state device manufacturing, etc., can solve problems such as atomic displacement, affecting SOI quality, and achieve the effect of reducing particles, improving roughness, and improving cleanliness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

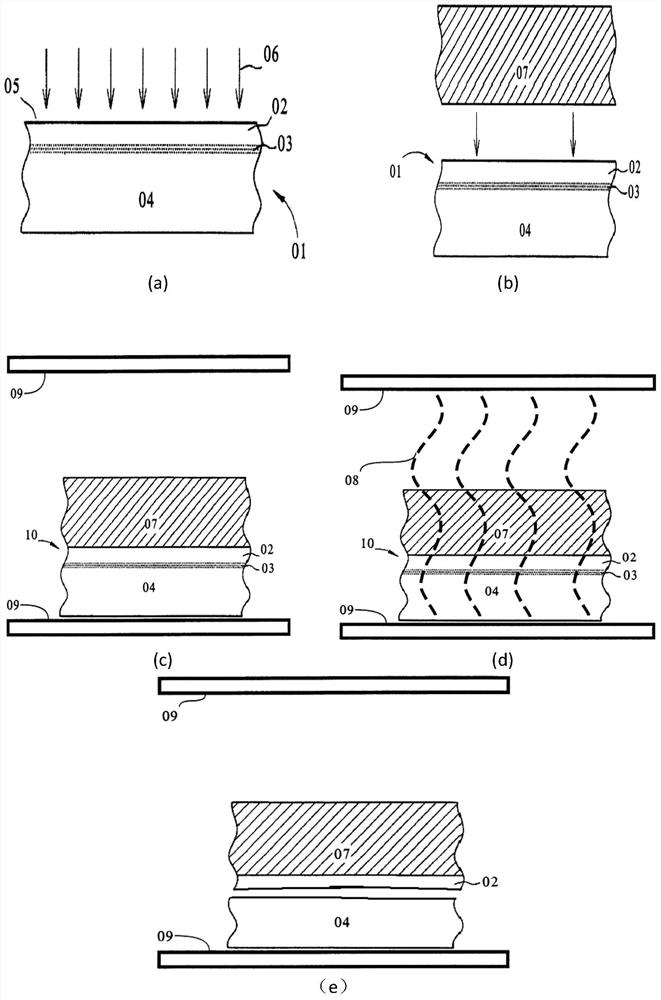

Method used

Image

Examples

Embodiment 1

[0049] Using TM-SOI technology, 3 pieces of SOI wafer materials with a diameter of 200mm after splitting were prepared, and they were placed in the reaction chamber of the epitaxy furnace for corrosion and defect repair. The specific steps are as follows:

[0050] (1) H is introduced into the reaction chamber 2 (Flow rate 50 liters / minute, purity>99.99999%), heating at 1050°C for 30 seconds, removing the natural oxide layer and impurities on the surface of the silicon wafer in situ;

[0051] (2) reduce the pressure of the reaction chamber, and the pumping pressure reaches 40torr, and the SOI silicon wafer processed through step (1) is placed in an anhydrous HCl atmosphere to corrode the silicon layer on its surface for 60 seconds;

[0052] (3) The reaction chamber is refilled with H 2 (flow rate 20 liters / minute, purity>99.99999%), restore the pressure of the reaction chamber to normal pressure, remove impurities and residual HCl in the reaction chamber, cool to the loading t...

Embodiment 2

[0063] Two pieces of the same batch of SOI wafer material as in Example 1 were taken and placed in the reaction chamber of an epitaxial furnace for HCl corrosion and defect repair. The different conditions from Example 1 are that the corrosion temperature is 850° C., the pumping pressure reaches 20 torr, and the corrosion is performed for 120 seconds. Table 3 is the test data:

[0064] table 3

[0065]

[0066]

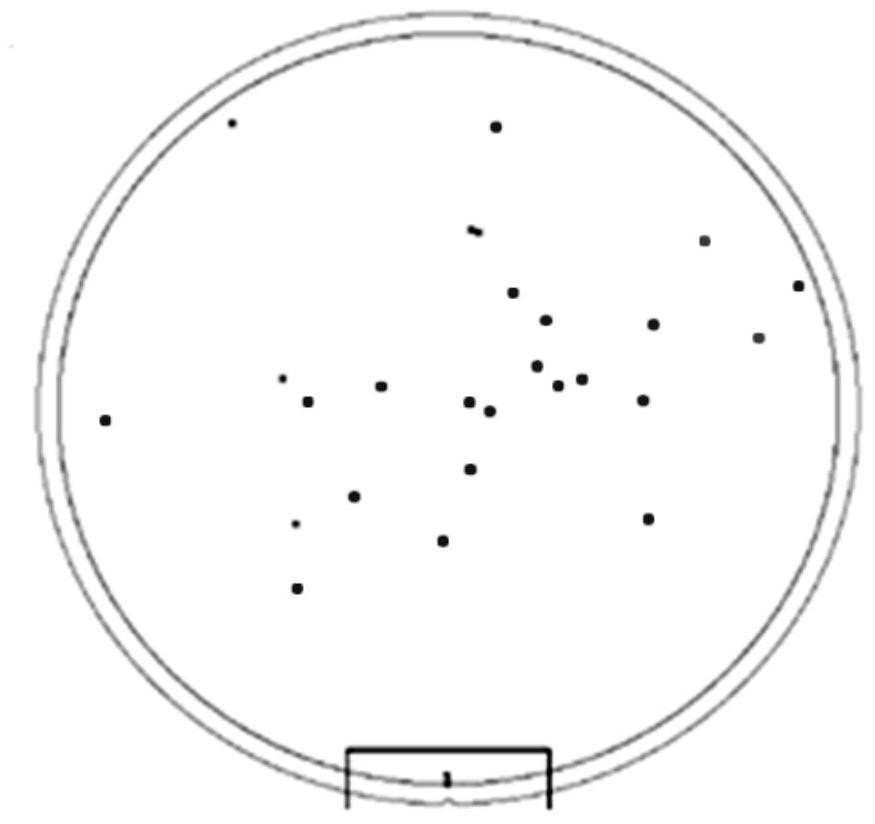

[0067] After being processed under this condition, the measured particle results are shown in Table 4, and the particle diagram is shown in image 3 , Figure 4 shown.

[0068] Table 4

[0069]

Embodiment 3

[0079] 10 SOI sheets in Example 1, Example 2, Comparative Example 1 and Comparative Example 2 were subjected to SECCO corrosion (pure water, 49% HF, potassium dichromate) for 20s, and then observed under an optical microscope to obtain The results are shown in Table 7:

[0080] Table 7

[0081] Numbering Number of defects (ea / cm 2 )

[0082] From the comparison of the data in Table 7, it can be seen that the method adopted in the present invention is obviously superior to the CMP process in terms of defect removal.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More