Semiconductor device with a metal insulator semiconductor transistor

a semiconductor transistor and semiconductor technology, applied in semiconductor devices, digital storage, instruments, etc., can solve the problem of hardening the multibit information in one memory cell as the scaling progresses, and achieve the effect of increasing the effective channel length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0061] The present embodiment provides a semiconductor device comprising an MONOS transistor having such a structure that a trench is formed in a channel portion and a silicon nitride film in a gate insulating film is formed as an electric charge holding portion to interpose the trench.

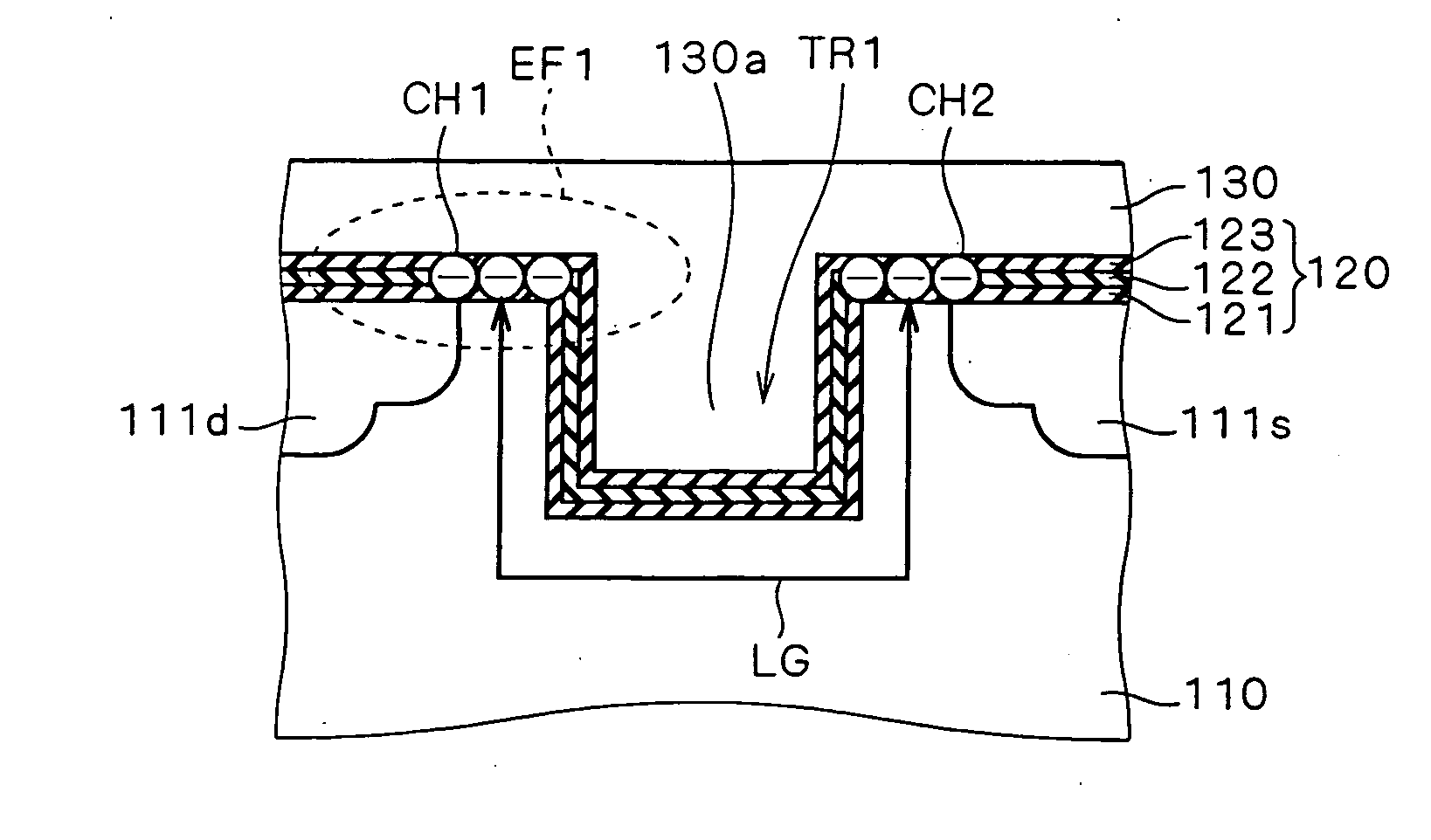

[0062]FIG. 1 is a view showing an MONOS transistor provided in a semiconductor device according to the present embodiment. As shown in FIG. 1, the MONOS transistor comprises a source region 111s and a drain region 111d which are formed in a semiconductor substrate 110 such as a silicon substrate, a gate insulating film 120 formed on the semiconductor substrate 110, and a gate electrode 130 formed on the gate insulating film 120. The gate insulating film 120 is a laminated film in which a silicon oxide film 121, a silicon nitride film 122 and a silicon oxide film 123 are sequentially provided.

[0063] In the present embodiment, a trench TR1 is formed in a channel portion between the source region 111s ...

second embodiment

[0069] The present embodiment is an example of a method of manufacturing the semiconductor device according to the first embodiment.

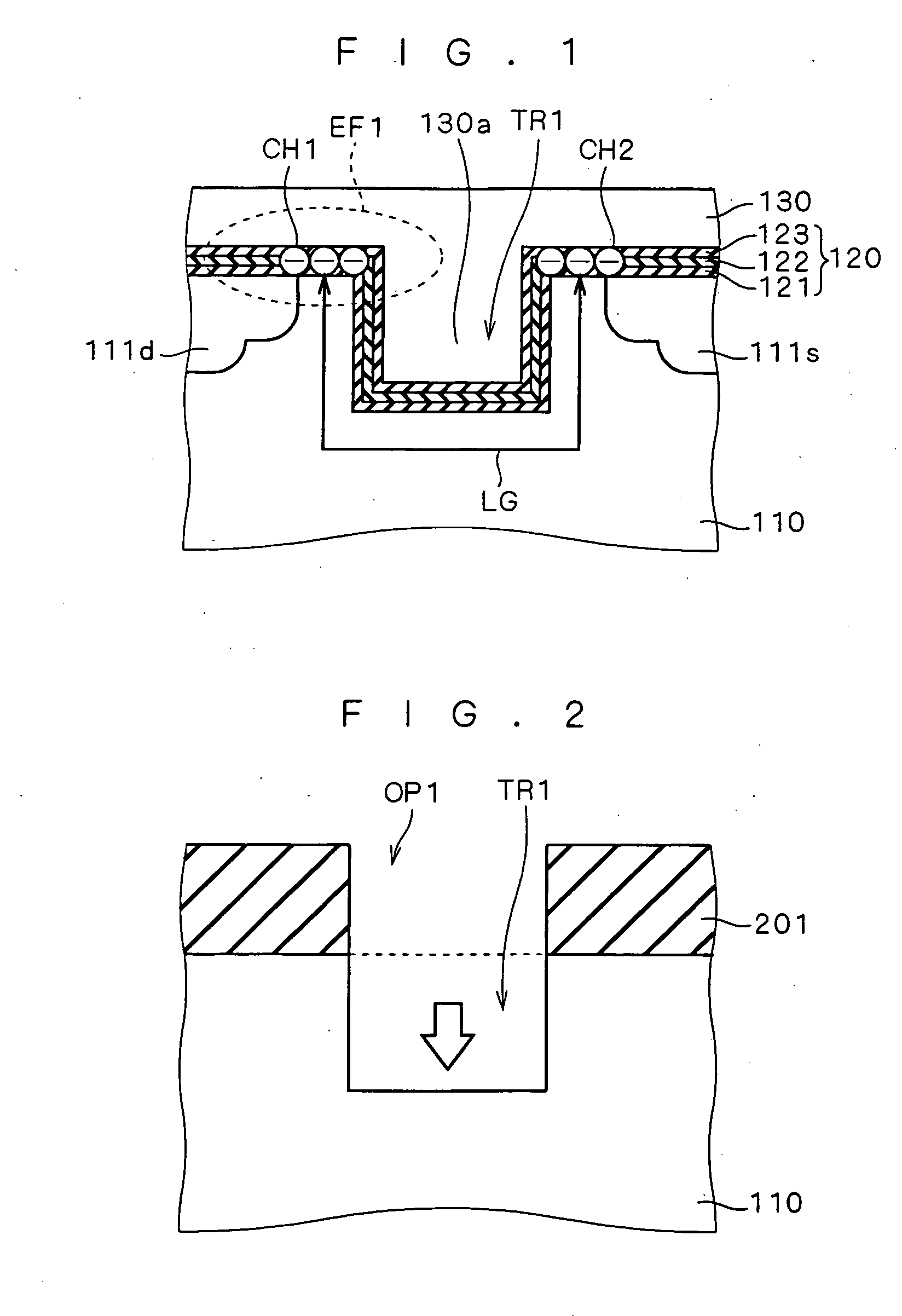

[0070] First of all, as shown in FIG. 2, a mask 201 such as a photoresist, a silicon oxide film or a silicon nitride film is formed on a semiconductor substrate 110, and an opening OP1 is provided therein so that a trench TR1 is formed on a surface of the semiconductor substrate 110 by anisotropic etching.

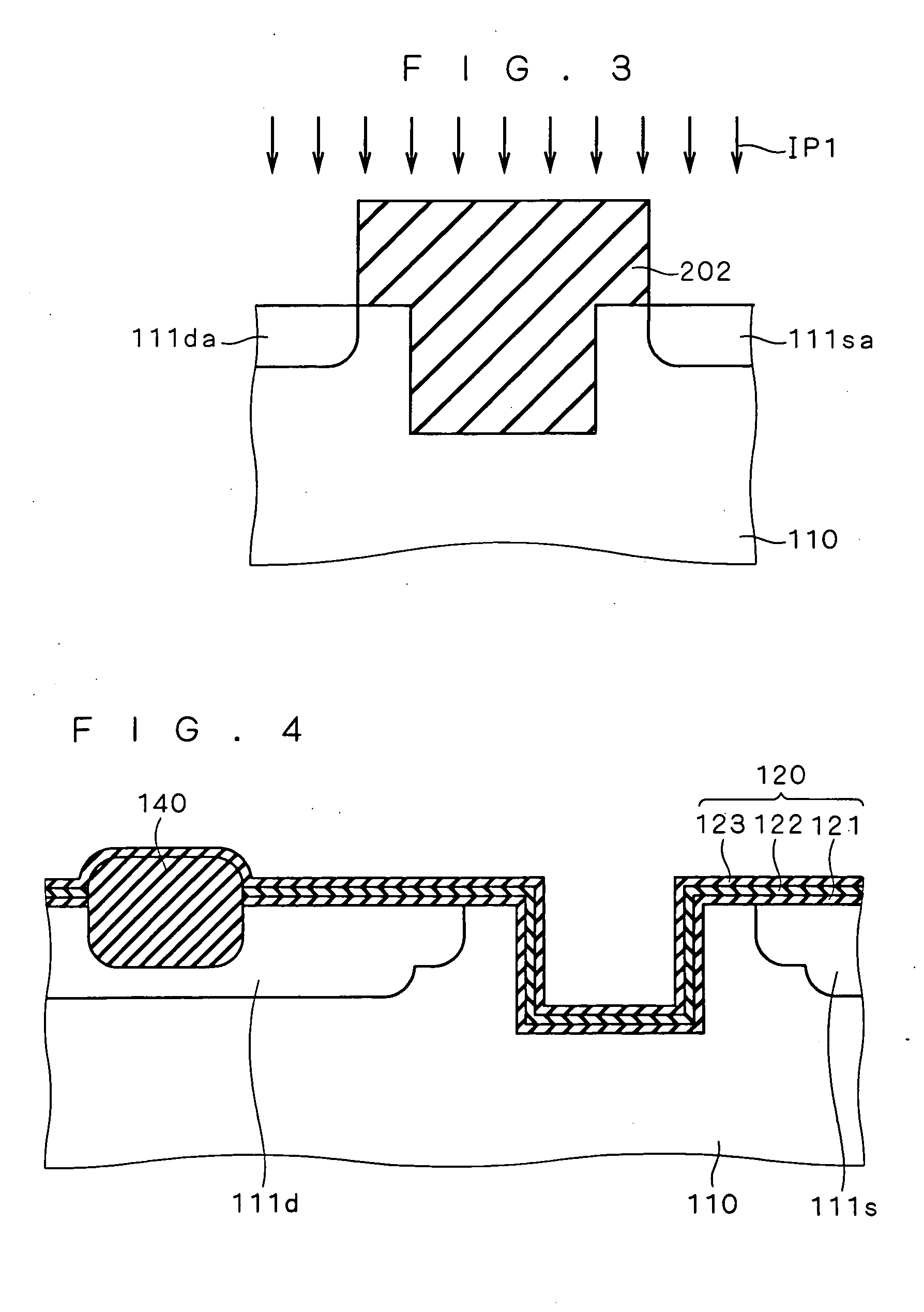

[0071] Next, well formation, channel doping and the like are carried out. As shown in FIG. 3, then, a mask 202 such as a photoresist is formed and LDD (Lightly Doped Drain) regions 111sa and 111da are formed by an impurity implantation IP1 in positions facing the surface of the semiconductor substrate 110 with the trench TR1 interposed therebetween. In the same manner, thereafter, an impurity is implanted in a higher concentration than that of each of the LDD regions 111sa and 111da to form a source region 111s and a drain region 111d.

[0072] Subsequ...

third embodiment

[0093] The present embodiment is another example of the method of manufacturing the semiconductor device according to the first embodiment.

[0094] First of all, a dummy film (for example, a silicon oxide film) 203 is formed on a semiconductor substrate 110 and a first mask film (for example, a silicon nitride film) 204 having an etching selectivity for the dummy film 203 is further formed on the dummy film 203 (FIG. 5). The reason why (120) is attached to the designation of the dummy film 203 in FIGS. 5 to 13 is that these drawings are also used in a seventh embodiment. In the present embodiment, a portion having (120) attached thereto can be disregarded.

[0095] Next, a photoresist 205 is formed and is then patterned to provide an opening OP2 (FIG. 6). Thereafter, anisotropic etching is carried out over the dummy film 203 and the first mask film 204. Consequently, an opening is formed in a region AR1 in which an isolating region is to be formed (FIG. 7).

[0096] Subsequently, the pho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More