Method for manufacturing semiconductor integrated circuit device

a semiconductor integrated circuit and manufacturing method technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problem of more difficult to maintain a long tddb lifetime, and achieve the effect of improving the dielectric breakdown strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

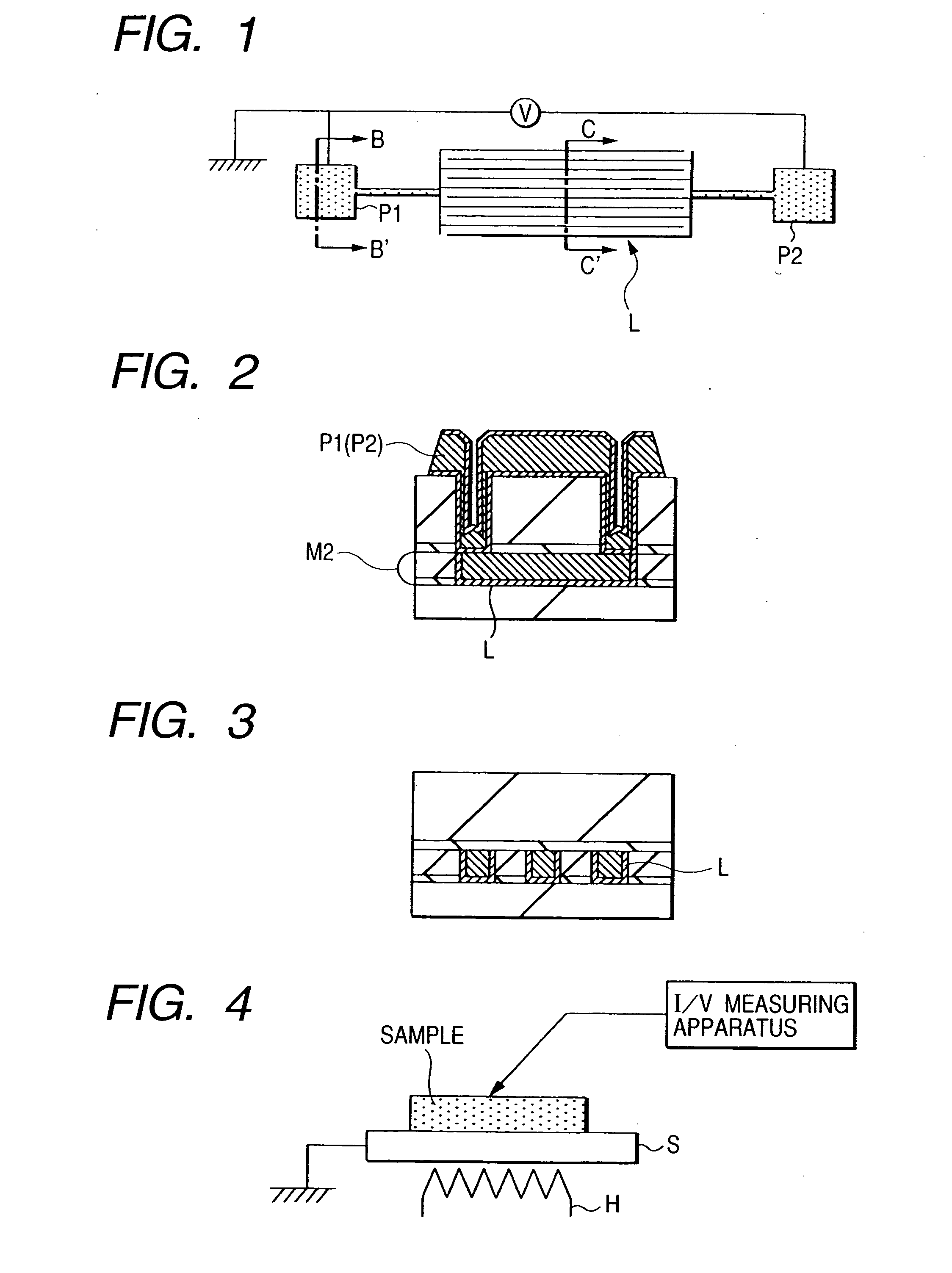

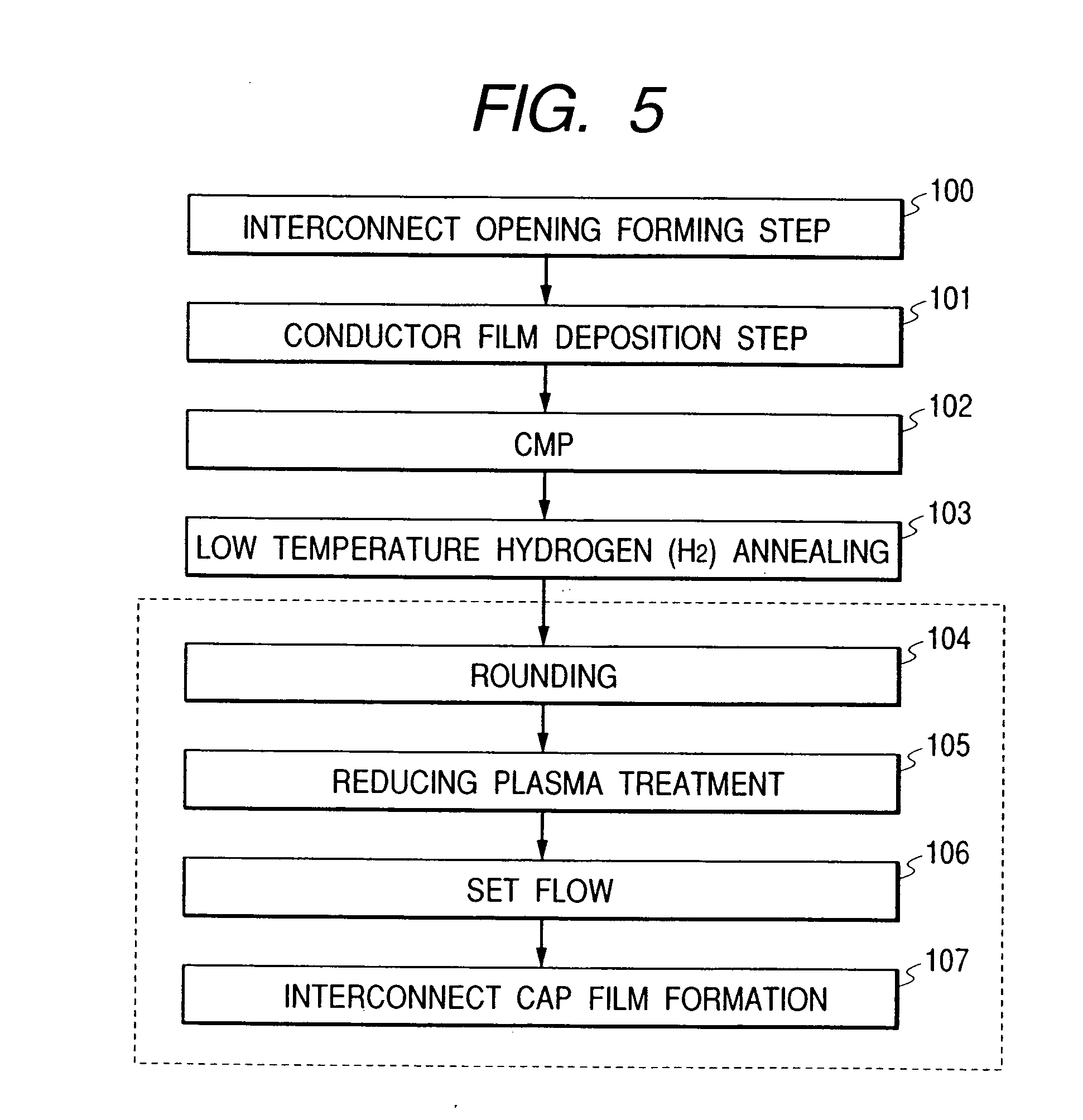

[0199] In this Embodiment, based on FIGS. 6 to 18 in accordance with the production flowchart of FIG. 5, explanation is made on the case where the technical idea of the present invention is applied to a manufacturing method of a CMIS (Complimentary MIS)-LSI (Large Scale Integrated Circuit). The step encompassed with a dotted line in FIG. 5 shows the treatment in the same treating chamber.

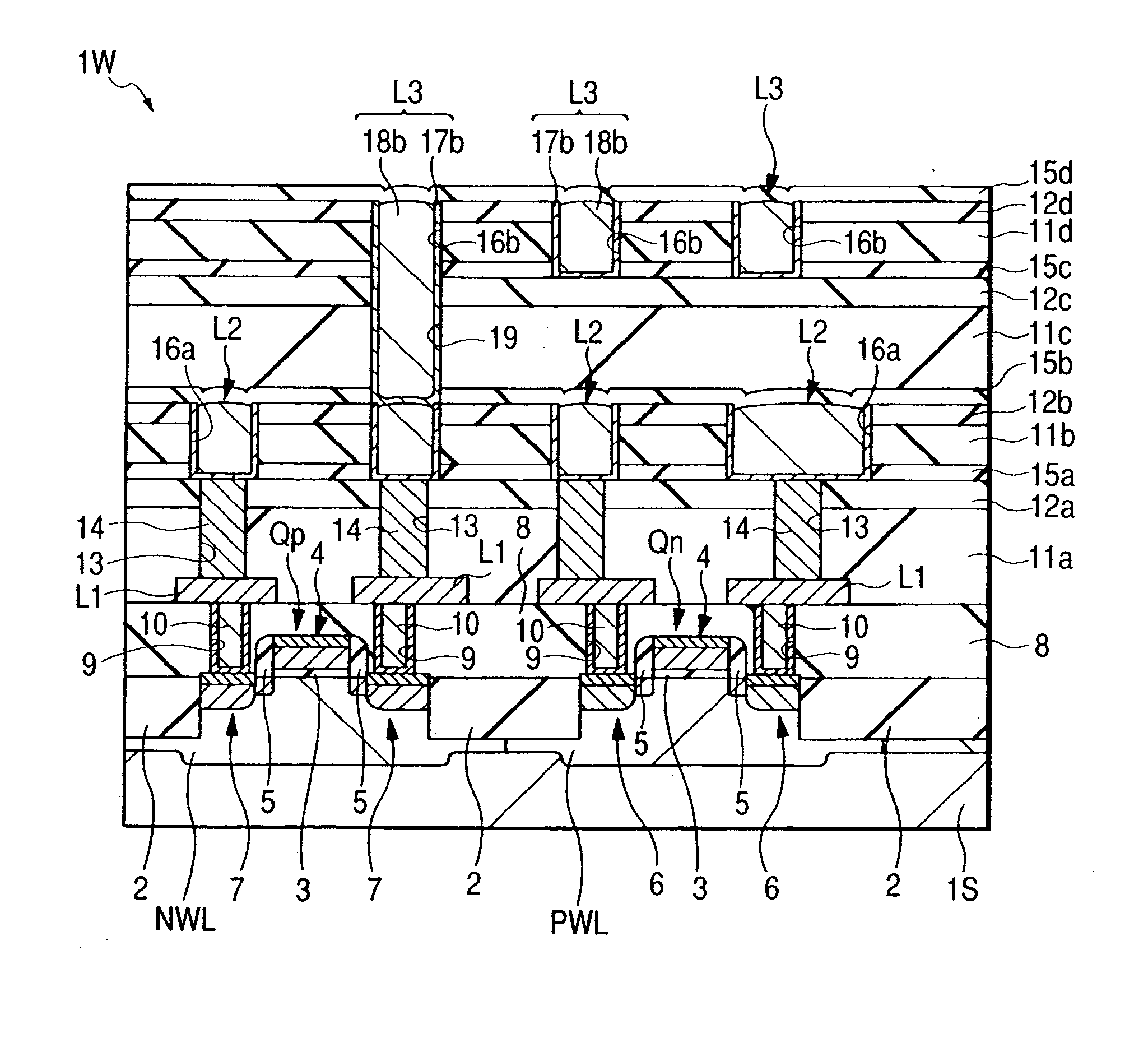

[0200]FIG. 6 is a fragmentary plane view of a CMIS-LSI during its manufacturing step and FIG. 7 is a cross-sectional view taken along a line X1-X1 of FIG. 6. A semiconductor substrate 1 (which will hereinafter be called substrate” simply) constituting a wafer 1W is made of p-type single crystal silicon having a specific resistance of about 1 to 10 Ωcm. The semiconductor substrate 1 has, on the main surface (surface on which a device is to be formed) thereof, an isolating trench (SGI (Shallow Groove Isolation) or STI (Shallow Trench Isolation)) 2. This isolation trench 2 is formed by embedding, for ...

embodiment 2

[0241]FIG. 19 is a flowchart of the manufacturing step of the semiconductor device according to another embodiment of the present invention. In this Embodiment 2, as illustrated in FIG. 19, the round taper of the main conductor film of the inlaid interconnect is formed in the set flow step 106. Described specifically, when the interconnect capping insulating film is made of a silicon nitride film, a silicon carbide film, an SiCN film or a silicon oxynitride film, a carrier gas such as nitrogen or helium is fed prior to feeding of a treatment gas upon set flow. While the time from the starting of feeding with the carrier gas until the starting of feeding with the treatment gas is set longer than that of the ordinary set flow, annealing is conducted during the introduction term of only the carrier gas, and stage temperature is set at a temperature as described in Embodiment 1, the wafer 1W is subjected to annealing treatment similar to that described in the round formation step of Emb...

embodiment 3

[0242] In Embodiment 3, a description will be made on the formation of an interconnect capping insulating film as a multilevel film. The insulating film is formed as a multilevel film in order to dissolve the problem discovered for the first time by the present inventor that when an SiON film such as the above-described “PE-TMS” (product of Canon) is employed as an interconnect capping insulating film, the conductive barrier film is inevitably oxidized upon formation of the insulating film. FIG. 20 is a fragmentary cross-sectional view of a semiconductor device, during its manufacturing process, according to a further embodiment of the present invention.

[0243] Upon deposition of an interconnect capping insulating film (second insulating film) 15b by CVD over the upper surface of the inlaid second-level interconnect L2 and insulating film 12b after the above-described ammonia plasma treatment without release of the chamber to the air, the insulating film 15b is deposited in order to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More