Semiconductor device and its manufacturing method

a technology of semiconductors and semiconductors, applied in semiconductor devices, electrical equipment, transistors, etc., can solve the problems of inability to manufacture a conventional one-layer gate type non-volatile memory, and achieve the effects of enhancing the reliability of both gate oxide films, reducing film thickness variation, and enhancing the reliability of high-voltage endurance gate oxide films

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

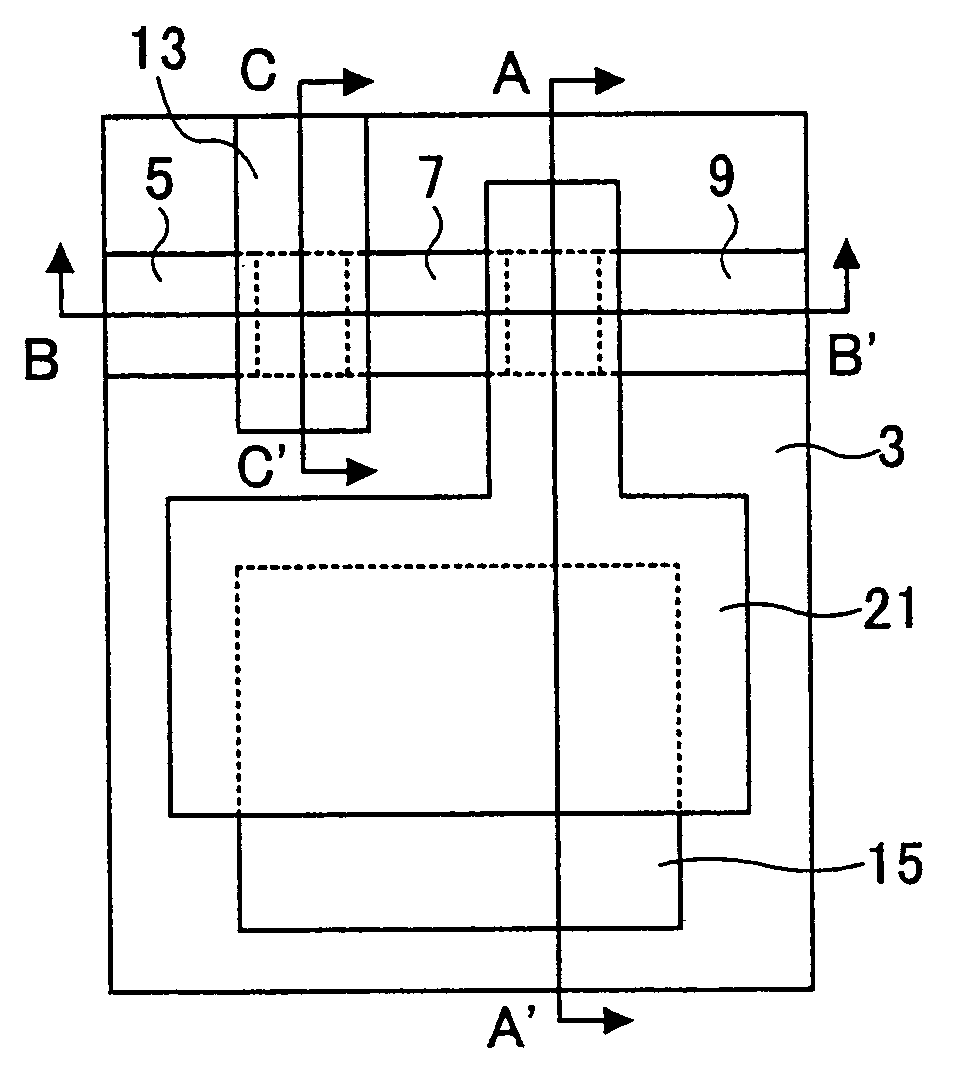

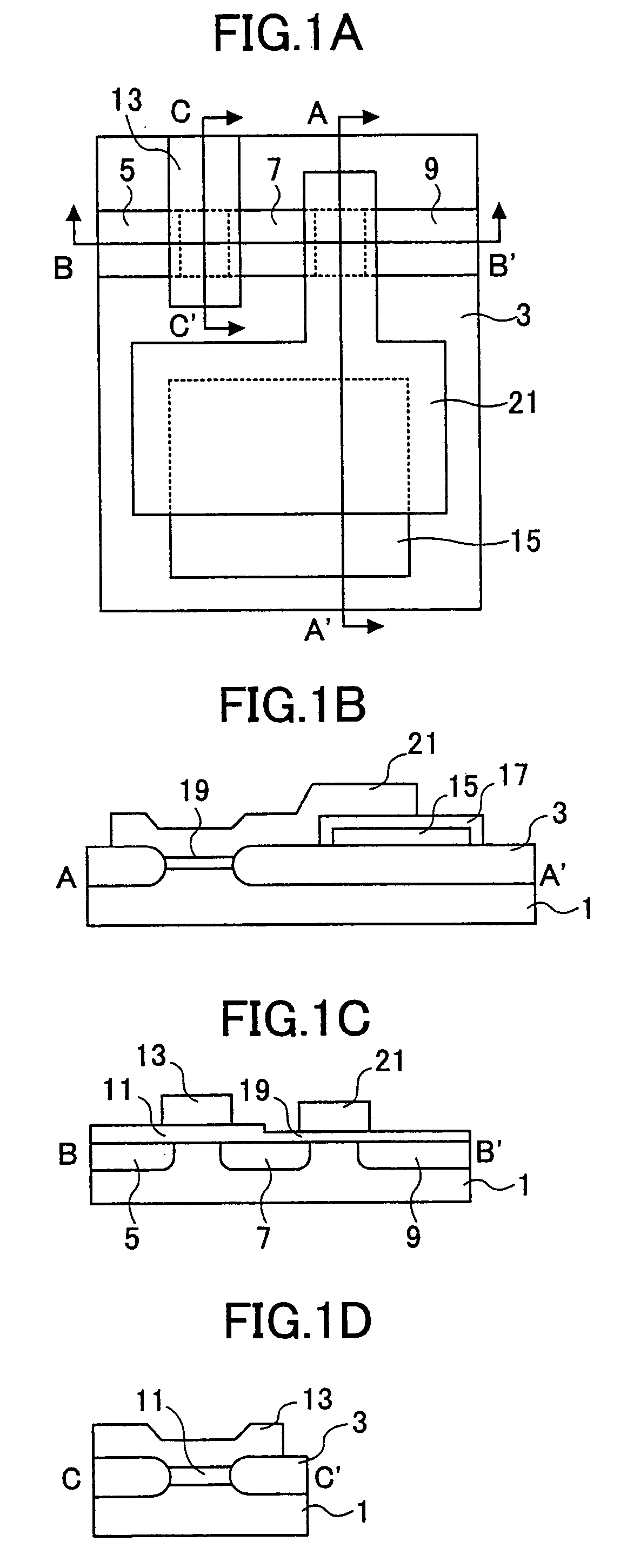

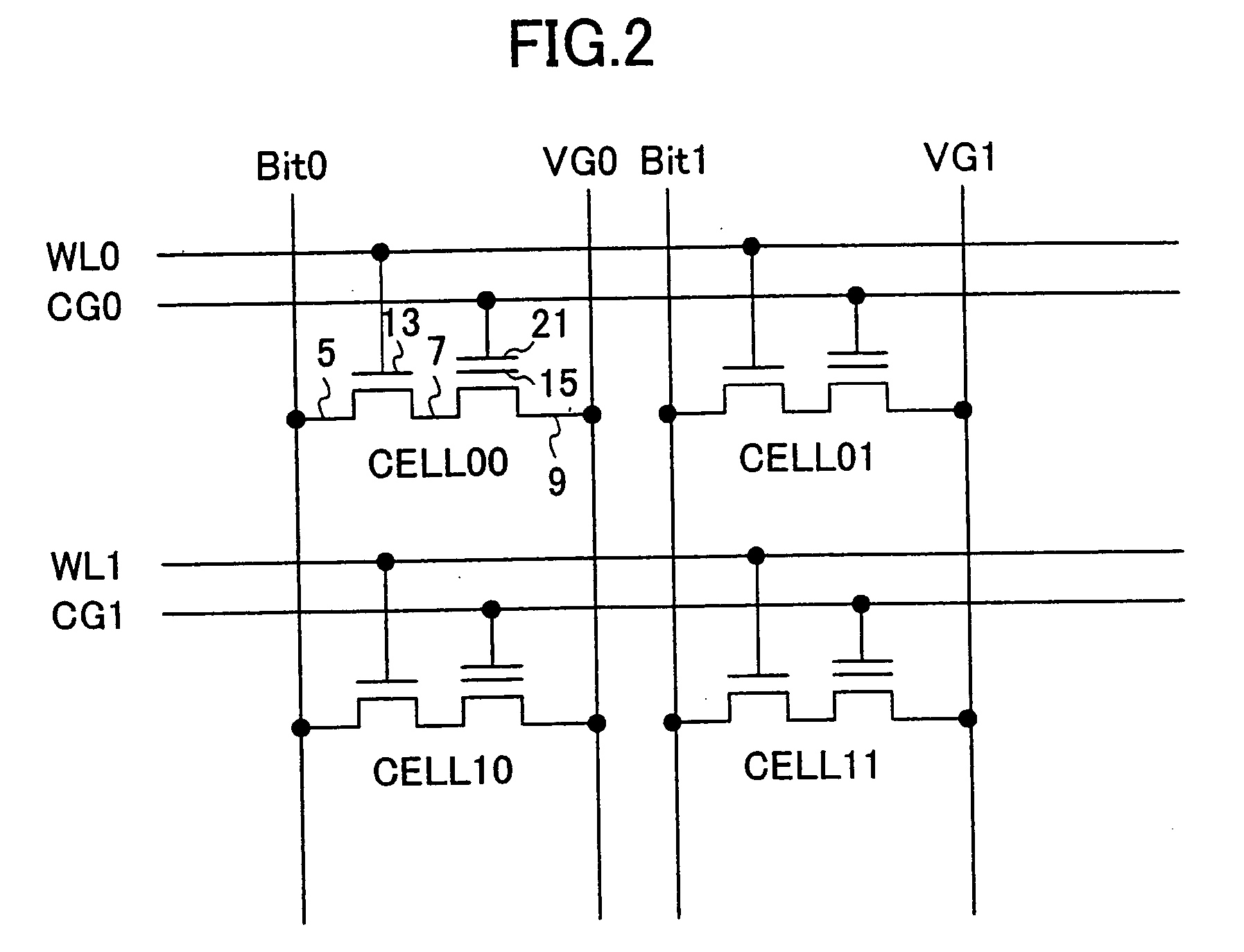

[0086]FIG. 1 shows the semiconductor device. A plan view is shown at sub-section (A), a sectional view in the A-A′ cross-section of the sub-section (A) is shown at sub-section (B), a sectional view in the B-B′ cross-section of the sub-section (A) is shown at sub-section (C), and a sectional view in the C-C′ cross-section of the sub-section (A) is shown at sub-section (D). Although this embodiment describes only one memory unit, the embodiment is applicable to any number of memory units. This embodiment is explained with reference to FIG. 1.

[0087] A field oxide film 3 (first insulation film) for unit separation is formed on the surface of a P substrate 1 in thickness, for example, between 4500 A and 7000 A. Here, in this embodiment, the film is formed 5000 A thick. N type diffusion layers 5, 7, and 9 are formed in an active region of the P substrate 1 surrounded by the field oxide film 3. The N type diffusion layers 5 and 7 are formed with an interval, and the N type diffusion layers...

second embodiment

[0114] The memory unit of the semiconductor device is provided with the laminating film 31 that contains the silicon nitride film through which an electron cannot travel easily between the control gate 15 and the floating gate 21, thereby the reliability of the memory is enhanced.

[0115]FIG. 6 shows sectional views for explaining the second embodiment of the manufacturing method for manufacturing the semiconductor device of the second embodiment, the sectional views being in the A-A′ cross-section and C-C′ cross-section of the sub-section (A) of FIG. 5. Sectional views in the B-B′ cross-section of the sub-section (A) of FIG. 5 is the same as FIG. 4. The embodiment of this manufacturing method is explained with reference to FIG. 4 through FIG. 6.

[0116] (1) The field oxide film 3 for unit separation is formed on the P substrate 1 by the usual LOCOS method. The sacrifice oxide film 23 is formed on the active region surface demarcated by the field oxide film 3, and a channel dope inject...

fifth embodiment

[0156] In the semiconductor device, since the tunnel oxide film 53 with film thickness thinner than the gate oxide film 19 for the memory is formed, writing to and erasing the memory can be performed through the tunnel oxide film 53, and the flexibility in designing the memory characteristic is enhanced.

[0157]FIG. 13 and FIG. 14 show sectional views for explaining the fifth embodiment of the manufacturing method for manufacturing the semiconductor device of the fifth embodiment. FIG. 13 shows the sectional view in the A-A′ cross-section and in the C-C′ cross-section of the sub-section (A) of FIG. 12, and FIG. 14 shows the sectional view in the B-B′ cross-section of the sub-section (A) of FIG. 12. The embodiment of this manufacturing method is explained with reference to FIG. 12 through FIG. 14.

[0158] (1) The field oxide film 3 for unit separation is formed on the P substrate 1 by the usual LOCOS method. A sacrifice oxide film in film thickness between 250 A and 400 A is formed on t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More