Circuit and method for a three dimensional non-volatile memory

a non-volatile memory and circuit technology, applied in the field of circuits and methods for providing three-dimensional non-volatile memory cells, can solve the problems of device failure, unpredictable threshold voltage (vt), other deleterious effects, etc., and achieve the effects of high integration, relaxed thermal budget for semiconductor processes, and dense and compact structur

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034]The making and using of the presently preferred embodiments are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

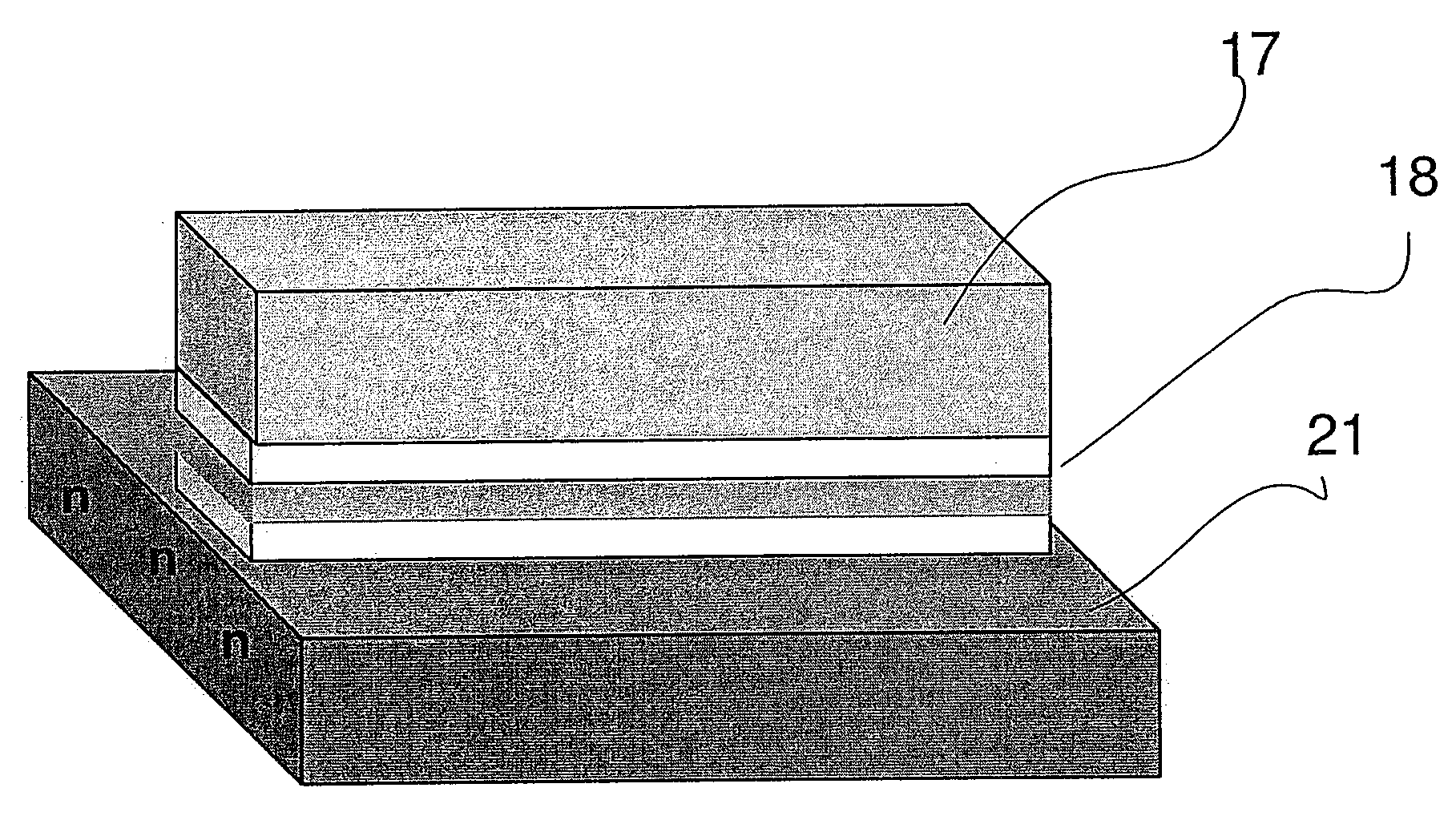

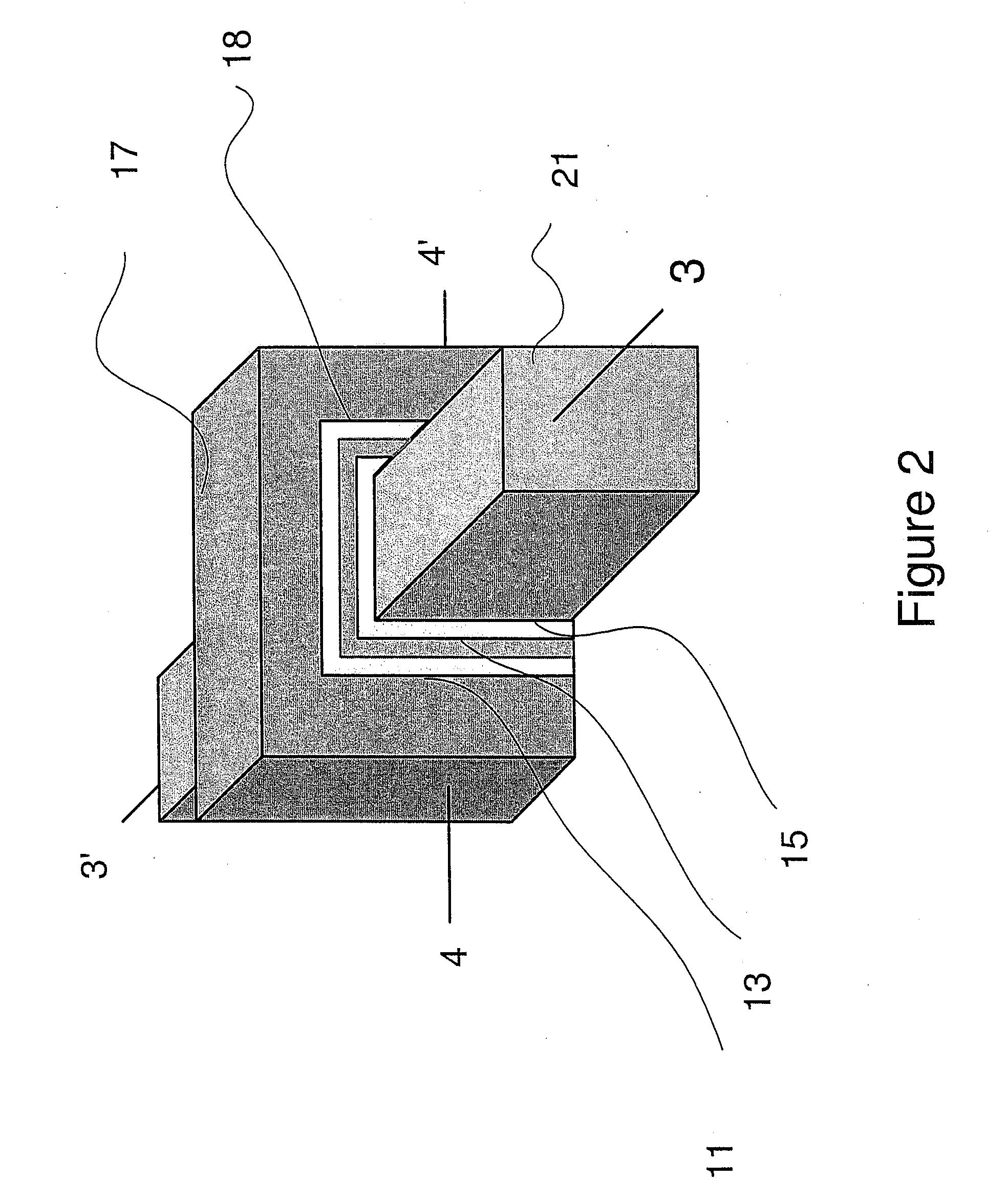

[0035]FIG. 2 depicts in a simple three dimensional view a preferred embodiment of the non-volatile memory cell of the invention. In the preferred embodiment of FIG. 2, the cell is implemented using a FinFET or triple gate MOS transistor approach. A silicon layer 21, typically an epitaxially grown or otherwise deposited polysilicon, is formed and uniformly doped. Alternatives to the polysilicon include bulk silicon, which is doped. The doping is preferentially performed as the polysilicon is deposited or grown, e.g. in situ and in a preferred embodiment, the doping is uniform....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More