Non-Volatile Memory Device with Improved Immunity to Erase Saturation and Method for Manufacturing Same

a non-volatile memory and memory device technology, applied in the direction of semiconductor devices, basic electric elements, electrical apparatus, etc., can solve the problems of affecting the efficiency of the control gate, the use of the p-type polysilicon control gate, and the tendency to change the effective work function towards midgap, etc., to achieve the effect of improving the immunity to erase saturation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

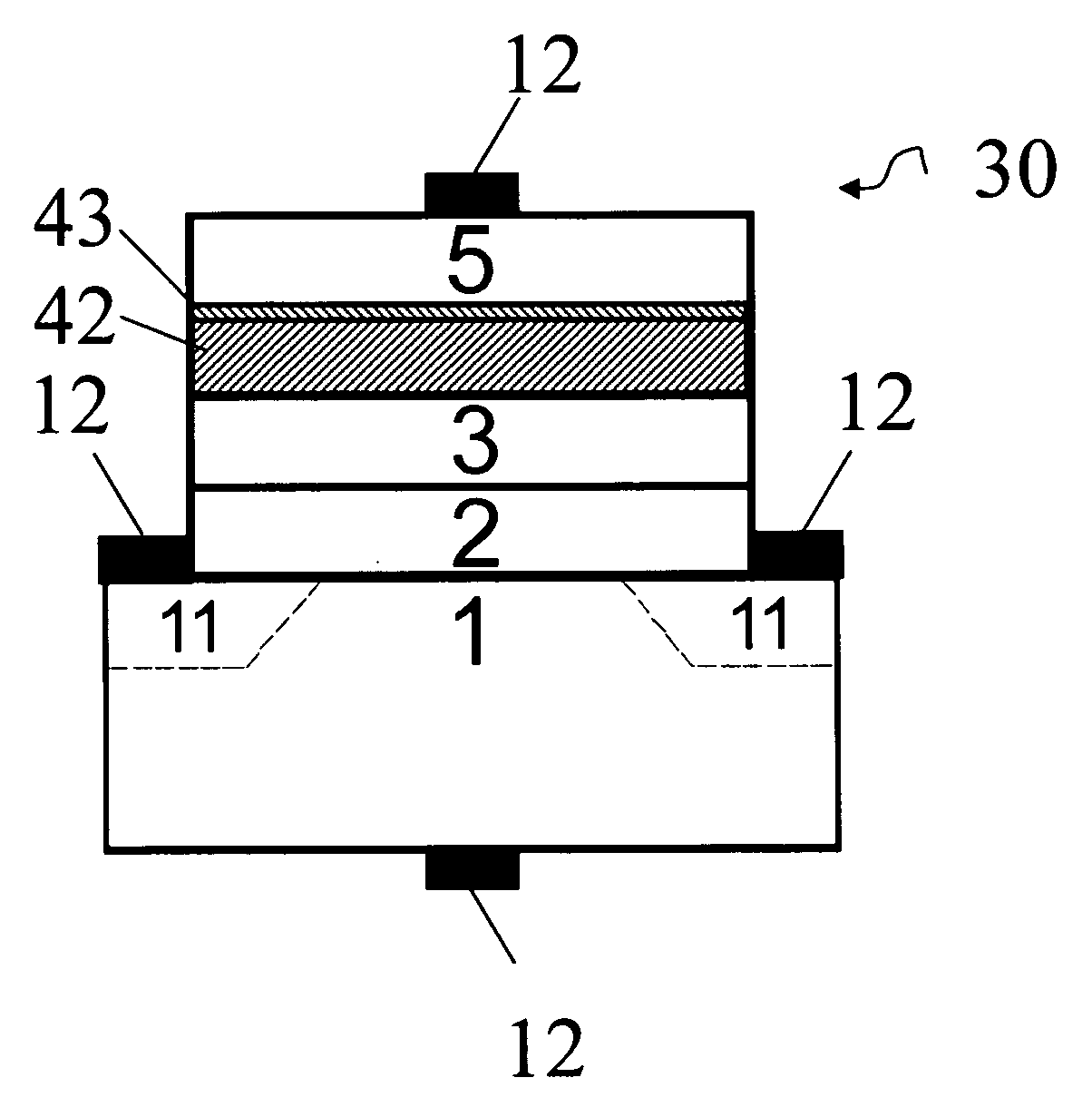

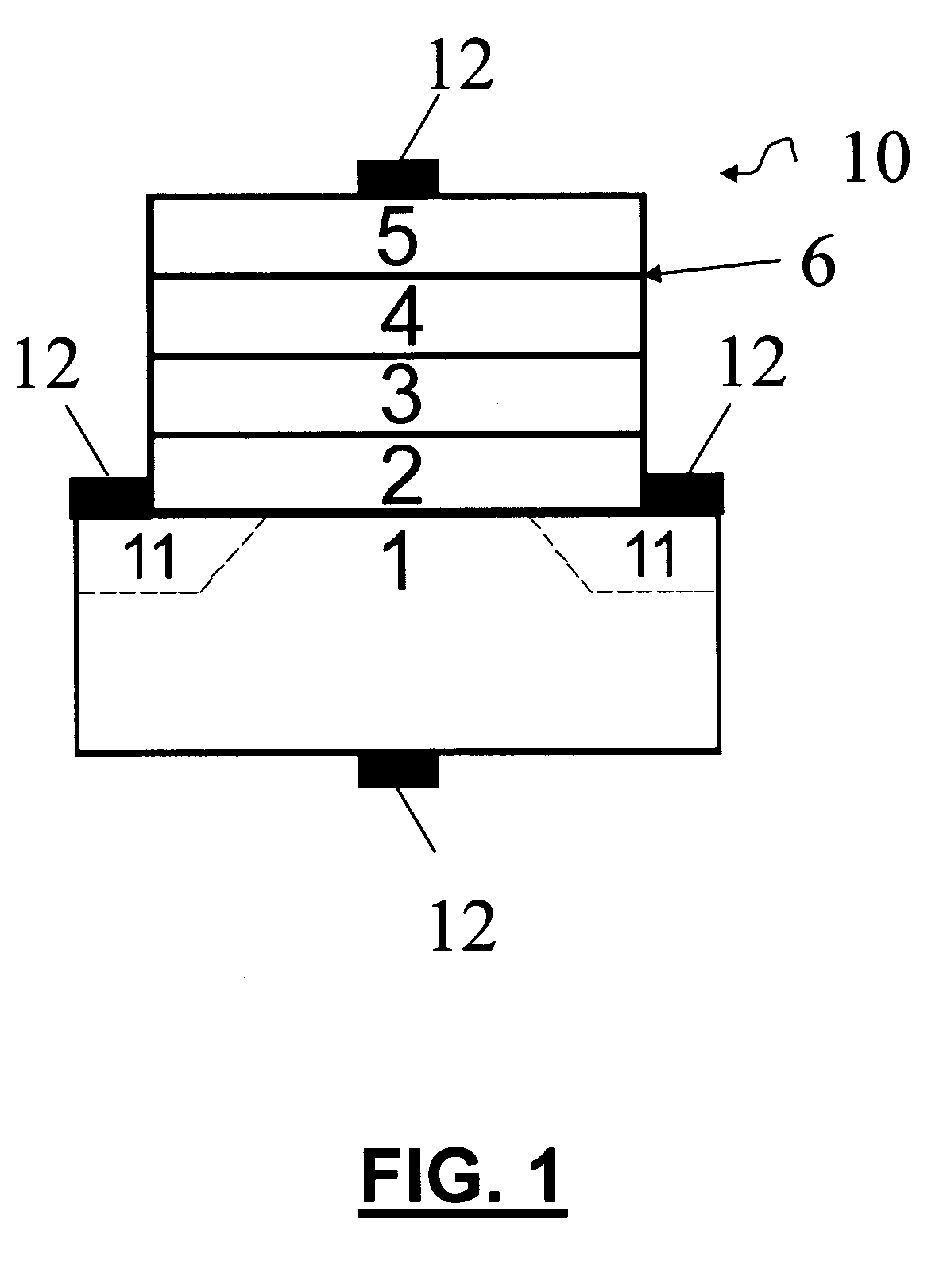

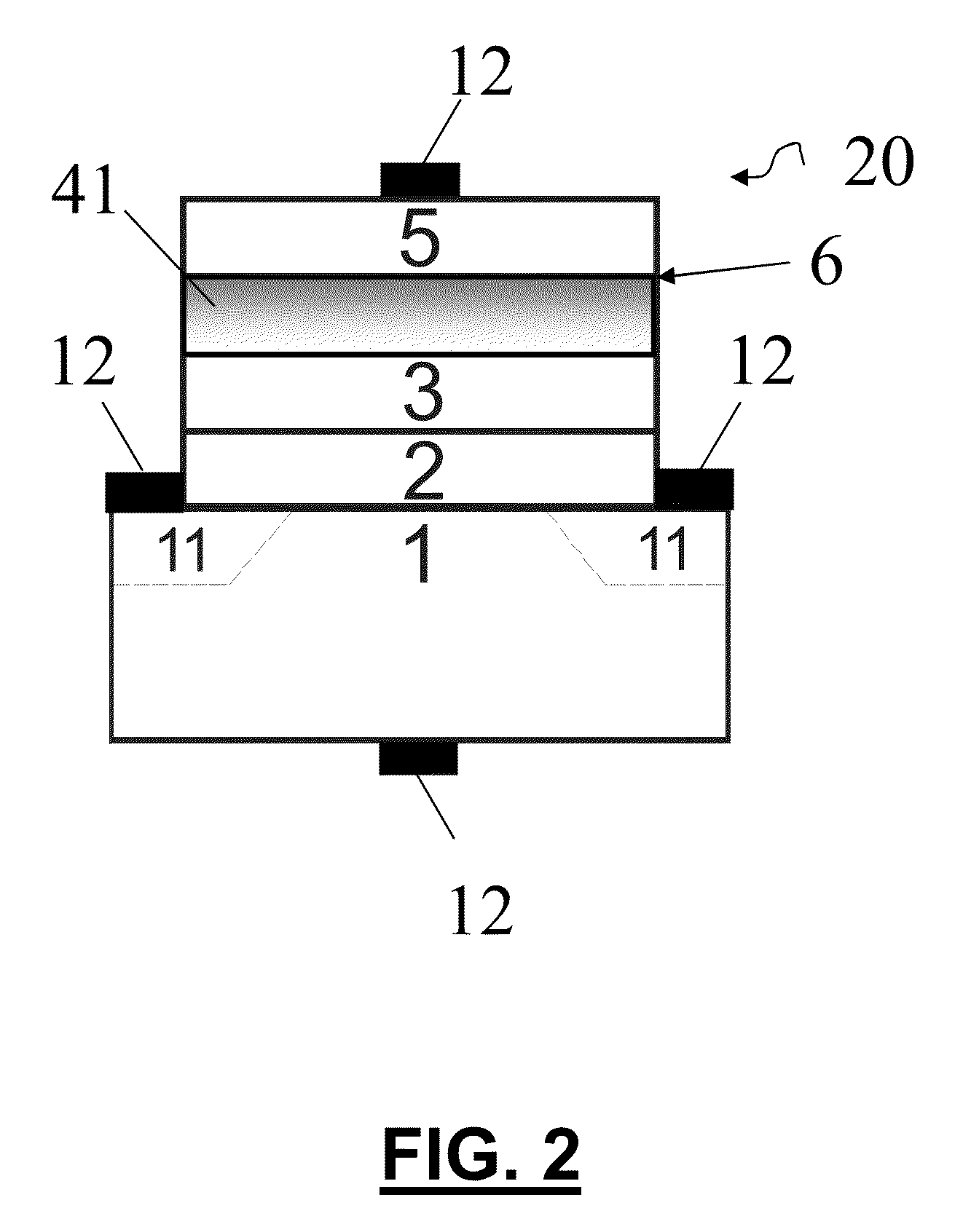

[0020]FIGS. 1-3 show three exemplary embodiments of non-volatile memory cells 10, 20, 30 according to the invention, each comprising a substrate with a channel 1 in between two doped regions 11 (source and drain), a first dielectric 2 on top of the channel 1, a silicon floating gate 3 on top of the insulating layer 2, a second dielectric 4, 41, 42-43 on top of the silicon floating gate 3 and a control gate 5 on top of the second dielectric. The first dielectric is the so-called tunnel dielectric and the second dielectric is the so-called interpoly dielectric. Each of the layers 2-5 may in itself be a single layer or a stack of different layers having substantially the same functionality as the respective single layer which the stack replaces. Contacts 12 are provided at the doped regions 11, at the bottom of the substrate 1 and on top of the control gate 5.

[0021]The embodiments may also be applied in charge trapping non-volatile memory cells in which charge is stored in a charge tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More