Implementing Tamper Resistant Integrated Circuit Chips

a technology of integrated circuit chips and tamper-resistant chips, applied in the field of data processing, can solve the problems of increasing the number of counterfeiting of chip design and processing methods, the inability to adequately protect intellectual property, and the danger of that technology falling into the enemy's hands

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

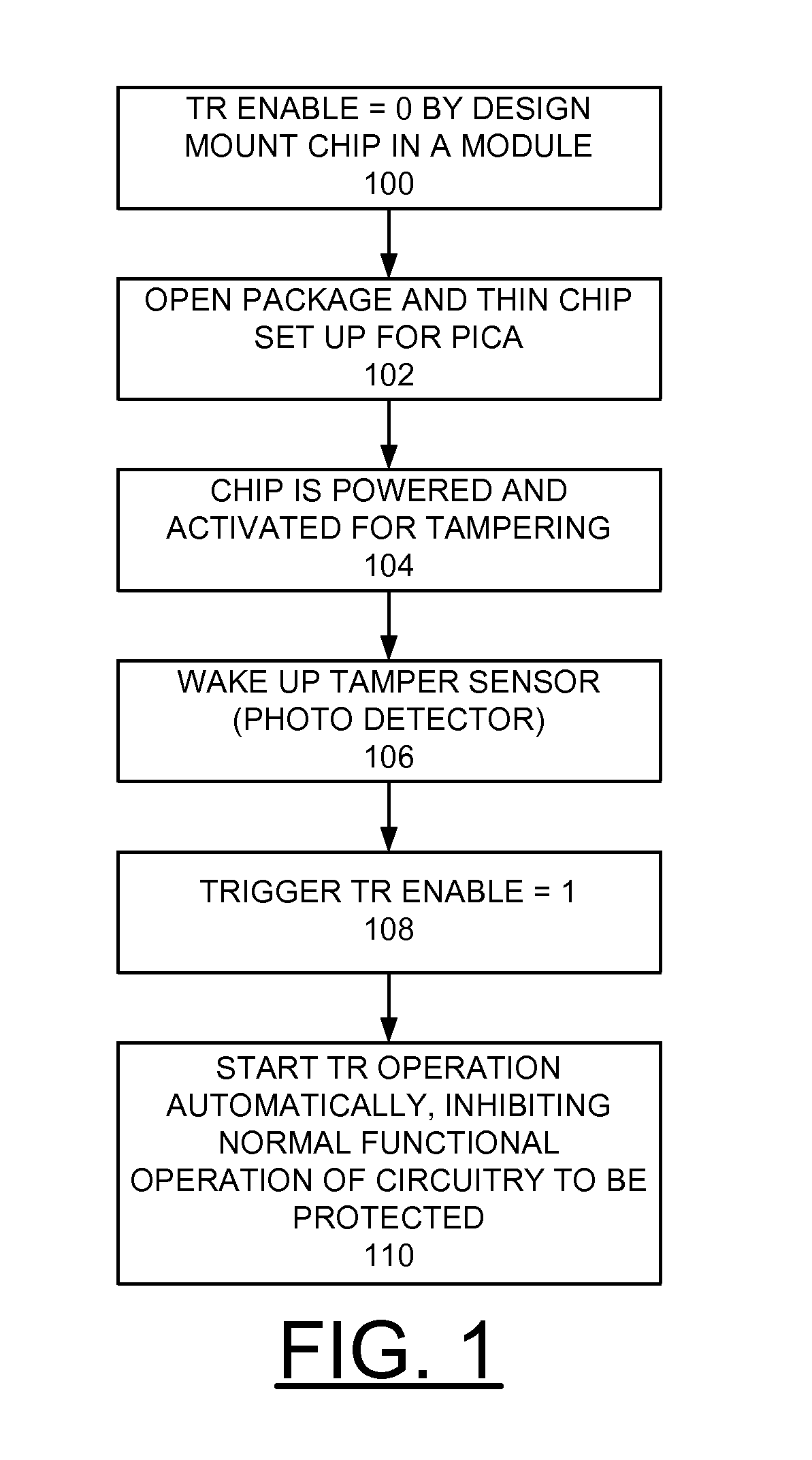

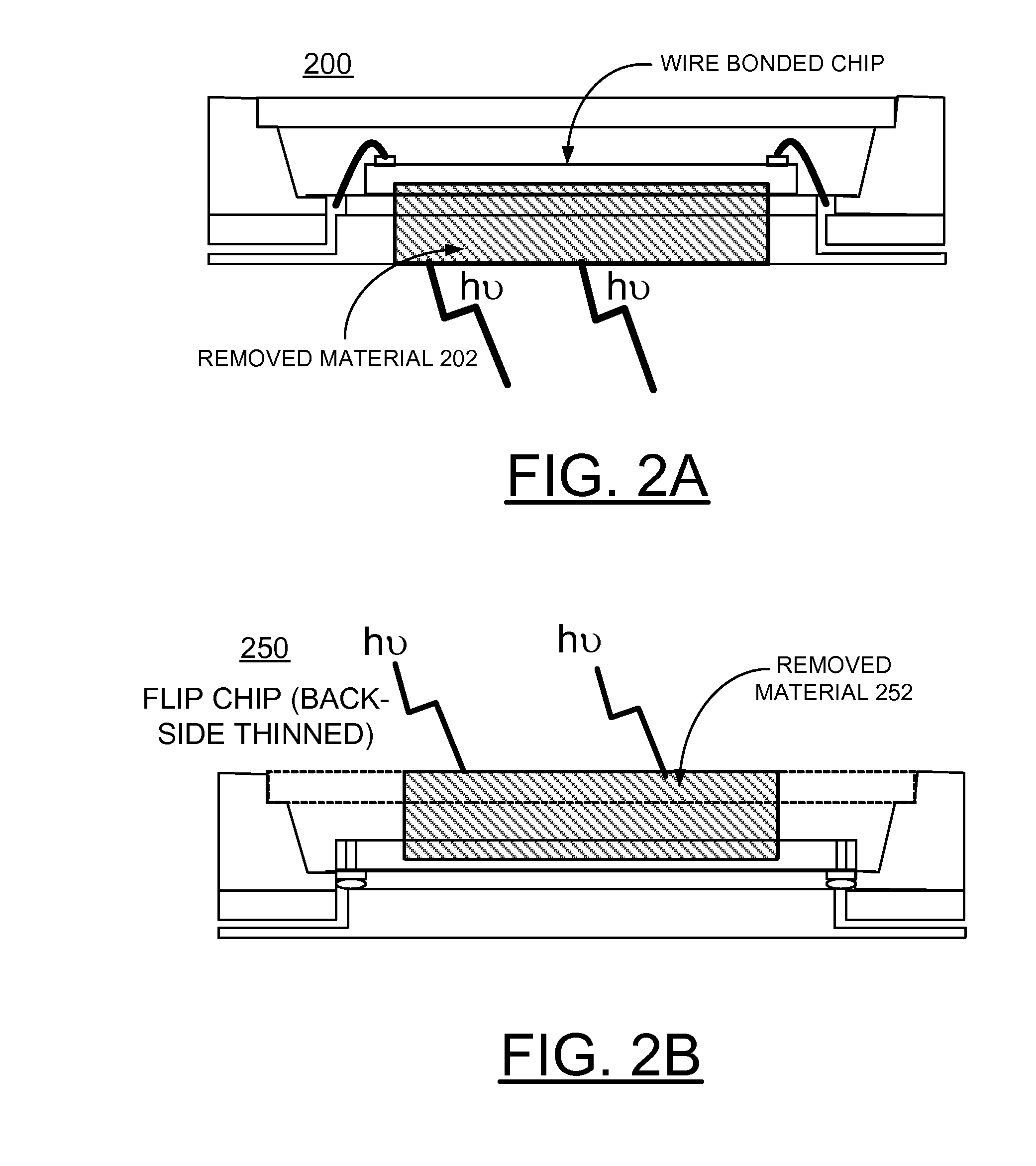

[0032]In accordance with features of the invention, an enhanced method and a tamper resistant circuit for resisting tampering including reverse engineering in a semiconductor chip are provided. The tamper resistant circuit includes three key elements: (1) one or more sensing devices to detect that the package has been opened or removed, (2) generating at least one tamper resistance (TR) enable signal to enable TR operation and (3) disabling at least one circuit block to prevent chip from being fully operational after being tampered.

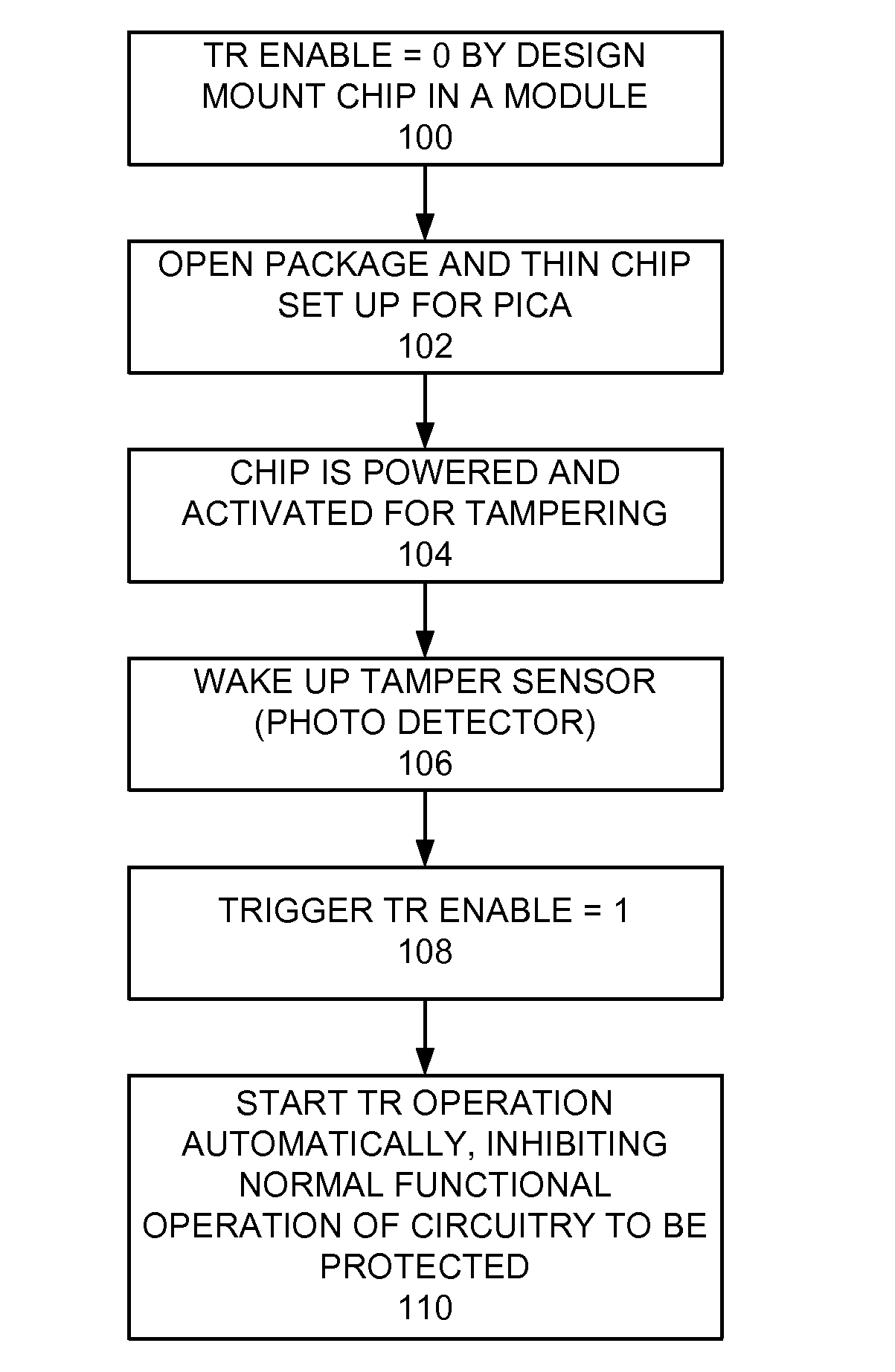

[0033]Having reference now to the drawings, in FIG. 1, there are shown exemplary steps of an anti-tampering method implemented by a tamper resistant circuit for resisting reverse engineering in a semiconductor chip in accordance with the preferred embodiment. A critical point is that the TR operation should not be triggered inadvertently during normal operation. As indicated at a block 100, by default design, the TR enable signal should always be at logic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com