Electrical overstress protection using through-silicon-via (TSV)

a technology of throughsilicon and overstress protection, which is applied in the direction of semiconductor/solid-state device details, diodes, radiation controlled devices, etc., can solve the problems of pn junctions that cannot be blocked in the reverse direction, pn junctions that could eventually reach avalanche breakdown, and catastrophic failure of pn junctions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

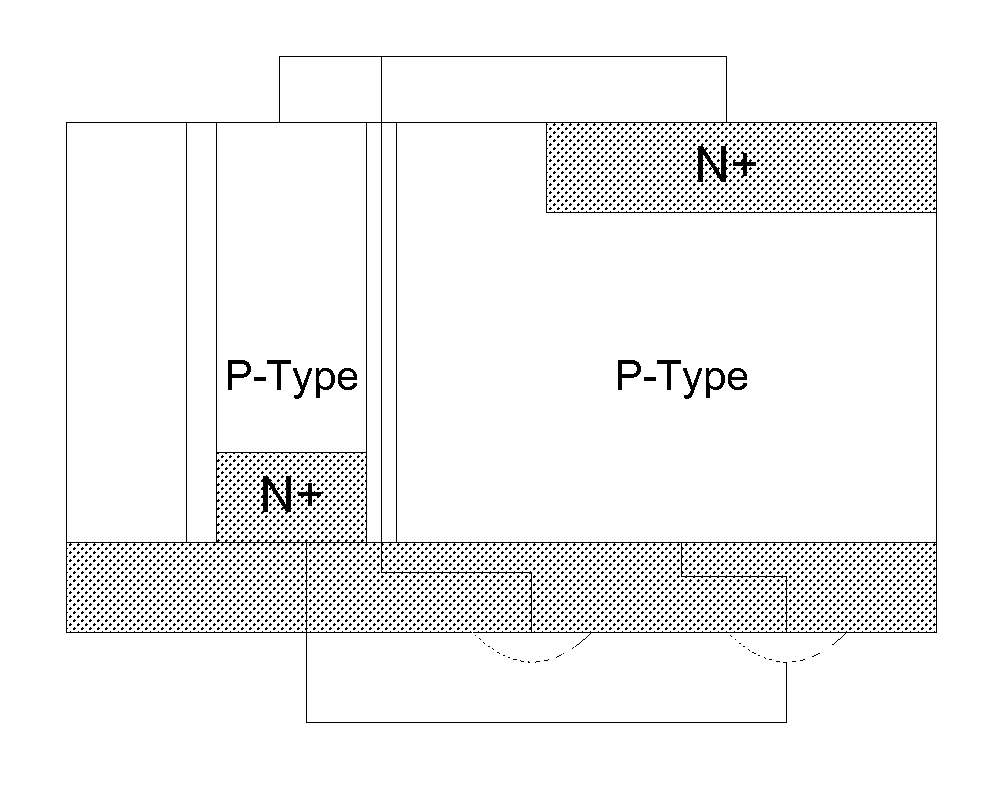

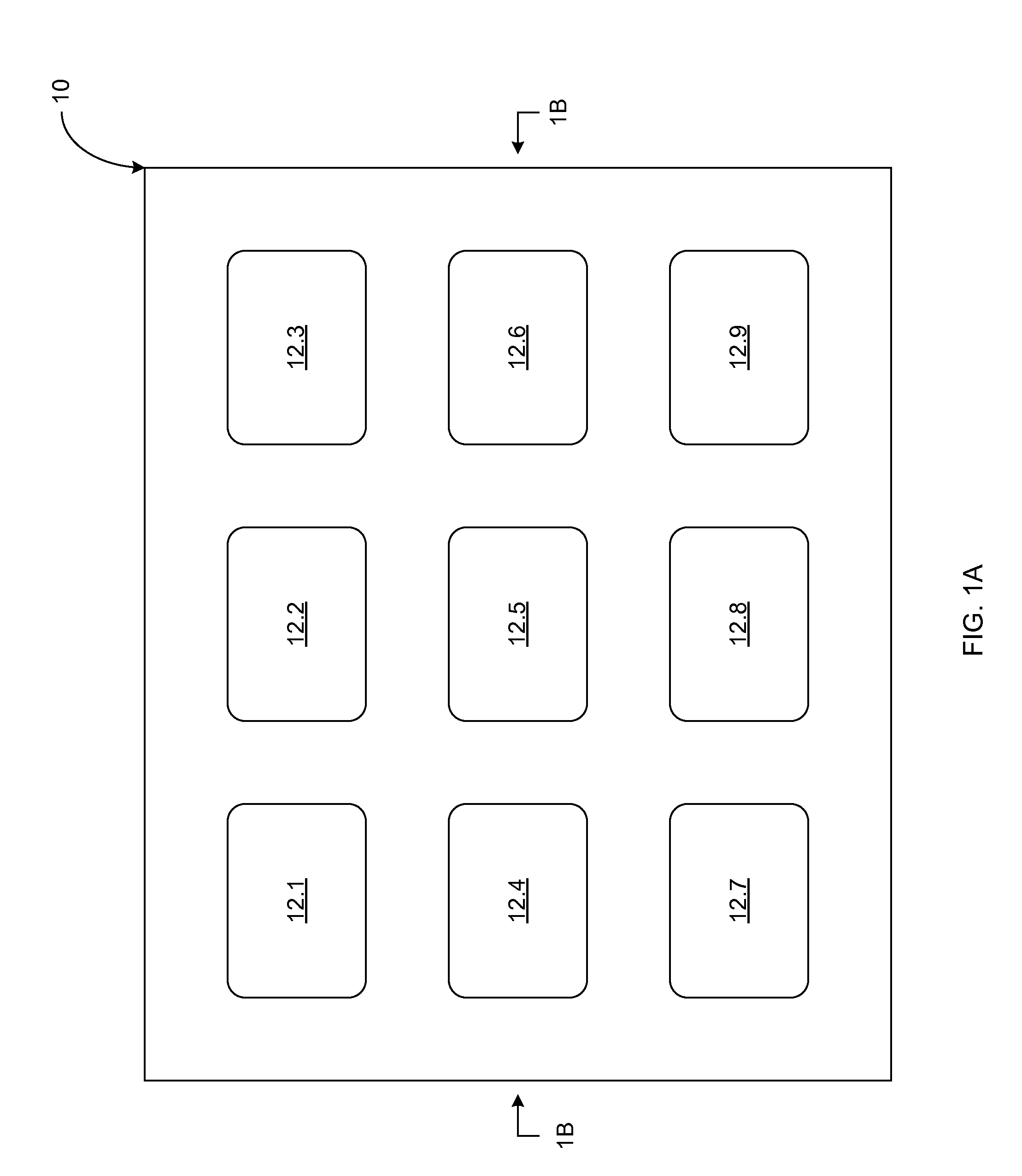

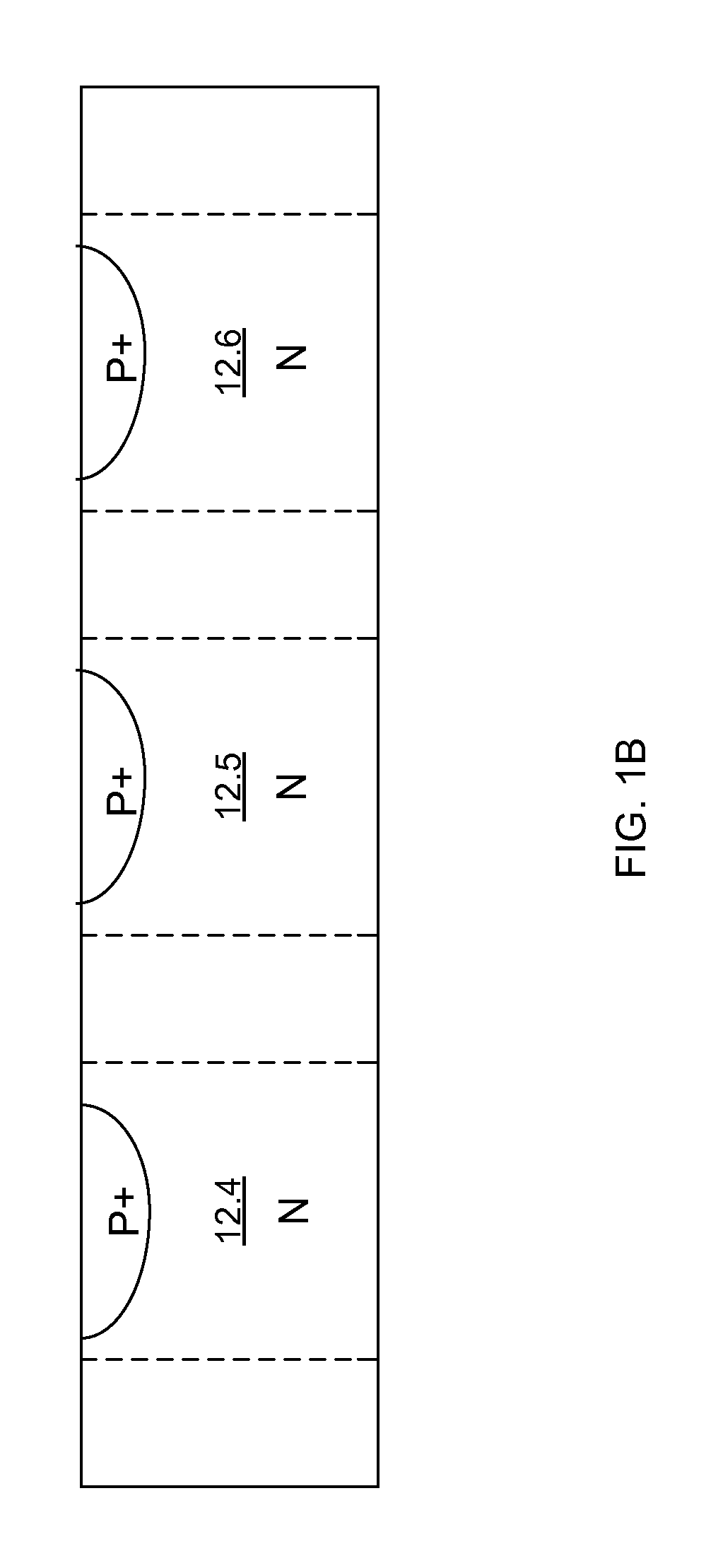

[0012]FIG. 1A illustrates a top view of a photodiode panel 10 that includes a plurality of photodiodes 12.1 to 12.9. FIG. 1B illustrates a cross-sectional view of the photodiode panel 10 as shown in FIG. 1A. Referring to FIGS. 1A and 1B, the photodiode panel 10 may include an N-doped semiconductor substrate on a single die, on which selected regions are implanted with P dopants, so that PN junctions for photodiodes 12.1 to 12.9 may be formed in those regions. The N-doped silicon may be connected to cathodes (not shown), and the P-type silicon may be connected to anodes (not shown). During ESD events, electrical discharges may suddenly appear either in the forward direction (anode-cathode) or in the reverse direction (cathode-anode). The photodiodes in the photodiode panel 10 may accommodate forward voltage stress (anode-cathode). However, the reverse voltage stress (cathode-anode), even at relative low stress level, may cause the photodiode panel to fail catastrophically. Because of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More