High-density and embedded-type capacitor and manufacturing method of the same

A manufacturing method and capacitor technology, which are applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of low capacitance density, difficult to meet high-frequency decoupling, and difficult to meet RF decoupling, etc. The effect of capacitance density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

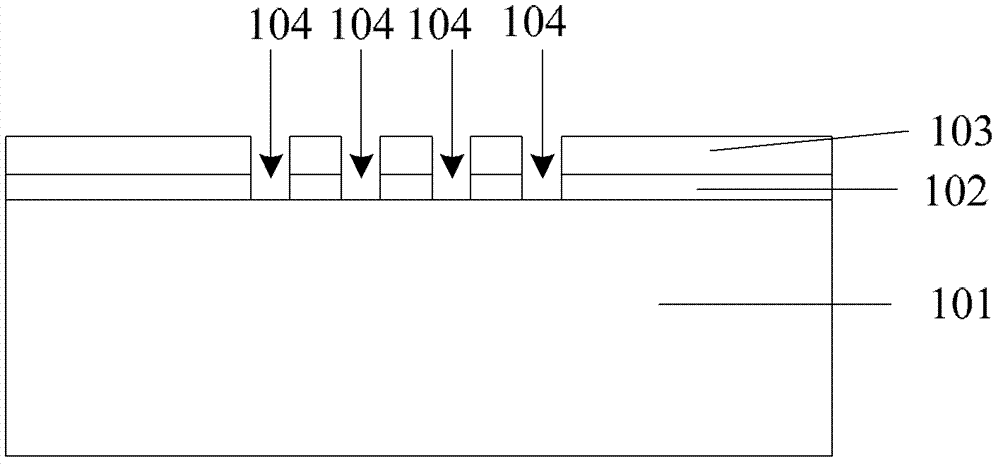

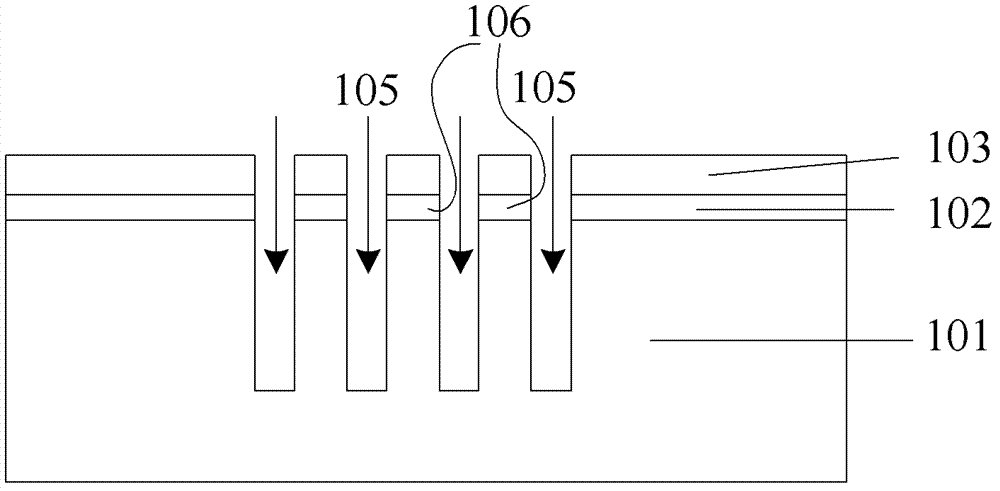

[0039] As mentioned in the background art, the prior art MIMIMI...M structured capacitors are limited by the planar structure, and the capacitance density is small, and it is difficult to meet the requirements of high-frequency decoupling. In other words, the capacitors in the prior art have a small capacitance density, and it is difficult to simultaneously apply to high-frequency and low-frequency use environments, that is, it is difficult to meet the requirements of low-frequency decoupling and high-frequency decoupling at the same time.

[0040] Based on the above reasons, the inventor considers that if a capacitor can meet the requirements of low-frequency decoupling and high-frequency decoupling at the same time, the capacitance density of the capacitor must be increased. To achieve this goal, it can be considered from the perspective of three-dimensional packaging. The three-dimensional structure is introduced into the capacitor structure, that is, the capacitor is changed f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More