Fabricating a semiconductor die having coefficient of thermal expansion graded layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015]Example embodiments are described with reference to the drawings, wherein like reference numerals are used to designate similar or equivalent elements. Illustrated ordering of acts or events should not be considered as limiting, as some acts or events may occur in different order and / or concurrently with other acts or events. Furthermore, some illustrated acts or events may not be required to implement a methodology in accordance with this disclosure.

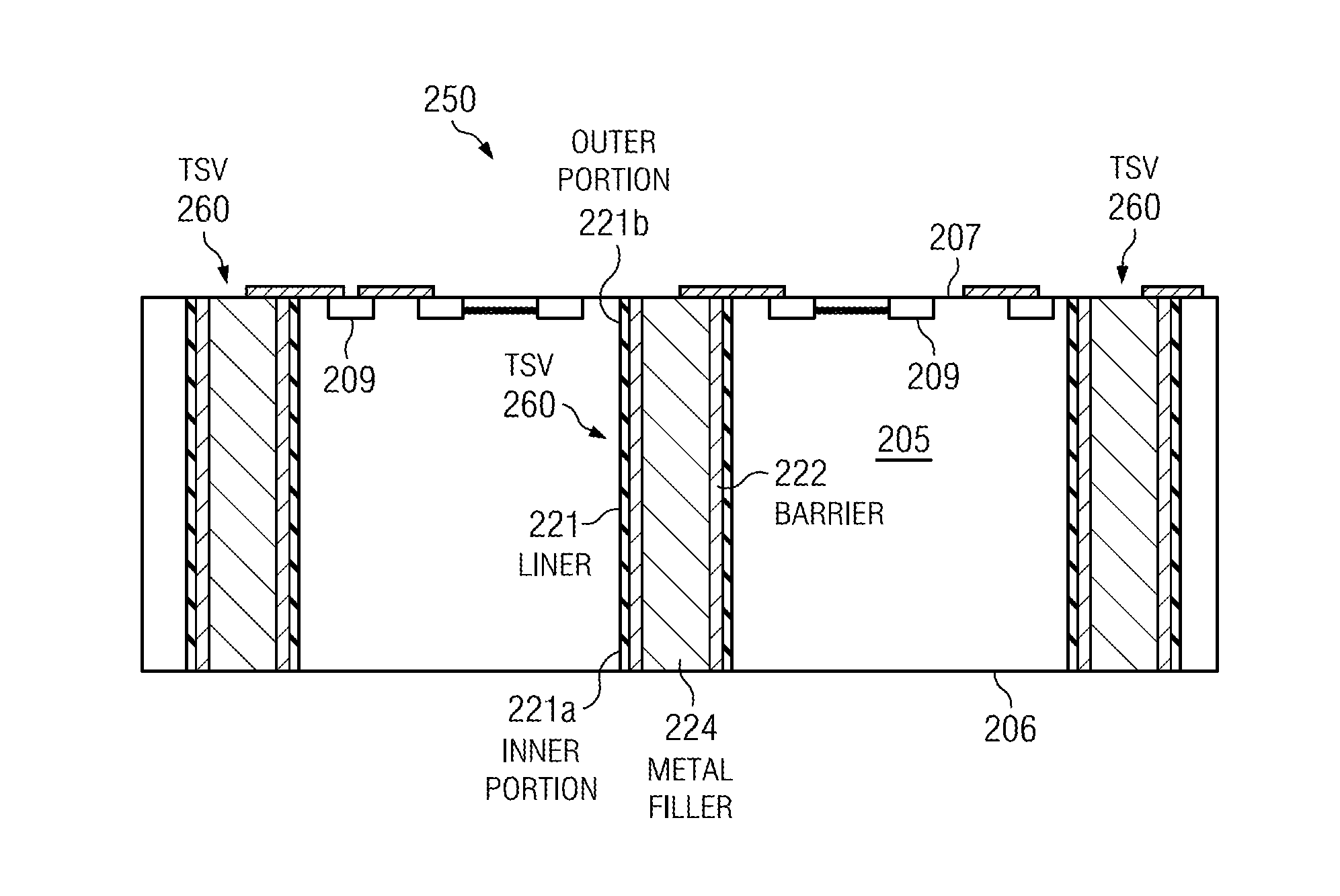

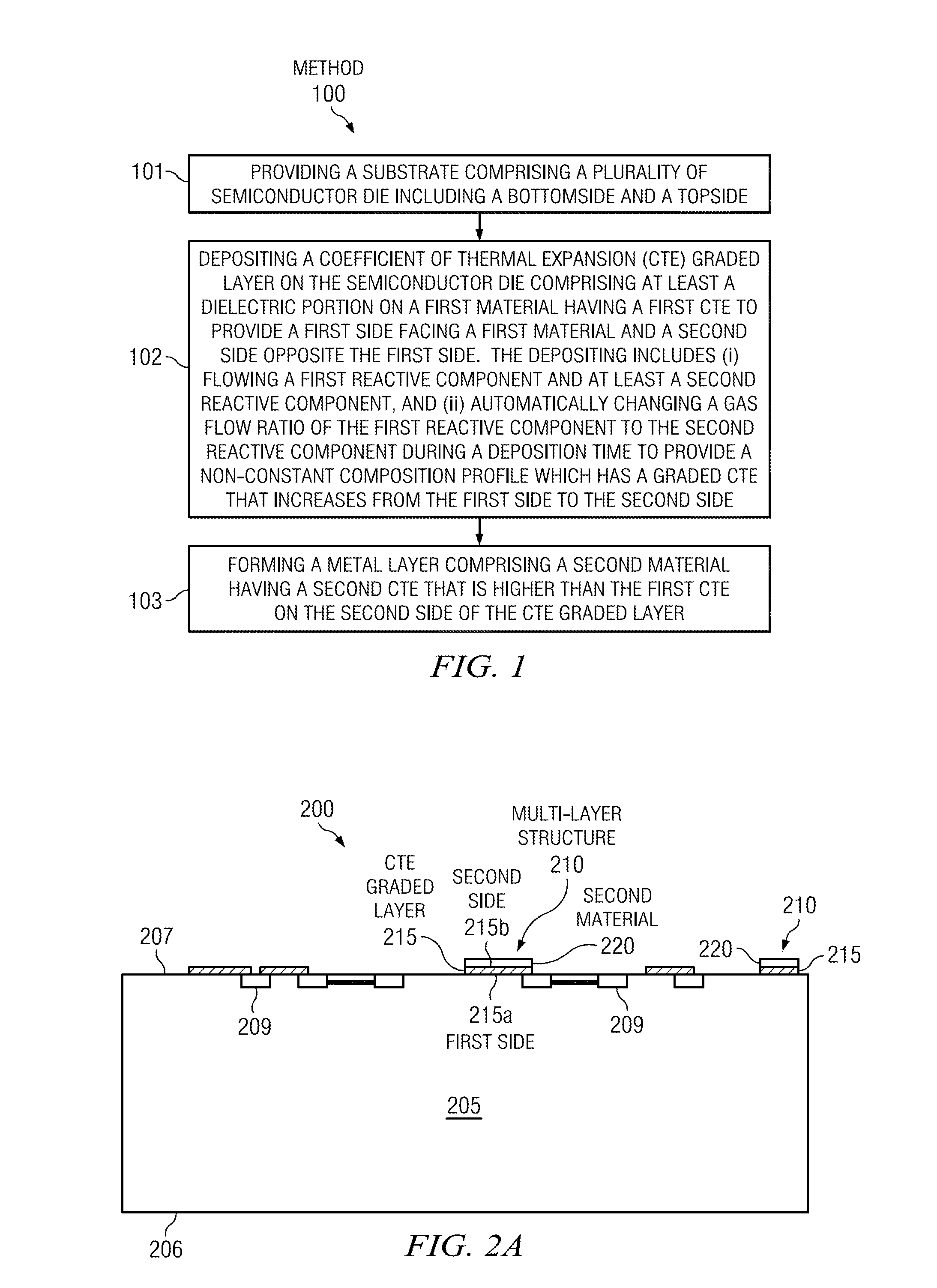

[0016]Disclosed embodiments include methods of fabricating a semiconductor die including disclosed CTE graded layers. FIG. 1 is a flow chart showing steps in an example method 100 of forming semiconductor die having multi-layer structures including disclosed CTE graded layers, according to an example embodiment. Step 101 comprises providing a substrate (e.g., a wafer) comprising a plurality of semiconductor die including a bottomside and a topside. Once method 100 and the other fabrication steps are completed, the topside will inc...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap