Stacked wafer structure and fabricating method thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

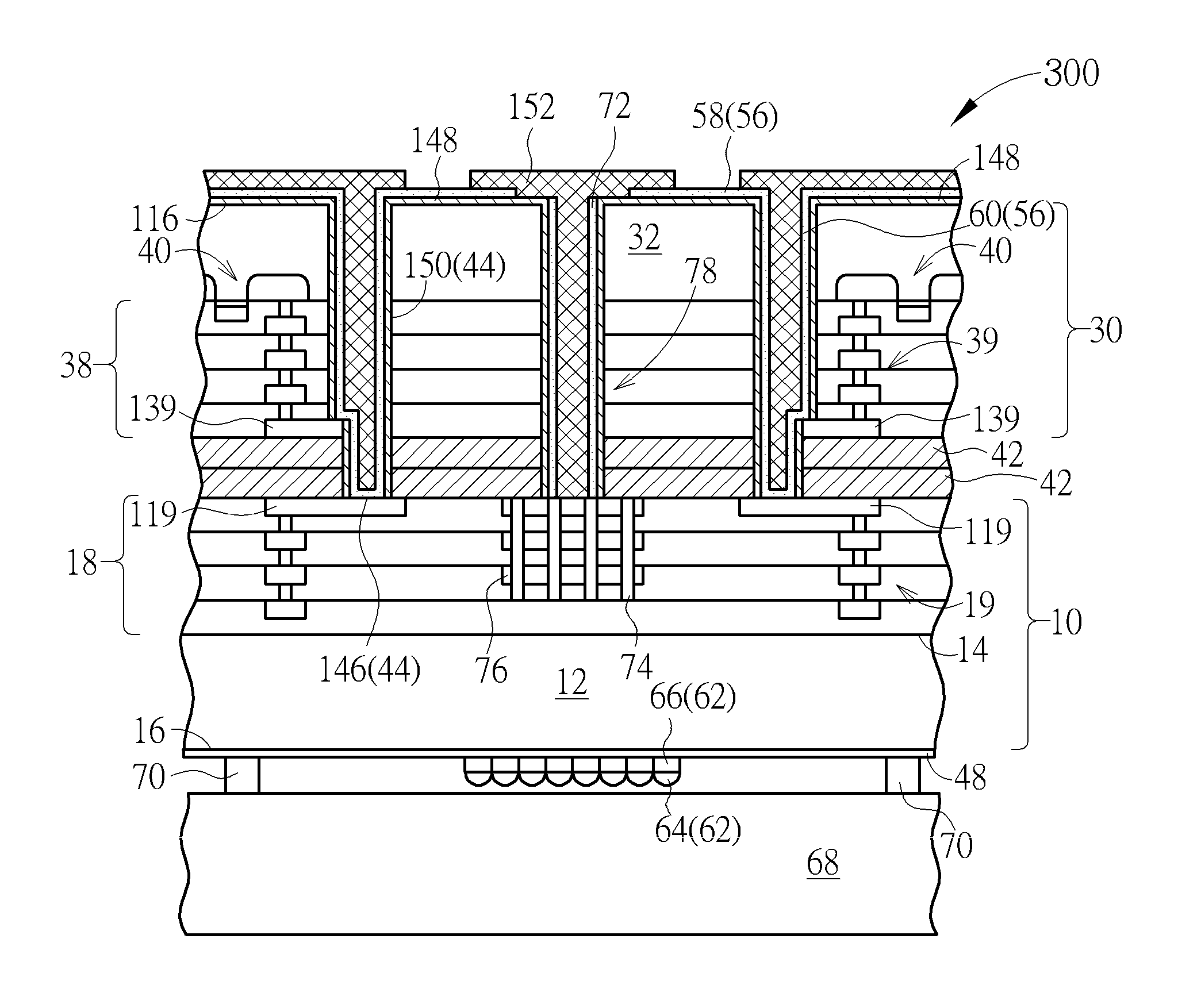

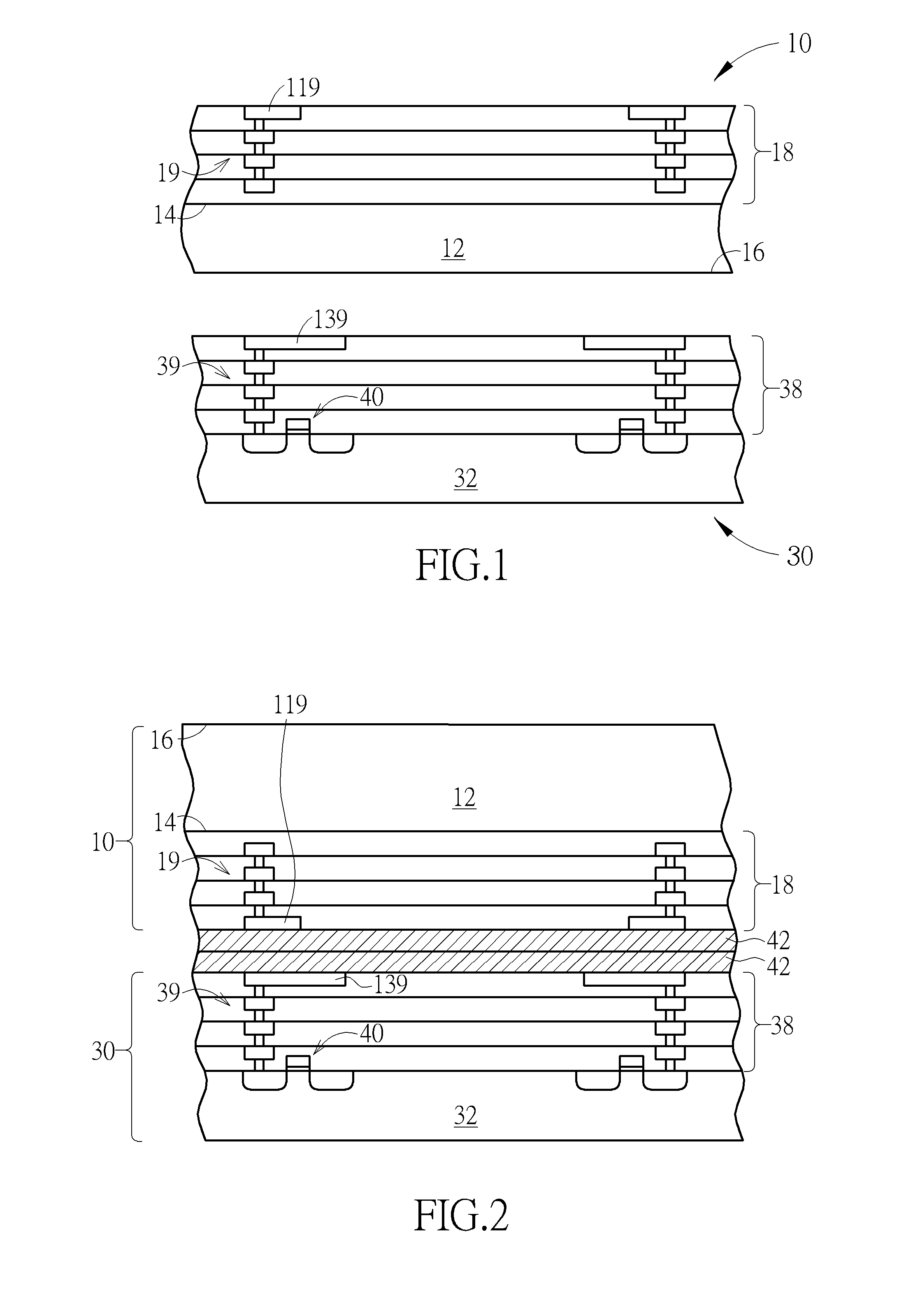

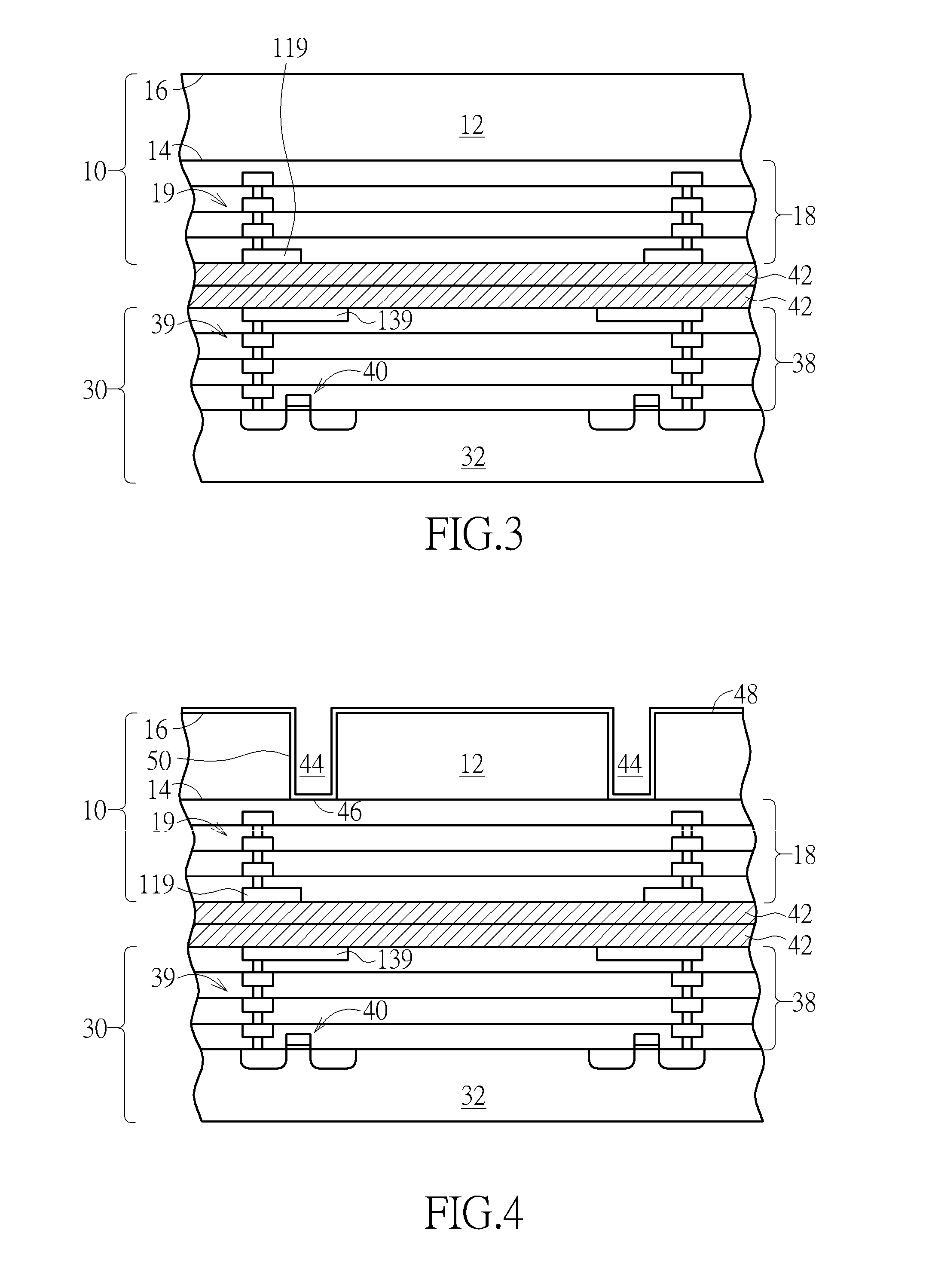

[0016]FIGS. 1 to 7 are schematic cross-sectional diagrams of fabricating a stacked wafer structure at various stages according to a first preferred embodiment of the present invention. It is understood that FIGS. 1 to 7 have been simplified for a better understanding of the inventive concepts of the present disclosure and may not be drawn to scale.

[0017]With reference to FIG. 1, a CMOS image sensors (CIS) wafer 10 and an image signal processor (ISP) wafer 30 are provided. The CIS wafer 10 includes a CIS substrate 12 having a front side 14 and a back side 16, an interlayer dielectric layer 18 disposed on the front side 14 of CIS substrate 12, at least one set of conductive stack 19 disposed within the interlayer dielectric layer 18. The conductive stack 19 may include numerous metal vias and pads. The upmost layer of the conductive stack 19 defined as a last metal 119 which is exposed through the interlayer dielectric layer 18 and often serves as a bonding pad. The front side 14 of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More