Hv converter with reduced EMI

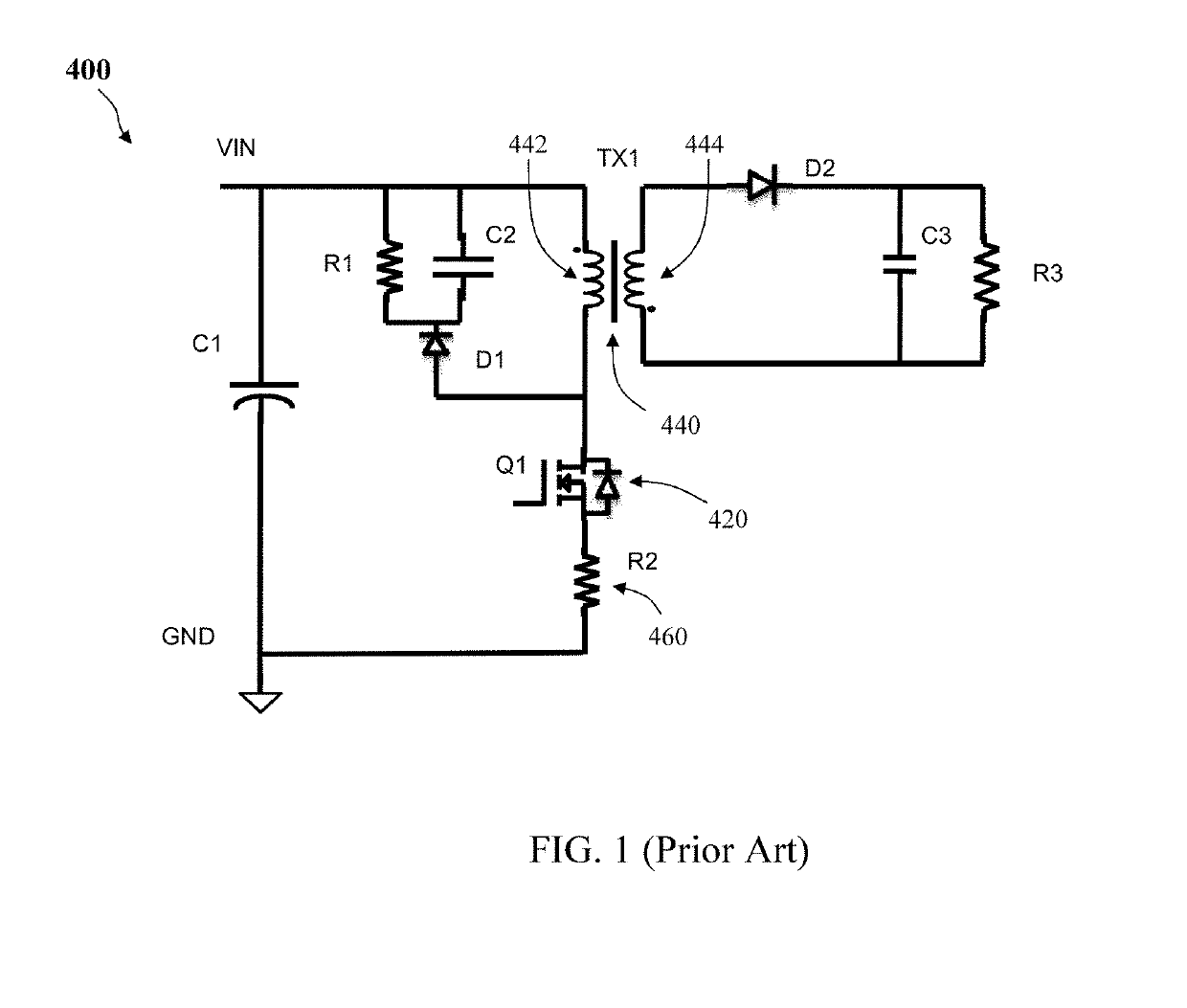

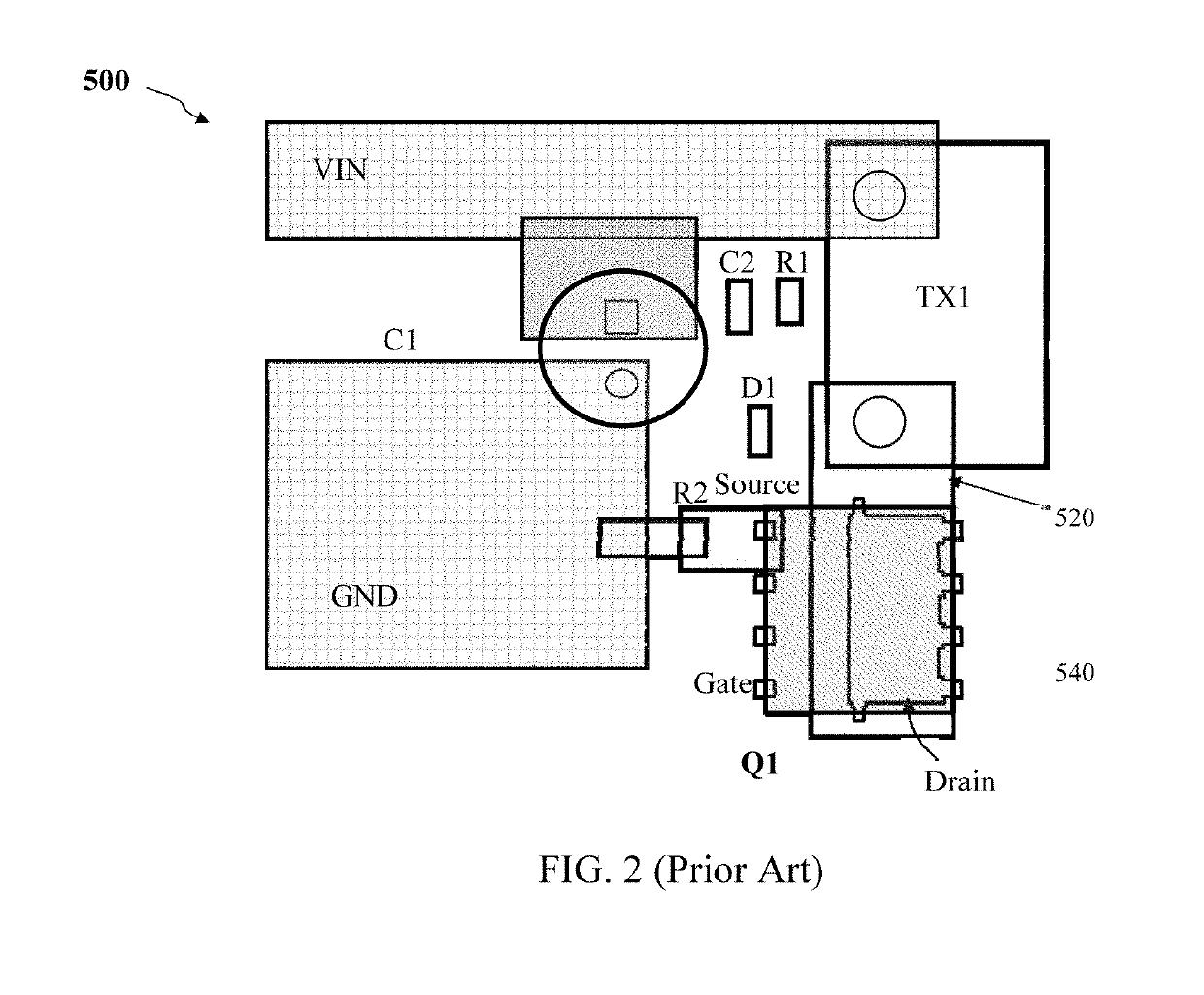

a converter and emi technology, applied in the field of high voltage converters, can solve the problems of high emi noise and inability to optimize the pcb layout b>500/b>, and achieve the effect of minimizing electromagnetic interference (emi) noise and facilitating cooling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

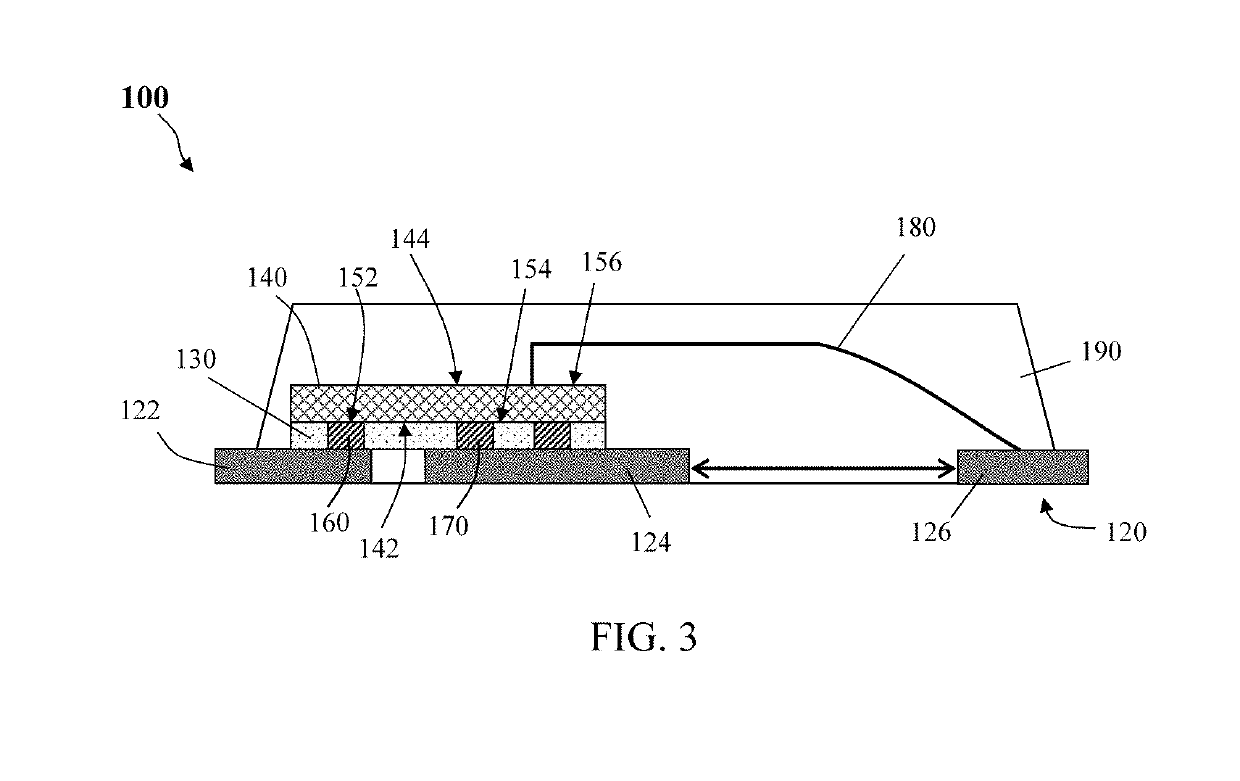

[0018]FIG. 3 is a cross sectional view of a double-diffused metal-oxide semiconductor (DMOS) package 100 in examples of the present disclosure. The DMOS package 100 includes a lead frame 120, an insulation material 130, a main DMOS chip 140, a first plurality of metal bumps 160, a second plurality of metal bumps 170, a wire 180 and a molding encapsulation 190. The lead frame 120 includes a gate section 122, a source section 124 and a drain section 126. To achieve thermal performance and to reduce EMI noise, in one example, the source section 124 accounts for more than 50% of the bottom surface area of the DMOS package 100. In another example, the source section 124 accounts for more than 70% of the bottom surface area of the DMOS package 100. In still another example, the source section 124 is 10 times in size of the drain section 126. The main DMOS chip 140 has a gate electrode 152 and a source electrode 154 disposed on a first surface 142 of the main DMOS chip 140 and a drain elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More