Combinational circuit, and encoder, decoder and semiconductor device using this combinational circuit

a combinational circuit and encoder technology, applied in the field of combinatorial circuits, can solve the problems of increasing the inappropriateness of the conventional method of low-speed serial reed-solomon decoders arranged in parallel, reducing the processing speed, and reducing the processing cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066]The preferred embodiment of the present invention will now be described by referring to the accompanying drawings. Note, however, that the present invention is not limited to this embodiment.

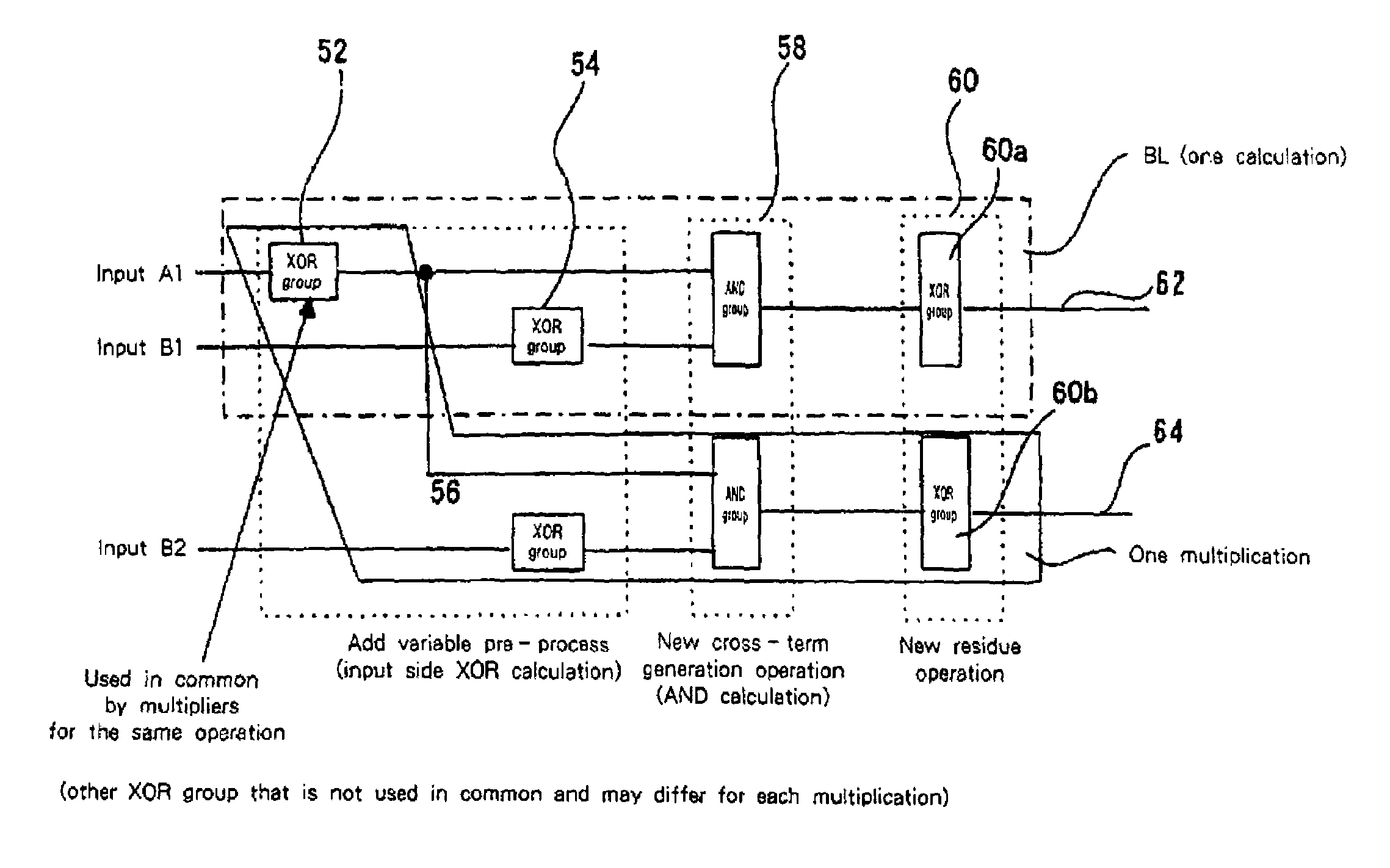

[0067]Section 1 Decoding Circuit

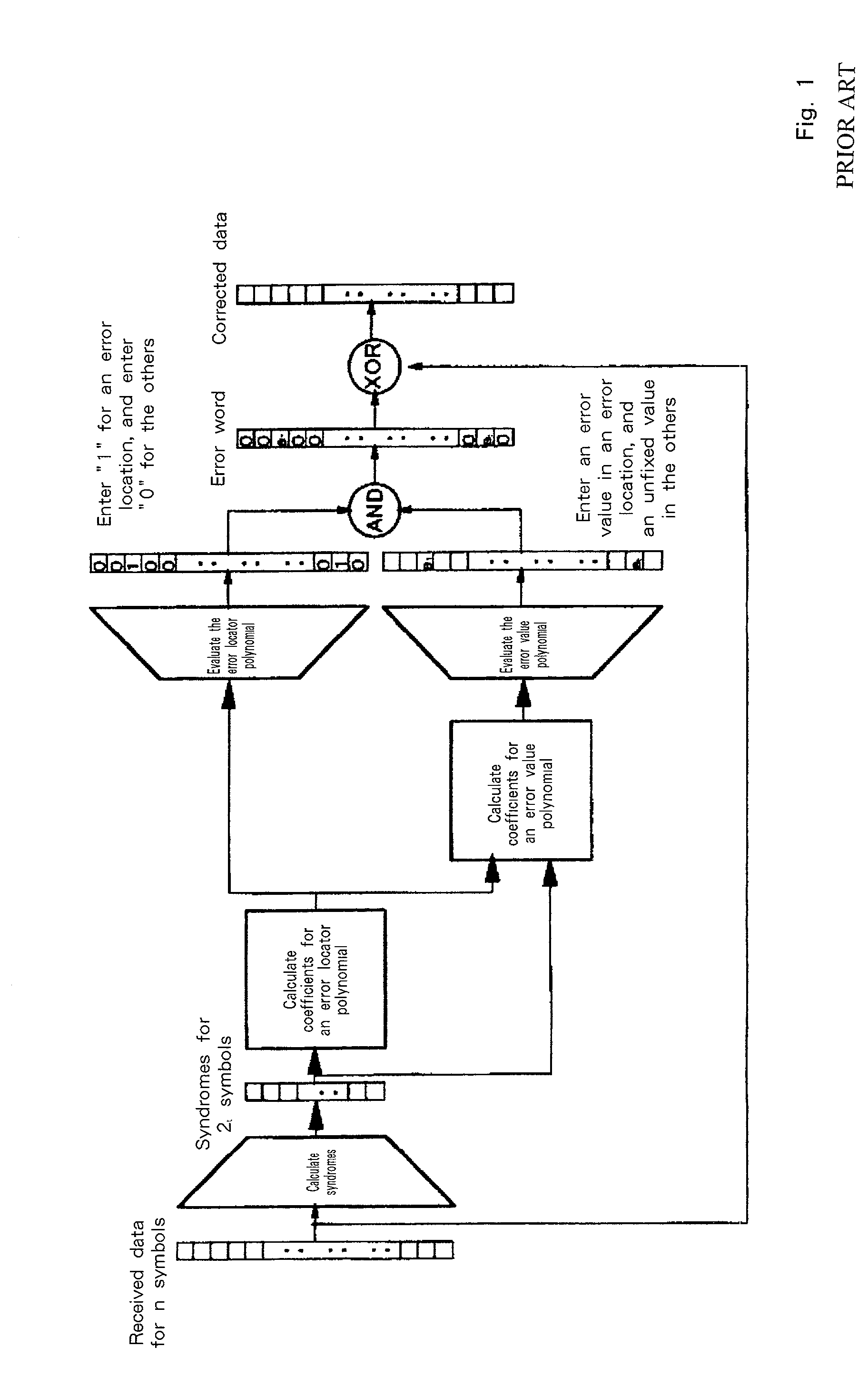

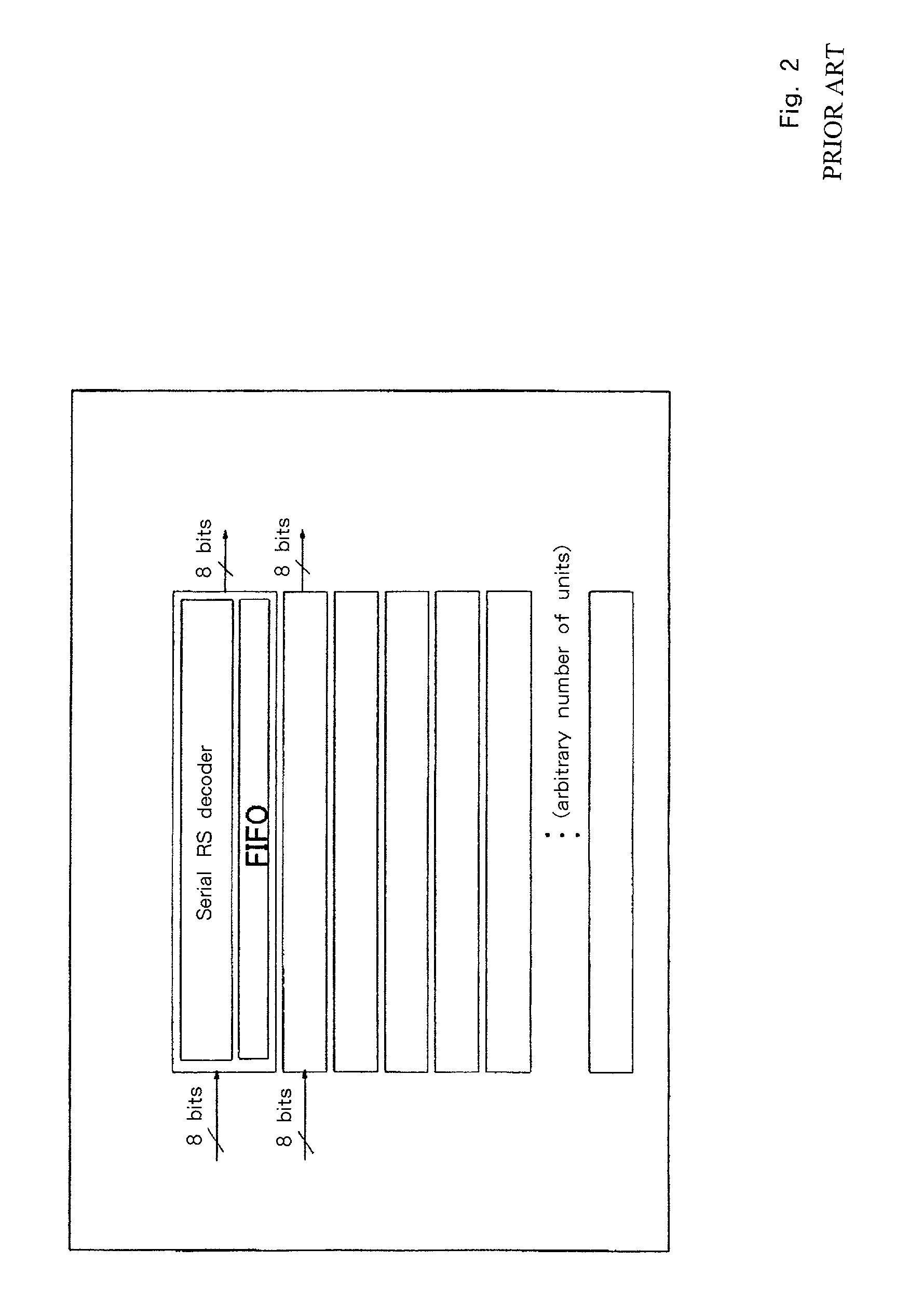

[0068]FIG. 6 is a diagram showing a decoder according to the present invention that can be used to correct errors in digital signals received through optical communication. The decoder in FIG. 6 includes an input unit 10, a processor 12 and an output unit 14. The input unit 10 receives a 16-byte interleaved digital signal ID. The processor 12 processes a signal received from the input unit 10 and calculates coefficients of an error locator polynomial and coefficients of an error value polynomial. And the output unit 14 obtains an AND of the Λ(x) evaluation result and Er(x) evaluation result that are generated from the data received from the processor 12, performs an XOR process with the AND result and the input digital signal ID, and generates a digital sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More