Dual-node capacitor coupled MOSFET for improving ESD performance

a mosfet transistor and dual-node technology, applied in the direction of pulse automatic control, pulse technique, semiconductor devices, etc., can solve the problems of gate electrode damage, ic chip damage, oxide layer, etc., and achieve the effect of improving the uniform turn-on of a multi-finger mosfet transistor and lowering the trigger voltag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

The present invention improves over conventional gate-coupling and well-coupling techniques in that the embodiments provide a lower trigger voltage for each MOSFET in the multi-finger MOSFET device, while improving the turn-on consistency for each MOSFET. Note that, although the present invention is particularly well suited to a multi-finger MOSFET ESD protection device, the present invention may also be employed in a single MOSFET device while providing stellar results.

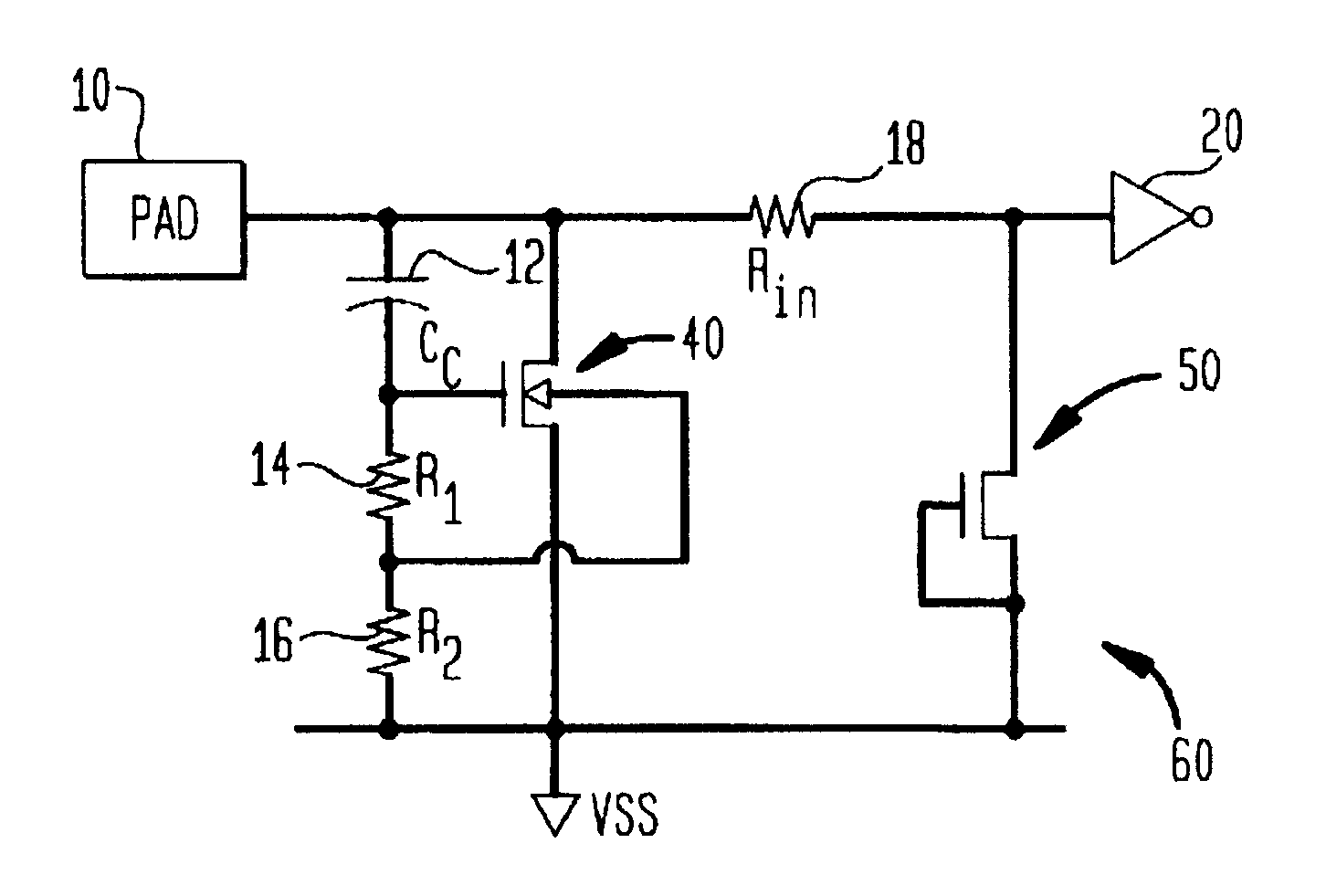

FIG. 6 shows an ESD protection device 60 having a dual-node capacitor in accordance with a first embodiment of the present invention. Protection device 60 is positioned between an IC pad terminal 10 and a buffer 20 that connects to an internal circuit (not shown) to be protected from an ESD event.

Device 60 includes a primary protection circuit that includes MOSFET 40, capacitor 12, and first and second resistors 14, 16, respectively. Illustratively, MOSFET 40 is an NMOS transistor but as previously discussed, may be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More