Calibration of isolated analog-to-digital converters

an analog-to-digital converter and calibration technology, applied in the field of analog-to-digital converter calibration, can solve the problems of difficult calibration of adc, inability to provide each adc with a precise reference, and gain and offset of individual channels, so as to eliminate the effects of drift in the different channels and eliminate the effect of selected gain and offset effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

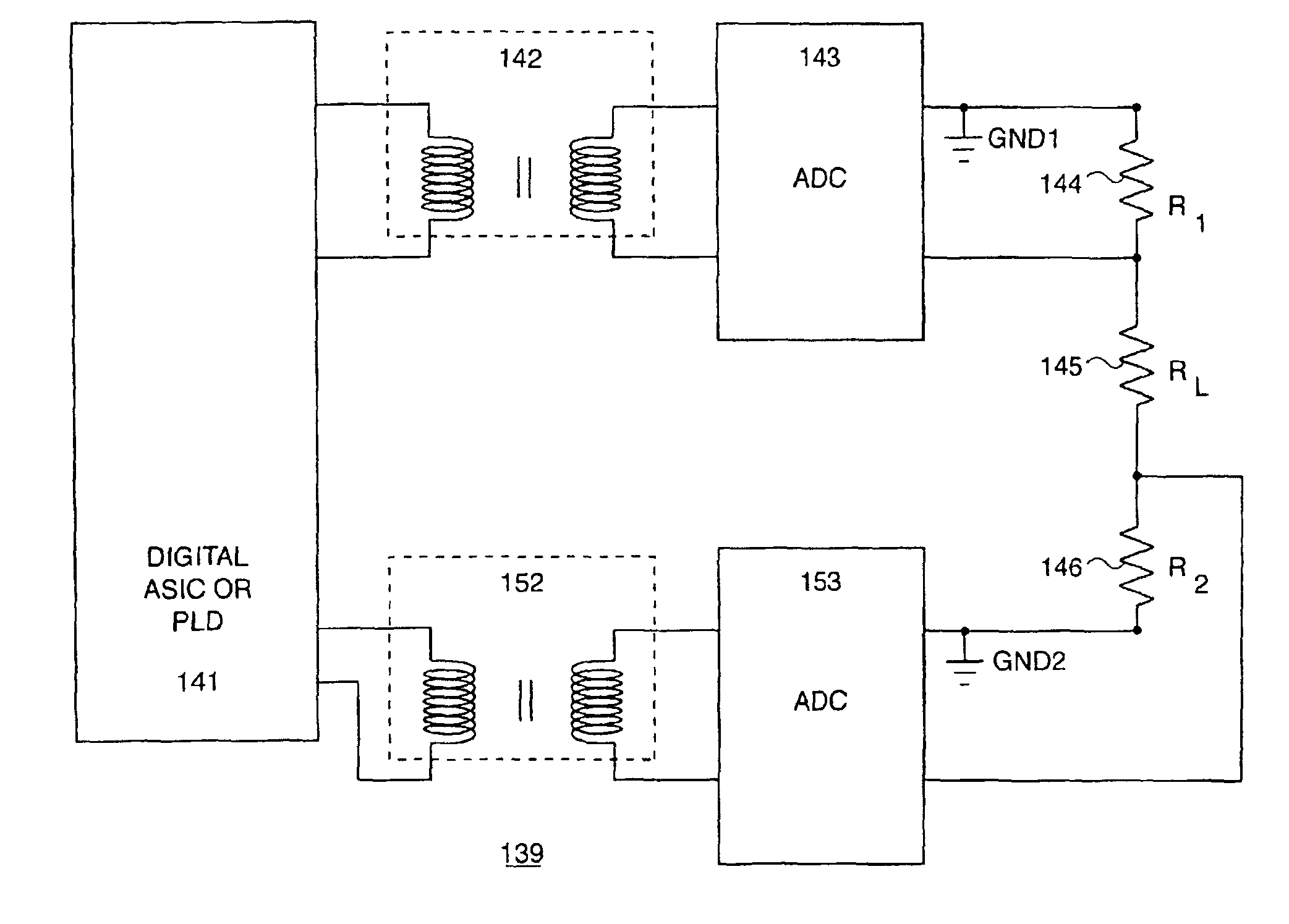

[0029]Referring now to FIG. 3, there is known a block diagram of a two channel isolated analog-to-digital converter system 139, wherein the analog-to-digital converter 143 and 153 are isolated from the microprocessor or programmable logic device 141 by first and second transformers 142 and 152, respectively.

[0030]System 139 includes a microprocessor or programmable logic device 141 which is coupled to first and second analog-to-digital converters 143 and 153 through respective first and second transformers 142 and 152. A current limiting / isolating resistor RL 145 may limit overall current and isolate the two calibration resistors R1, 144 and R2 146 from one another. First and second calibration resistors R1 144 and R2 146 may be coupled to the outputs of analog-to-digital converters 143, and 153, respectively.

[0031]First and second analog-to-digital converters 143, and 153 may be referenced to respective local grounds GND1 and GND2, which may be at very different potentials. In norm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More