Junction field effect transistor

A field effect transistor and junction gate technology, which is applied in the field of microelectronic semiconductors, can solve the problem of device size gate oxide, the thermal electron effect cannot be effectively solved, etc., and is suitable for large-scale integration, cost saving, and good heat dissipation efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Specific implementation examples

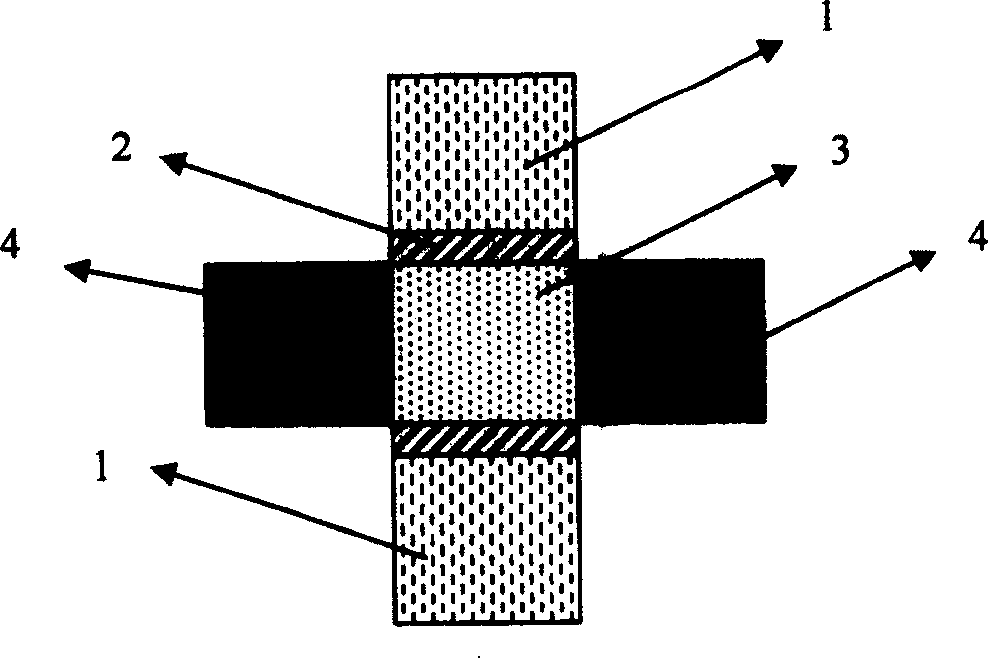

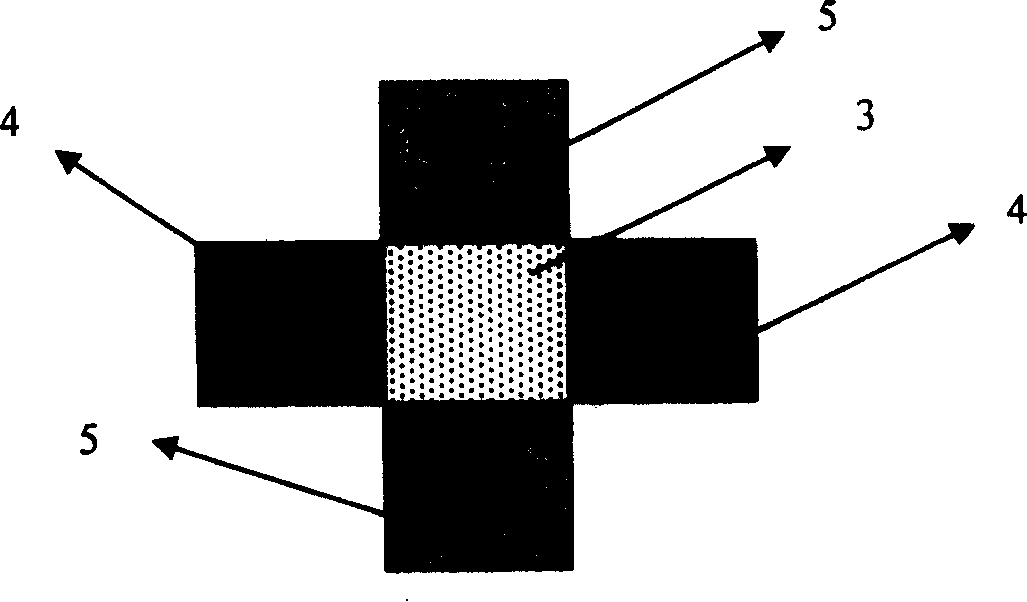

[0021] refer to figure 2 , the dual gate junction gate field effect transistor of the present invention comprises: source region 4, drain region 4, double control gate 5 and body 3, body 3 is square, control gate 5 is doped monocrystalline silicon, control gate and body are directly connected Form a P-N junction, the body is a square. It can be seen from the figure that the dual-gate junction gate field effect transistor of the present invention is a completely symmetrical structure, so as long as the connecting electrodes between the control gate and the source and drain are changed, the n-type double gate junction gate field effect transistor and the p-type double gate field effect transistor.

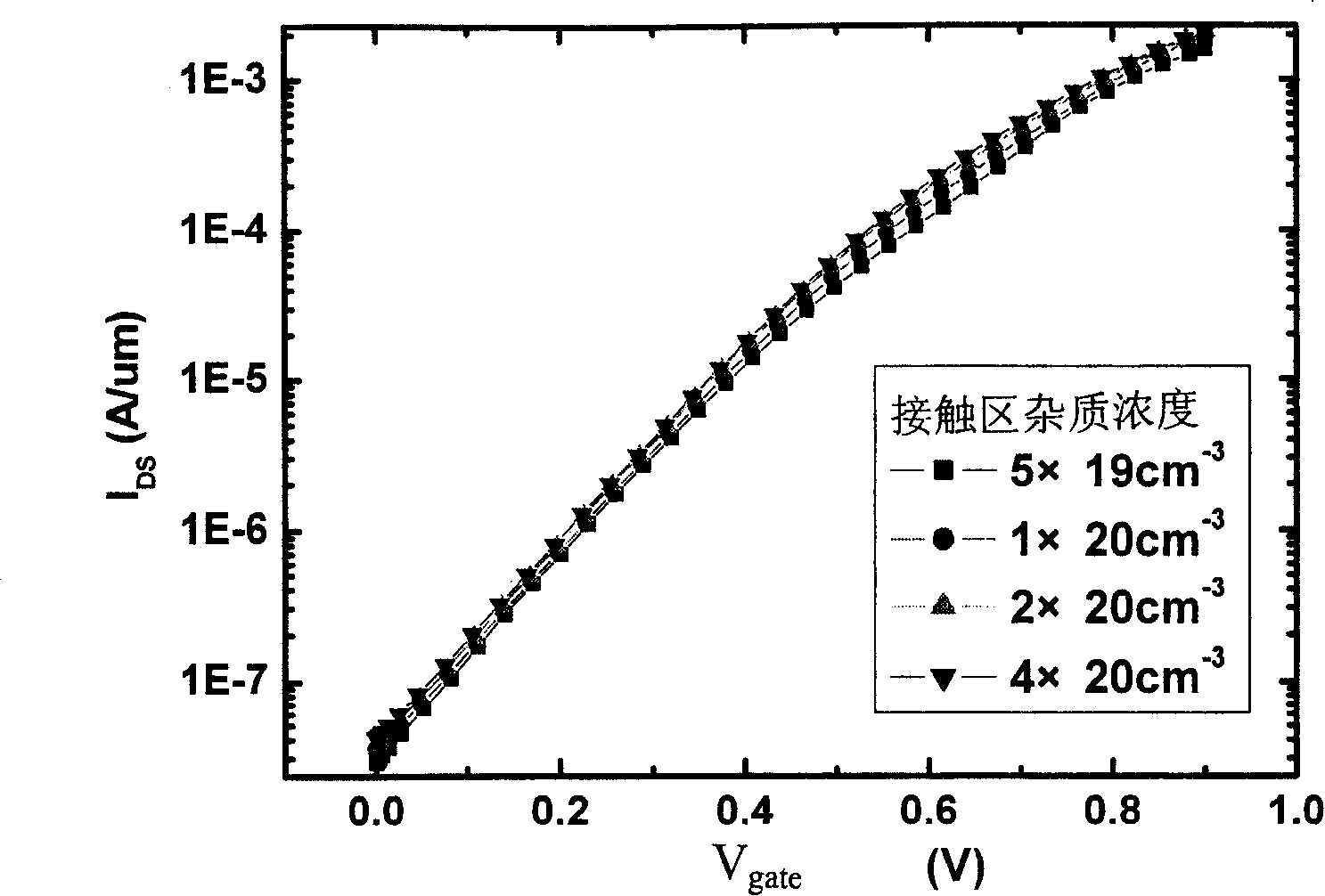

[0022] The specific implementation example of the double-gate junction gate field effect transistor of the present invention, taking the side length of the body as an example, its specific design structural parameters are as follows: the l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More