Forming method of shallow plow groove isolation structure

An isolation structure, shallow trench technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to reduce stress levels, optimize performance, and improve substrate surface stress levels

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

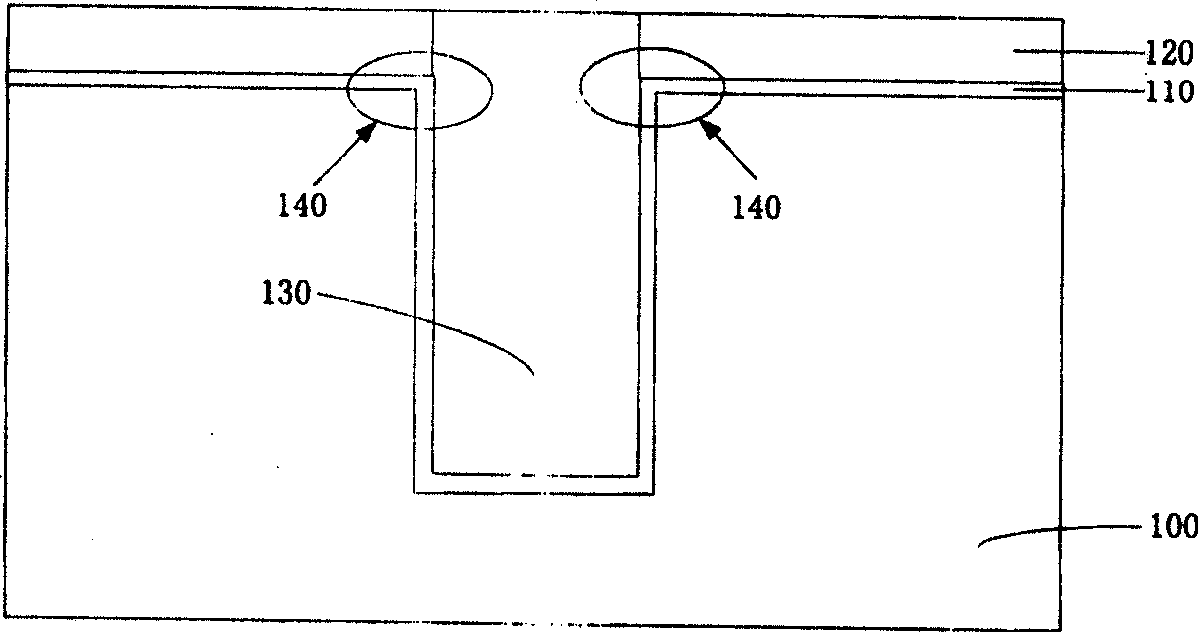

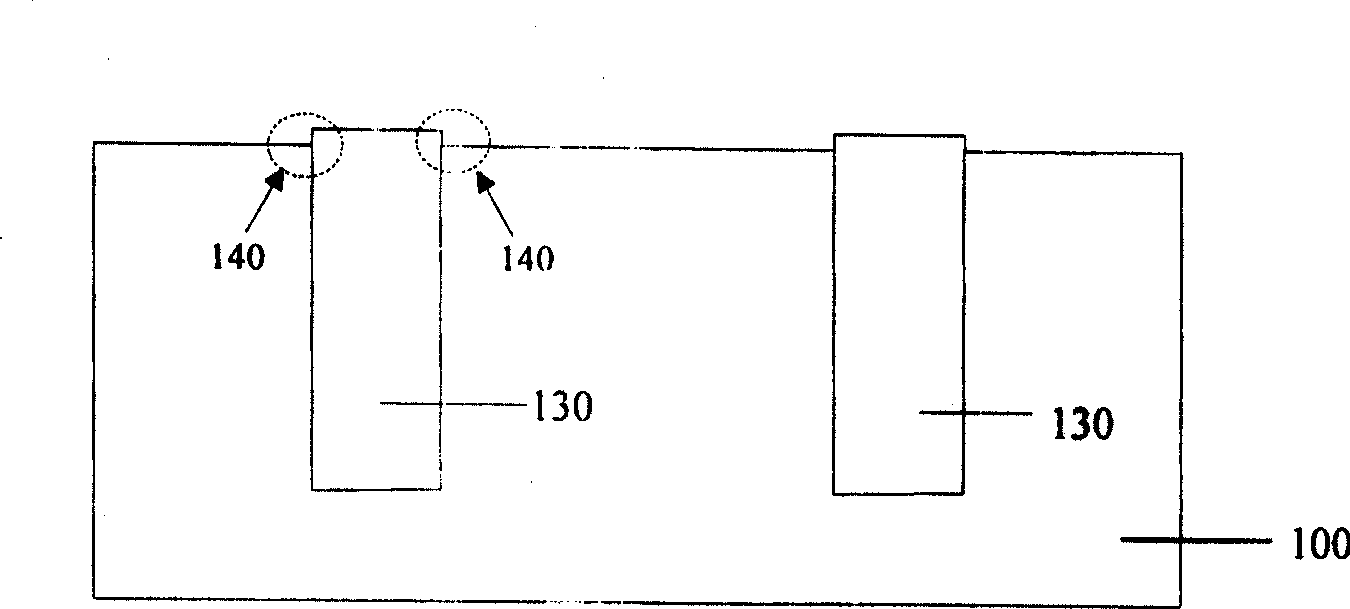

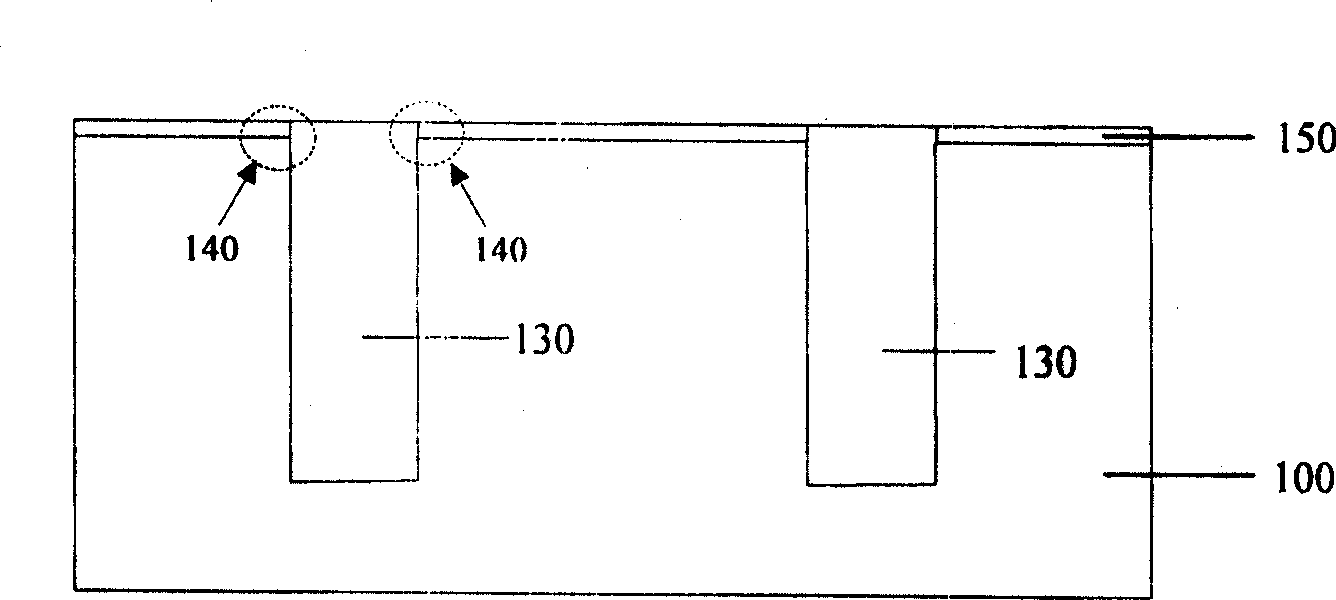

[0038] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0039] The invention relates to the technical field of semiconductor integrated circuit manufacturing, in particular to a method for forming a shallow trench isolation structure in a semiconductor device and the shallow trench isolation structure. It should be noted here that this specification provides different embodiments to illustrate the various features of the present invention, but these embodiments are only for convenience of description by using specific compositions and structures, and do not limit the present invention.

[0040] After the manufacturing process of semiconductor devices enters the process node of 65nm and below, the influence of stress on the carrier mobility of CMOS devices becomes more and more obvious. The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More