High-speed burst mode clock data recovery circuit

A burst mode and recovery circuit technology, applied in the field of digital communication, can solve problems such as slow synchronization speed that cannot meet data recovery, high circuit manufacturing process requirements, low R&D costs, etc., to achieve easy integration or secondary integration, production process Effects with low requirements and clean clock spectrum

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Below in conjunction with accompanying drawing and embodiment the present invention will be further described

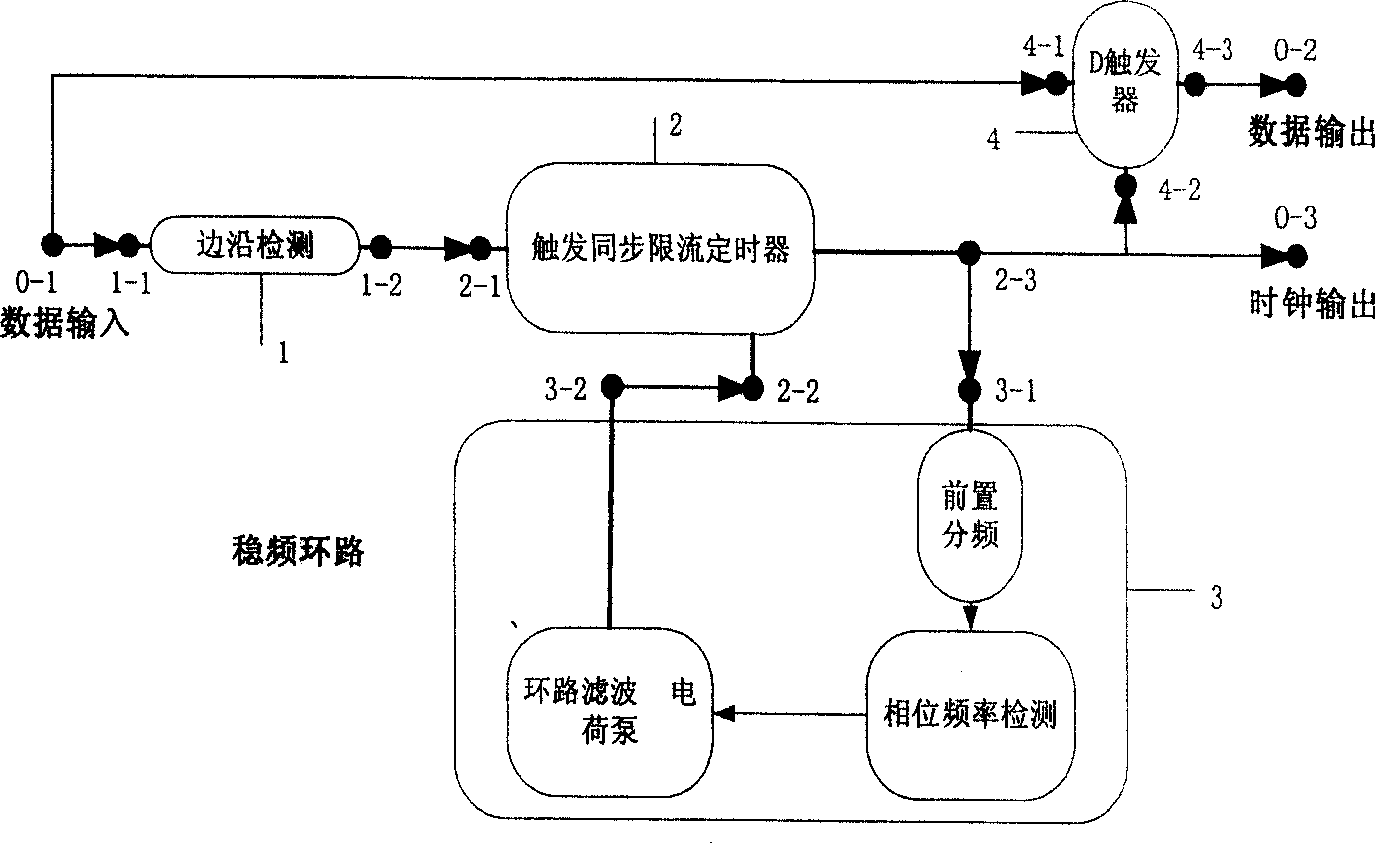

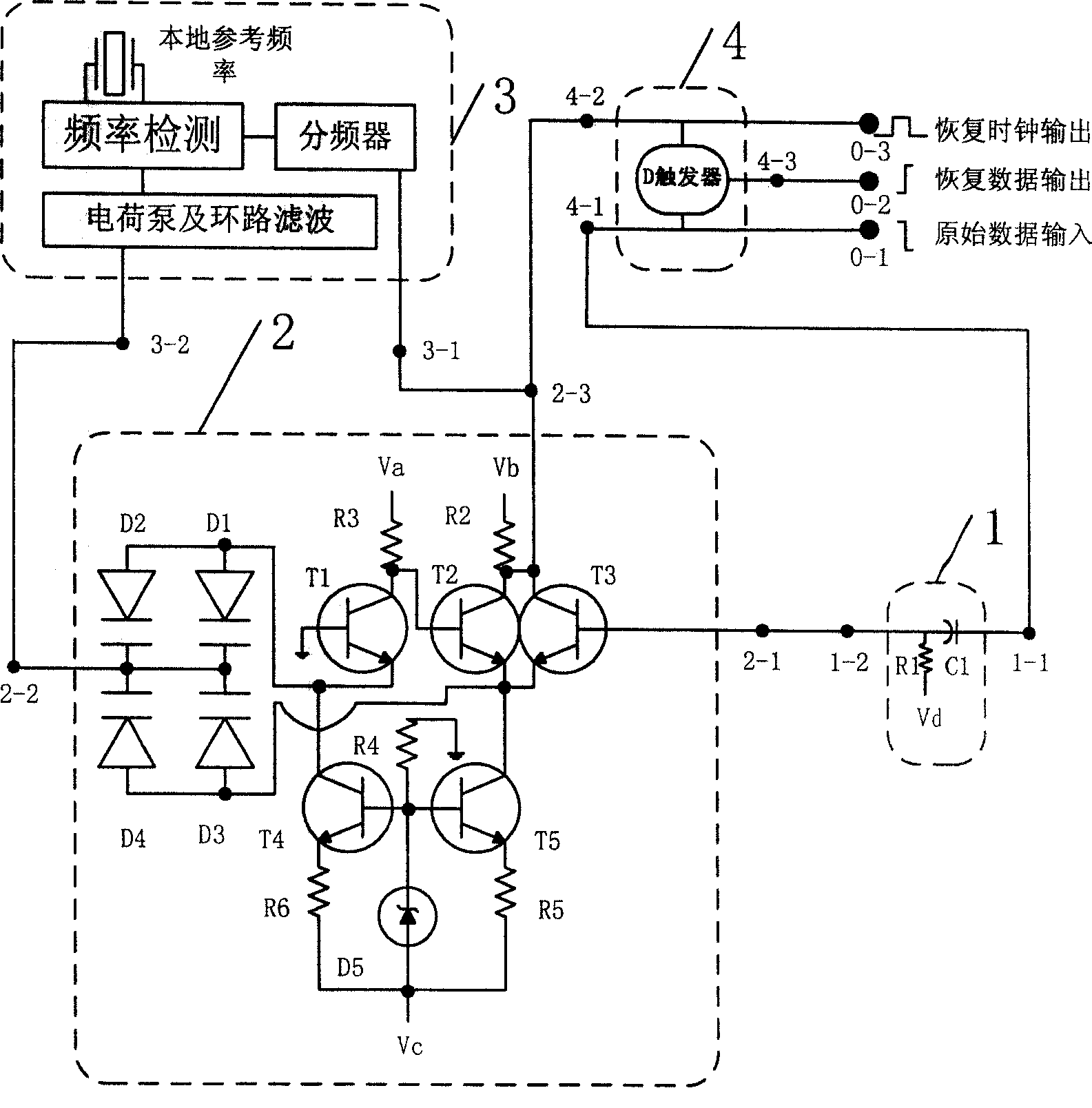

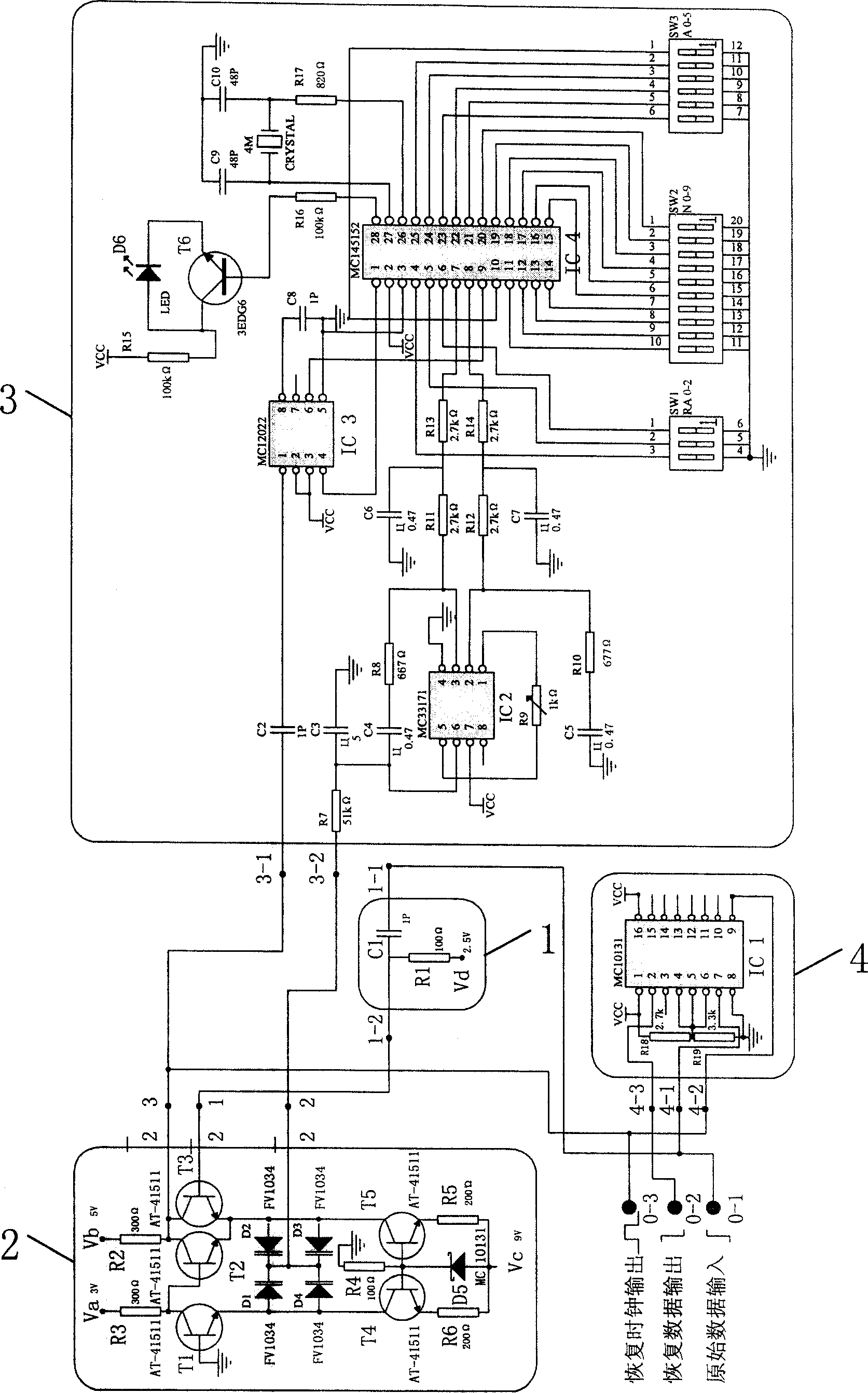

[0029] figure 2 It is a circuit block diagram of the present invention, wherein, 1 is an edge detection circuit, 2 is a current-limiting timer with a trigger input, 3 is a frequency stabilization loop, and 4 is a decision output circuit. R1 to R6 are resistors; T1 to T5 are bipolar transistors; C1 is a capacitor, D1 to D4 are varactor diodes; D5 is a Zener diode; Va, Vb, Vc, and Vd are power supply voltages.

[0030] The circuit shown in the figure is composed as follows:

[0031] The edge detection circuit 1 is characterized by an RC differential circuit. The input data signal passes through the differential circuit composed of C1 and R1 to detect the positive and negative jumps of the data signal, and then clamped to the threshold level of T5 by Vd. Only the positive transition is triggered, and the negative transition does not have much influence on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More