High speed parallel-serial data switching system

A technology for converting systems and serial data, which is applied to parts of TV systems, TVs, color TVs, etc., can solve the problems of large area required for integration, poor implementability, large power consumption and noise, etc., to achieve Effects of area reduction required for integration, cost control, and power consumption reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The following describes the present invention in further detail based on the drawings and embodiments:

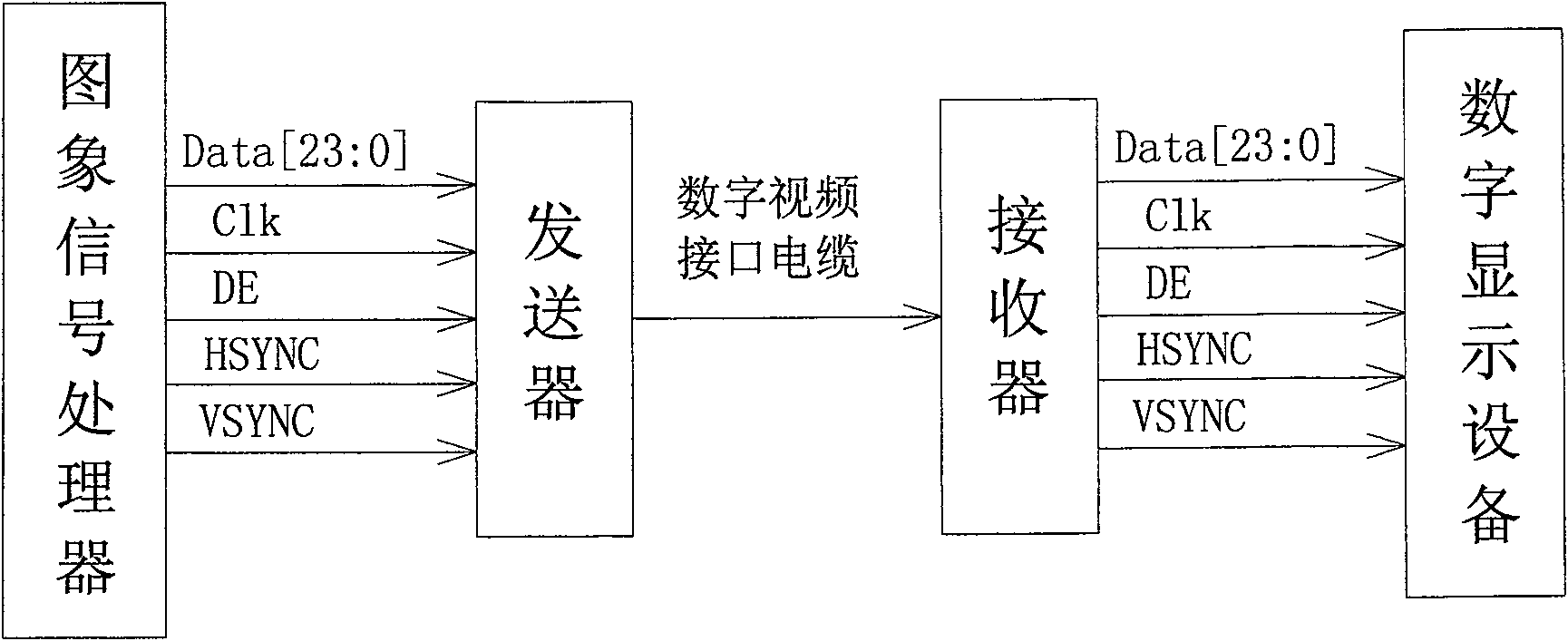

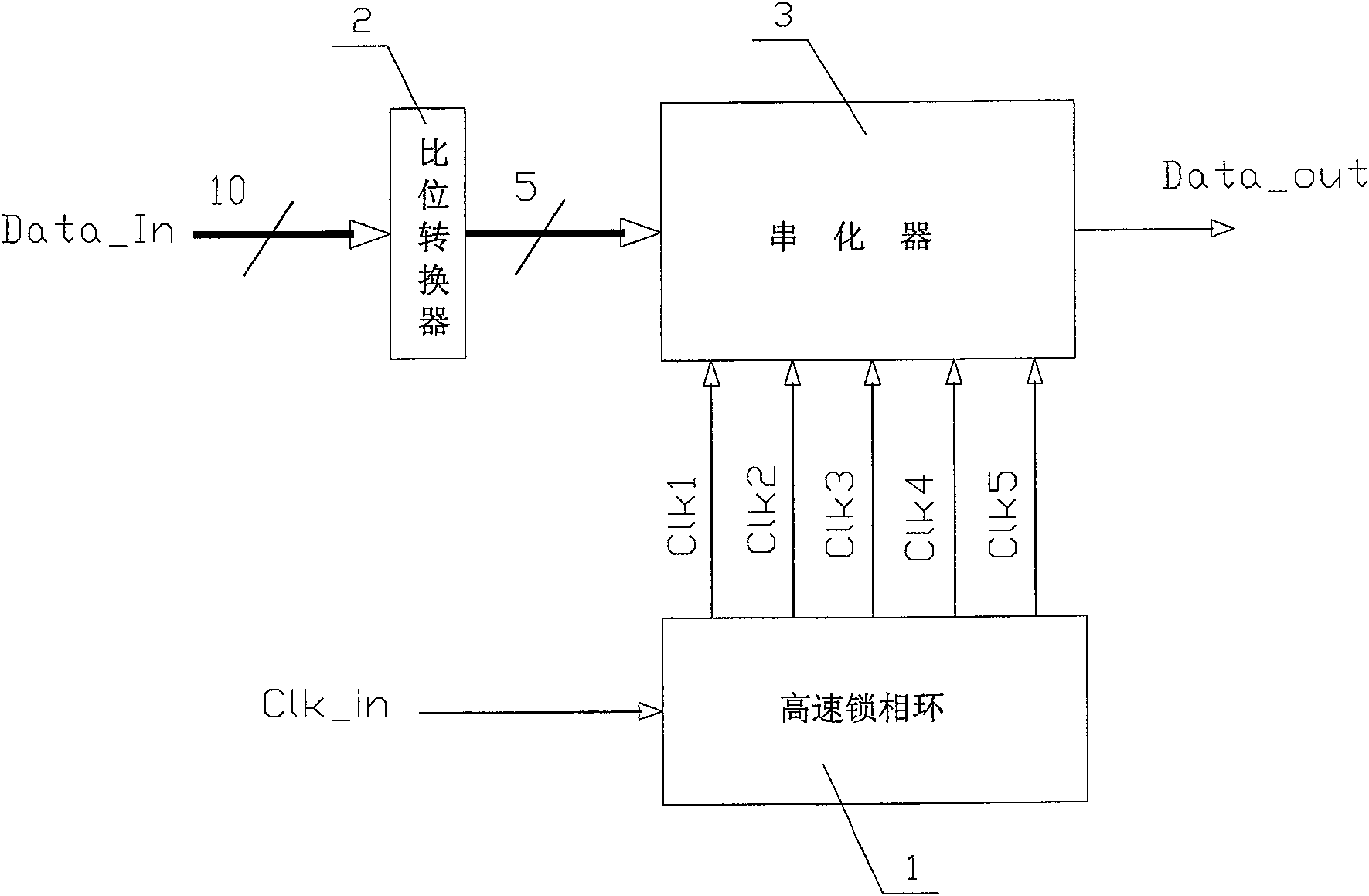

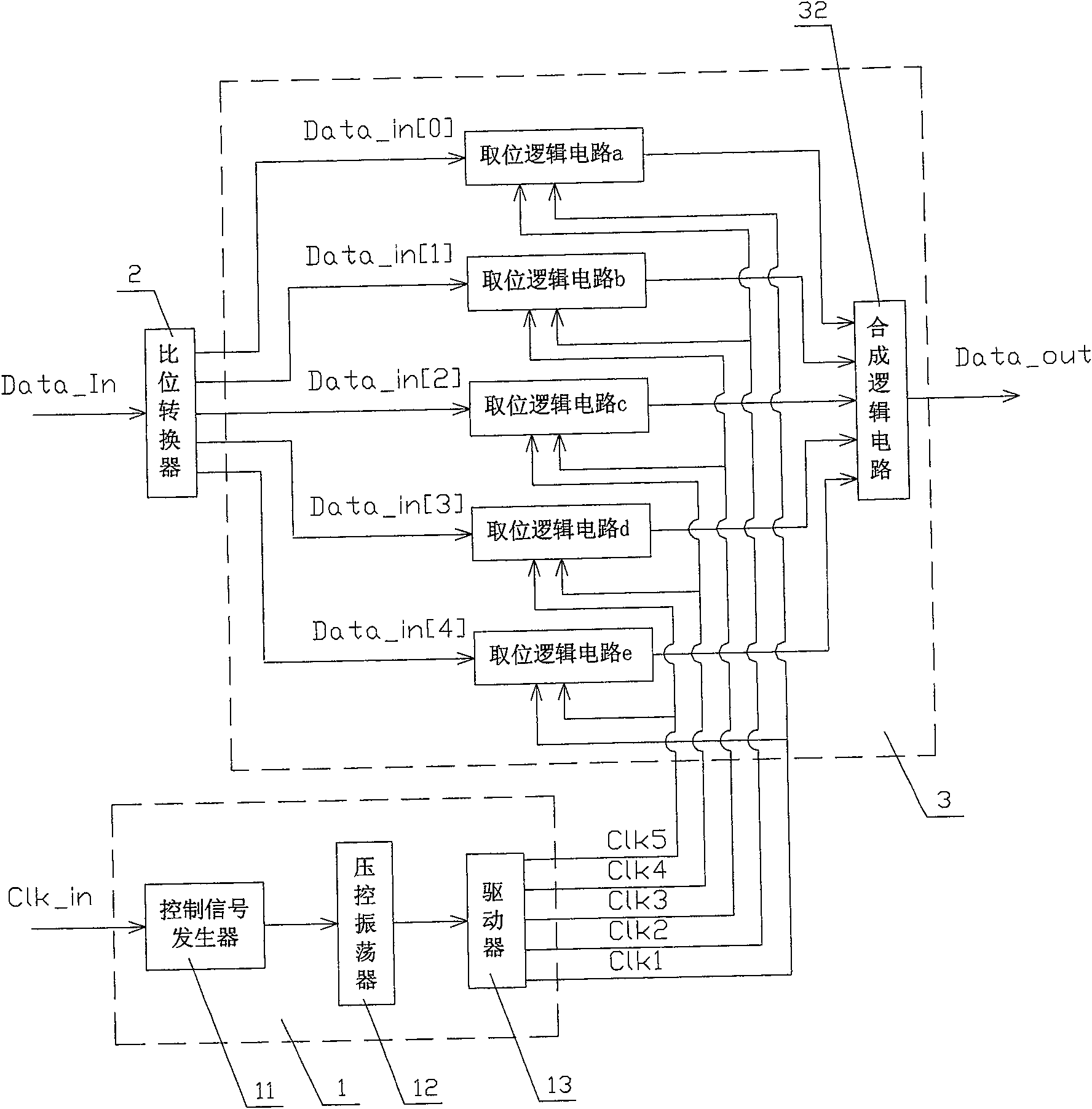

[0029] according to figure 2 with image 3 , The present invention includes a high-speed phase-locked loop 1, a bit-bit converter 2 and a serializer 3. The bit-bit converter 2 processes the input high-bit parallel data signal with a frequency multiplier clock to generate a low-bit parallel data output signal, Such as figure 1 As shown, the bit converter 2 multiplies the input 10-bit parallel data signal Data_In to generate a 5-bit parallel data signal Data_in[4:0], and the serializer 3 receives the parallel output signal from the bit converter 2. For the data signal Data_in[4:0], the serializer 3 generates a serial output data signal according to the clock signal generated by the high-speed phase-locked loop 1.

[0030] Such as image 3 with Figure 4 As shown, the high-speed phase-locked loop 1 includes a control signal generator 11, a voltage-controlled oscillator 12...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More