LDO circuit using bidirectional asymmetry buffer structure to improve performance

A buffer and asymmetric technology, applied in the direction of instruments, adjusting electrical variables, control/regulation systems, etc., can solve problems such as increasing LDO quiescent current, reducing LDO power supply voltage rejection ratio, increasing circuit complexity, etc., to achieve expansion of unity gain Wider bandwidth, improved transient response performance, and flexible circuit configuration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

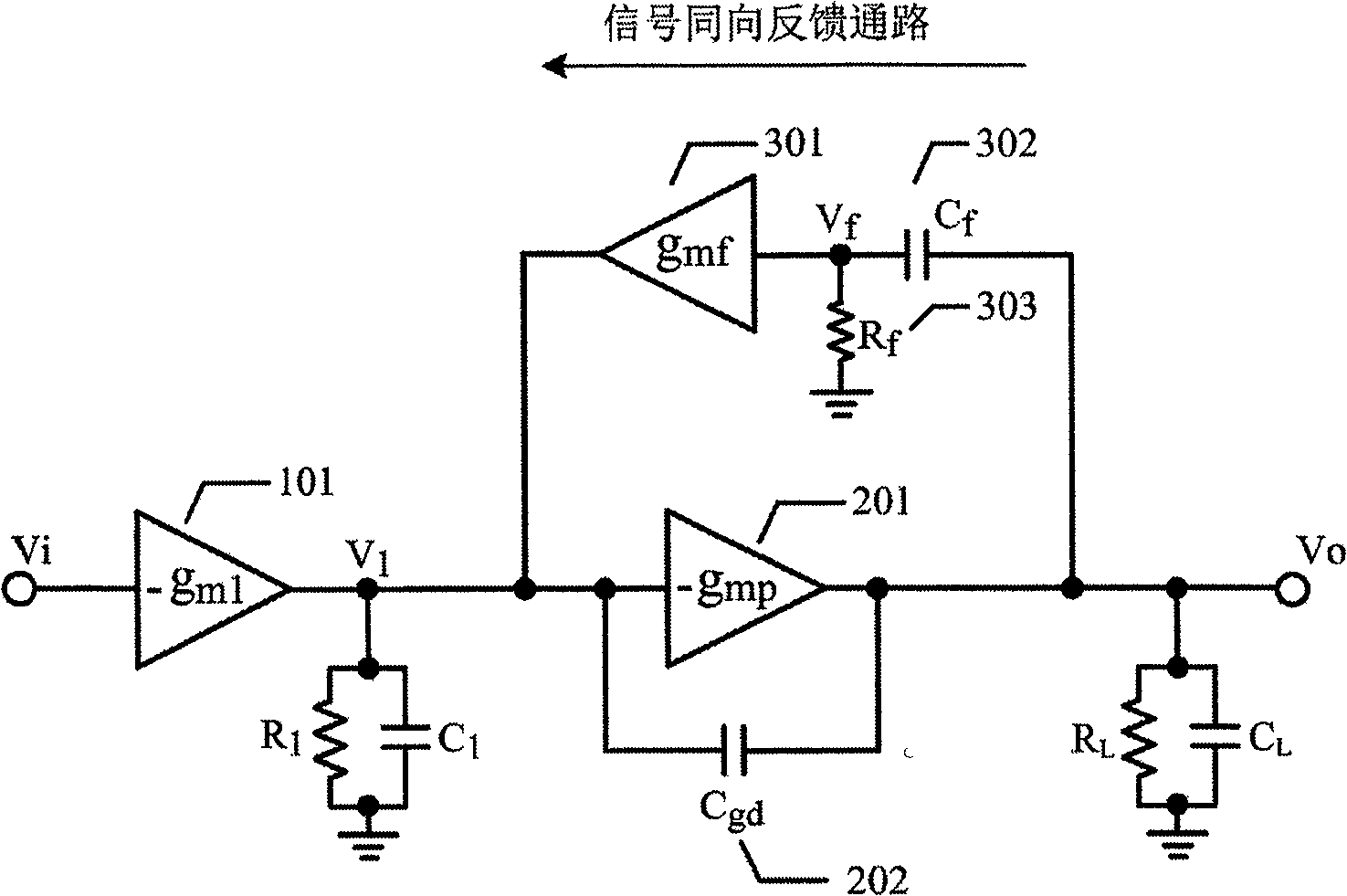

[0047] Figure 5 The block diagram of the circuit principle for canceling the right half-plane zero point of the present invention is given, including the buffer stage 401, the first reverse gain stage 101, the LDO transmission element 201, and the gate-drain parasitic capacitance C of the LDO transmission element 201 gd 202, and the second reverse gain stage 301, capacitor C f 302. Resistance R f A two-way asymmetric buffer structure composed of 303. Node V i , V b , V 2 And V o Are the input end and output end of the buffer stage 401, the output end of the first reverse gain stage 101 and the output end of the LDO, R b , C b Is node V b Output impedance and lumped parasitic capacitance, R 2 , C 2 Is node V 2 Output impedance and lumped parasitic capacitance, R L , G L Is node V o The output impedance (including load impedance) and load capacitance.

[0048] It should be noted, Figure 5 The buffer stage 401 in the schematic block diagram shown may be a buffer stage with a signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More