High-capacity FLASH solid memory controller

A controller and large-capacity technology, applied in static memory, digital memory information, instruments, etc., can solve problems such as data errors, poor error correction capability of stored controller data, and inability to meet the high reliability requirements of aerospace and military industries. Simplified operation, increased speed, and the effect of strong scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

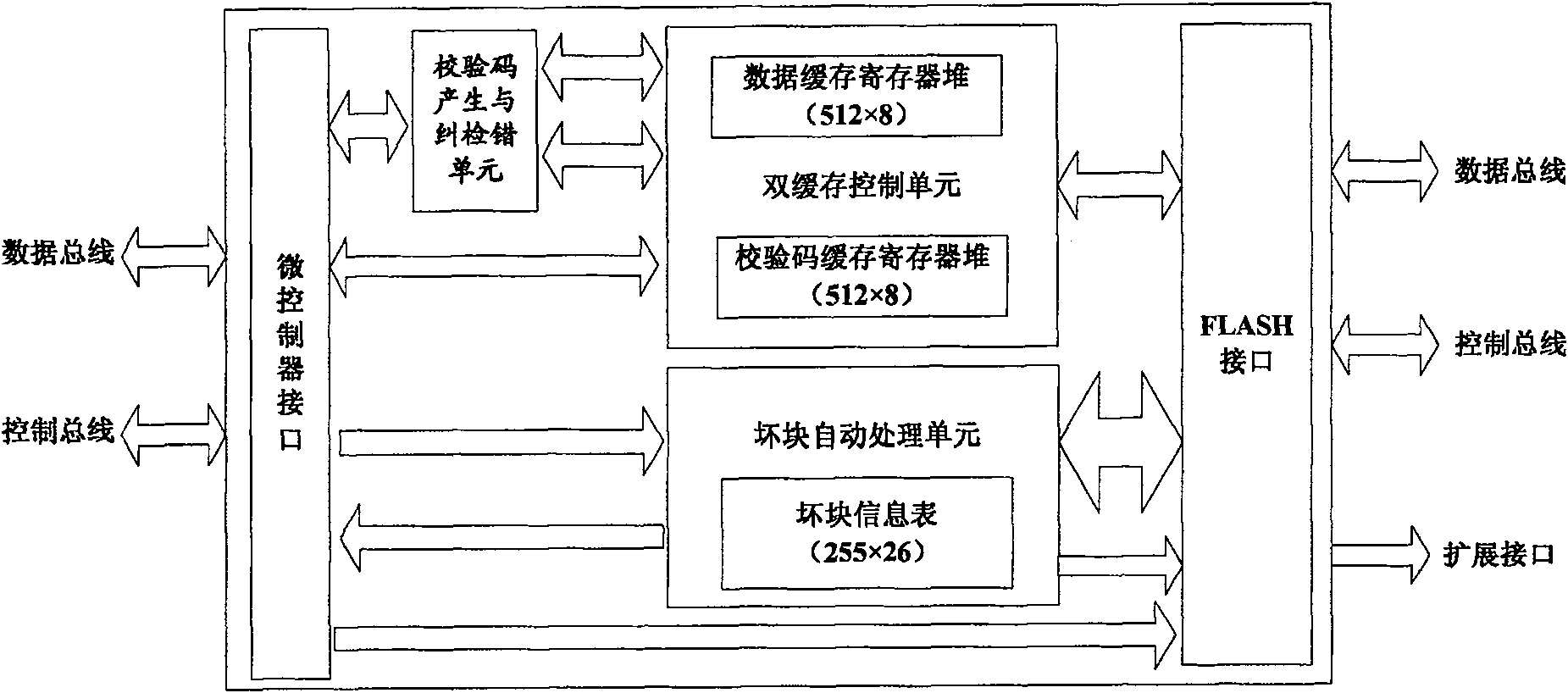

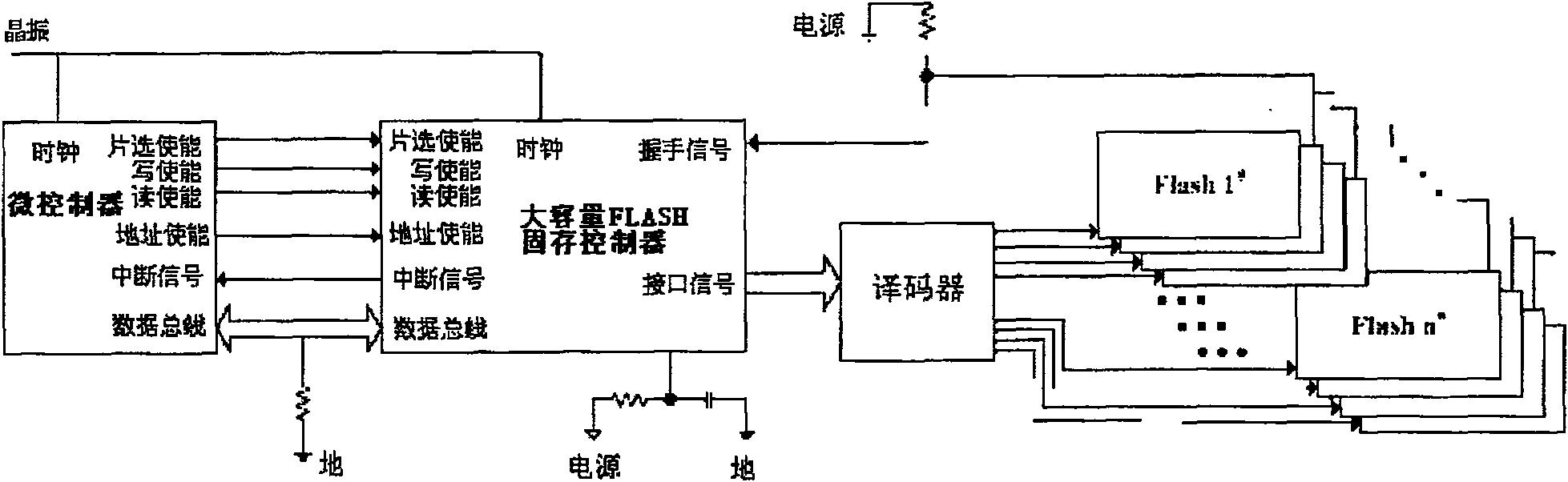

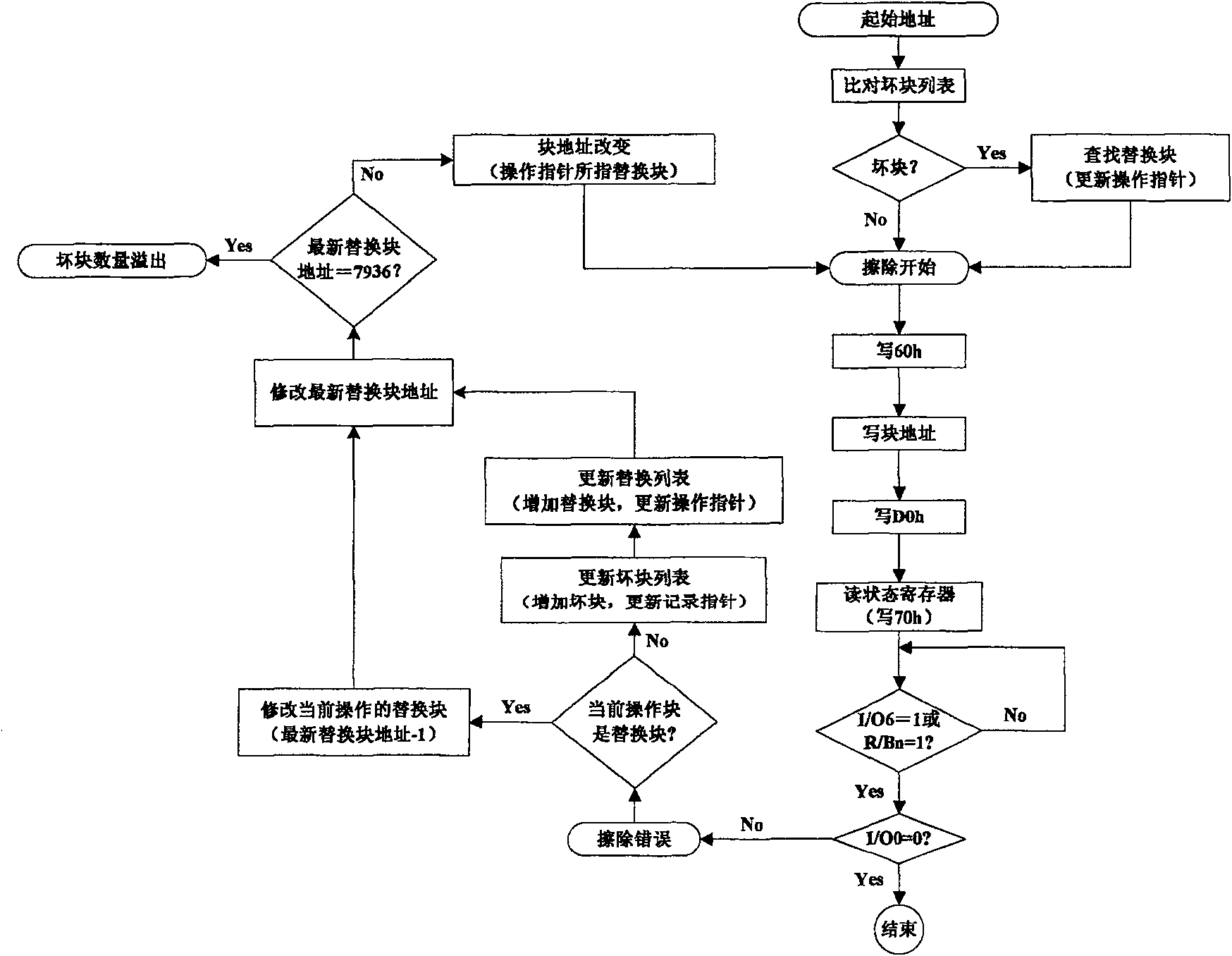

[0033] Such as figure 1 Shown is the principle block diagram of the large-capacity FLASH solid memory controller of the present invention, including a microcontroller interface, a FLASH interface, a data buffer unit, a check code buffer unit, a check code generation and error detection and correction unit, and automatic processing of bad blocks. Unit and double buffer control unit, in which the microcontroller interface and the microcontroller are used for data communication; the FLASH interface is for data communication with the FLASH; the data buffer unit stores the data to be transmitted; the check code buffer unit stores the data stored with the data buffer unit Corresponding check code; the check code generation and error detection unit receives data from the external microcontroller via the microcontroller interface, generates a check code based on the transmitted data, and combines the data with the check code It is sent to the double buffer control unit; the data from the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More