Method for realizing RTD and HEMT single chip integration using dry etching technology

A technology of dry etching and monolithic integration, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve the problems of not being suitable for industrialized mass production, not being suitable for small-sized device circuits, and being unable to accurately control device sizes, etc. problem, to achieve the effect that is beneficial to the consistency of threshold voltage and transconductance, good etching uniformity, and good directionality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

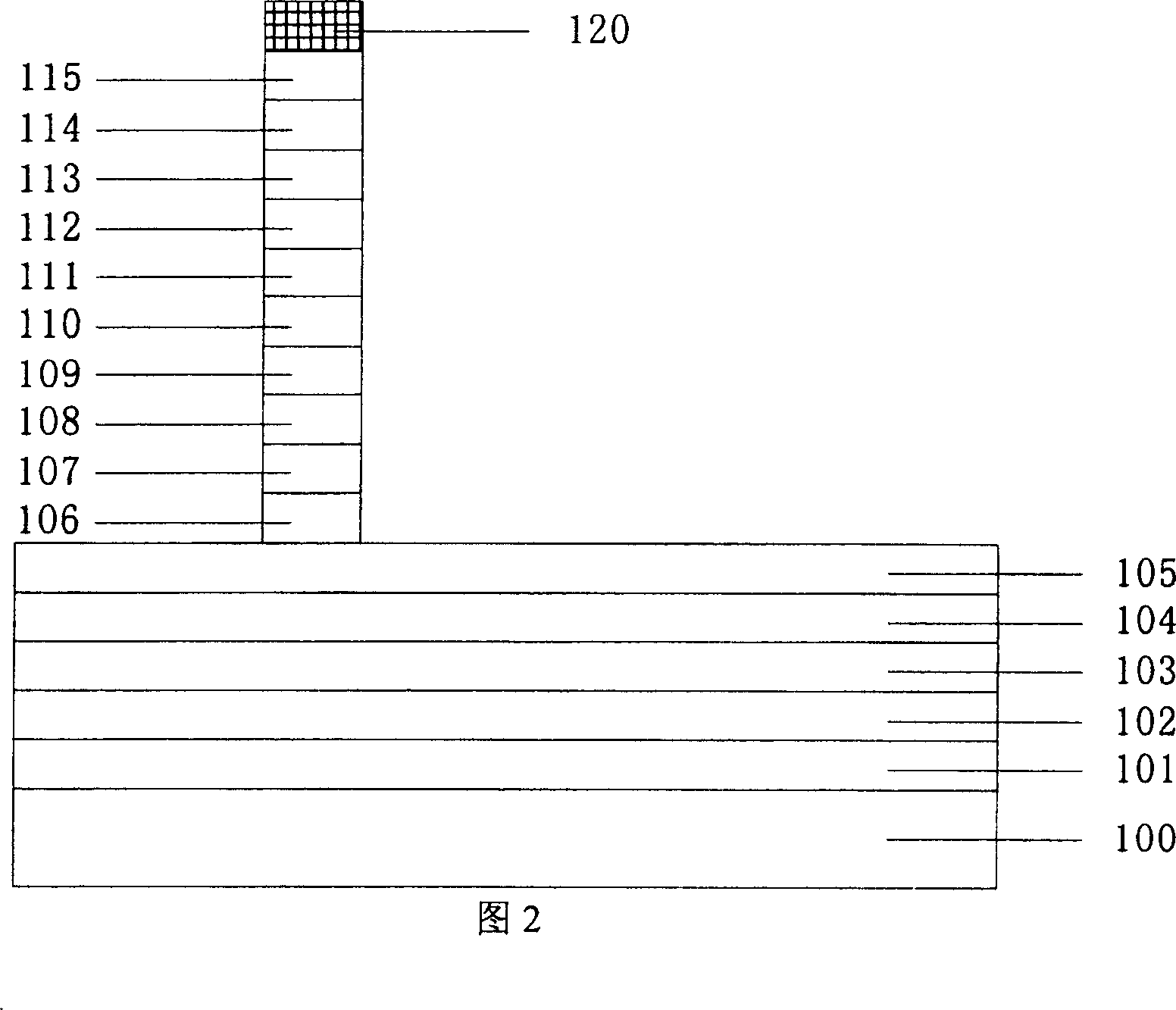

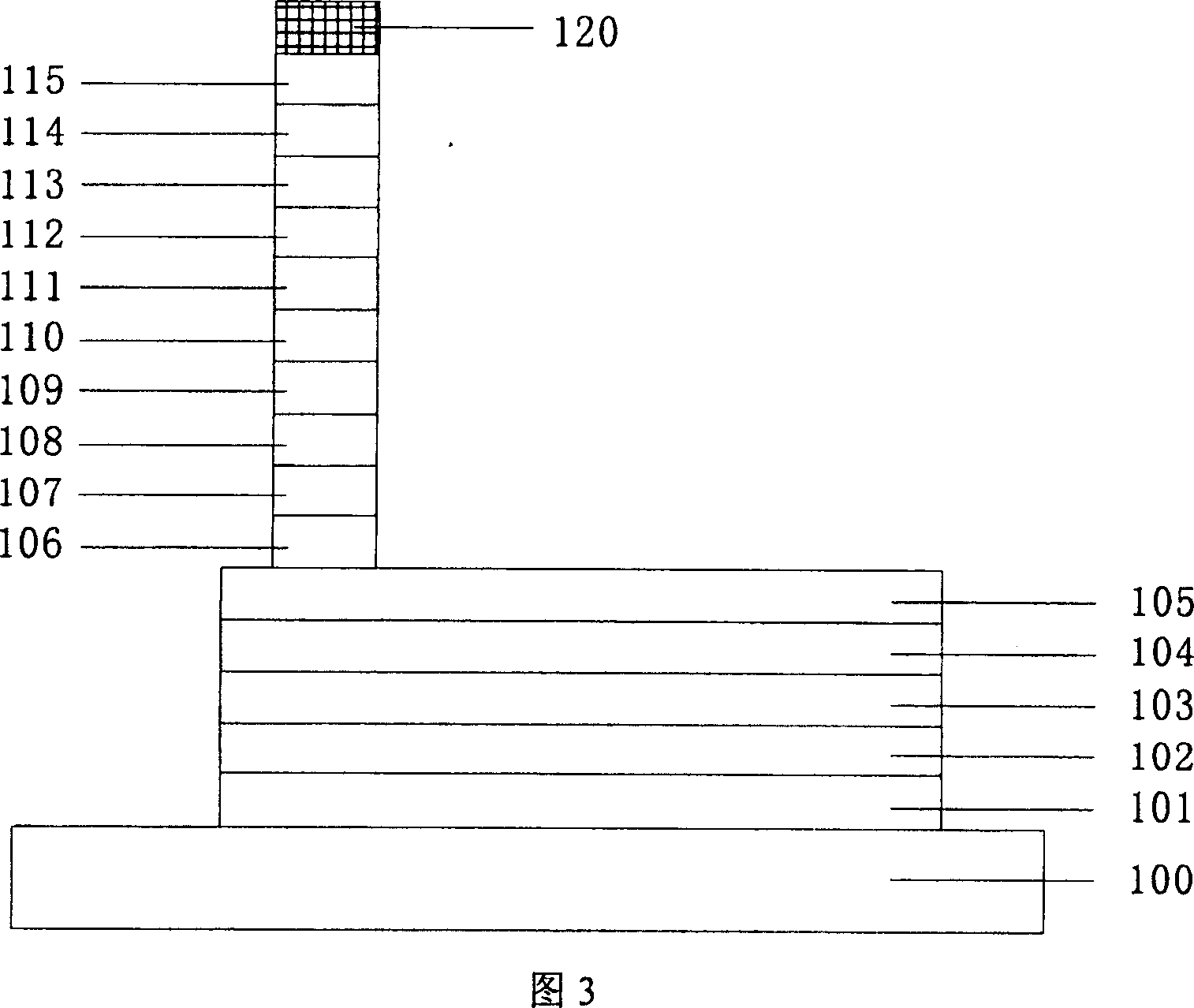

[0060] Please refer to Fig. 1-Fig. 9 again, a kind of method that adopts dry etching technology to realize RTD and HEMT monolithic integration of the present invention, comprises the following steps:

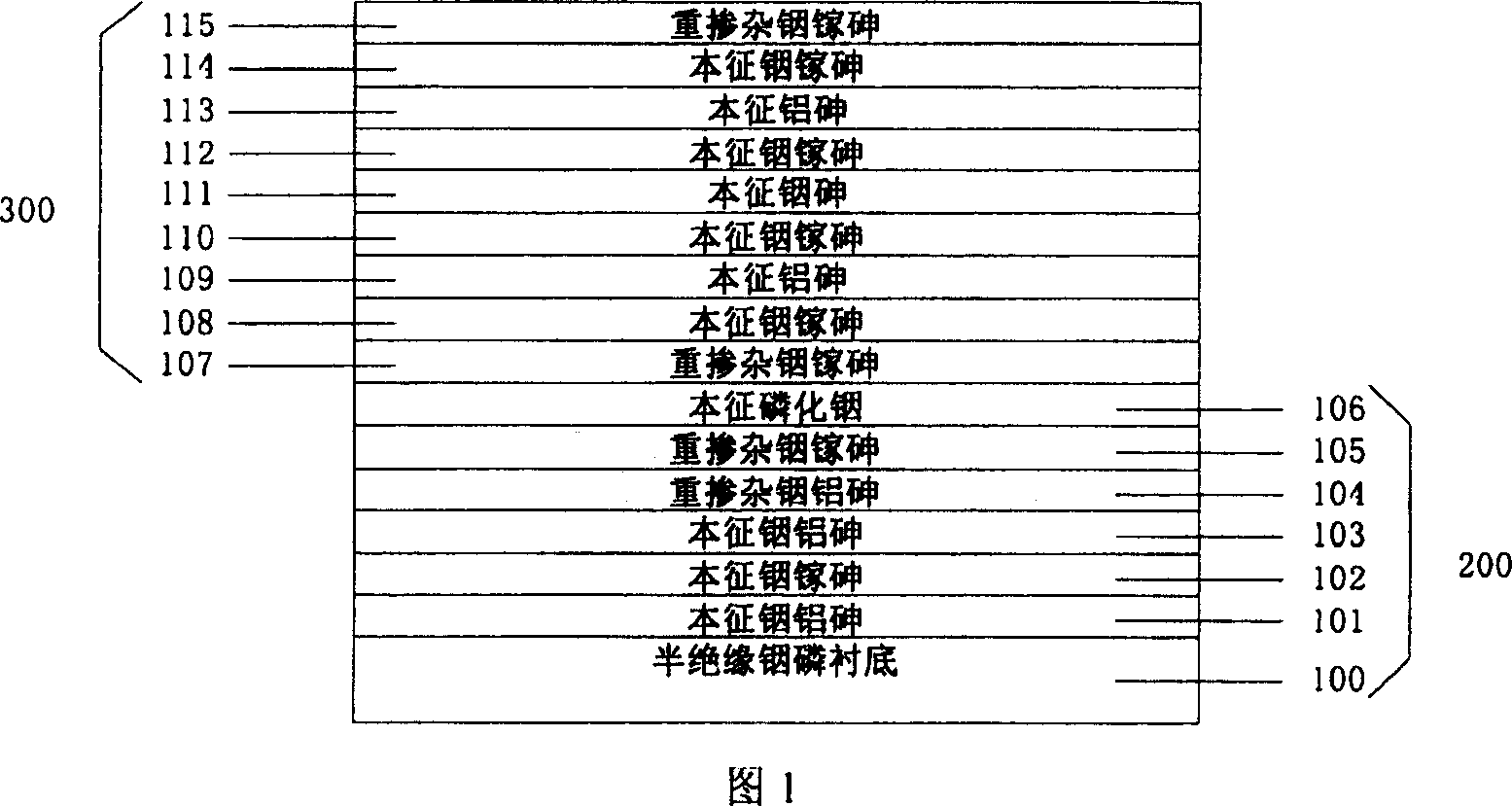

[0061] Step 1: On the semi-insulating InP substrate 100, the material structure of HEMT and RTD is sequentially grown by molecular beam epitaxy: the HEMT structure includes a 2000A non-doped InAlAs buffer layer 101, a 150A non-doped InGaAs channel 102, and a 30A non-doped Doped InAlAs isolation layer 103, 4×1012 cm-2 delta plane doped layer, 200A non-doped InAlAs barrier 104 and 200A heavily doped InGaAs cap layer 105. This is followed by a 50AInP selective etch stop layer 106, and an RTD structure including a heavily doped 500AInGaAs collector contact layer 107, a 50A undoped collector spacer 108, a 16A undoped AlAs barrier 109, and a 13A undoped Doped InGaAs well 110, 18A non-doped InAs sub-well 111, 13A non-doped InGaAs well 112, 16A non-doped AlAs barrier 113, 50A non-doped ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More