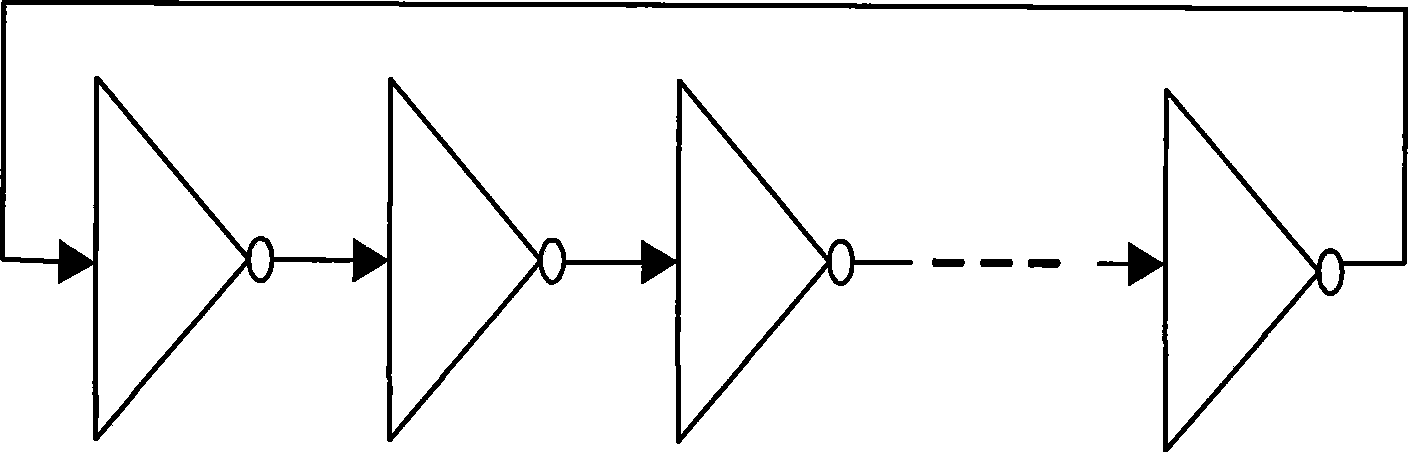

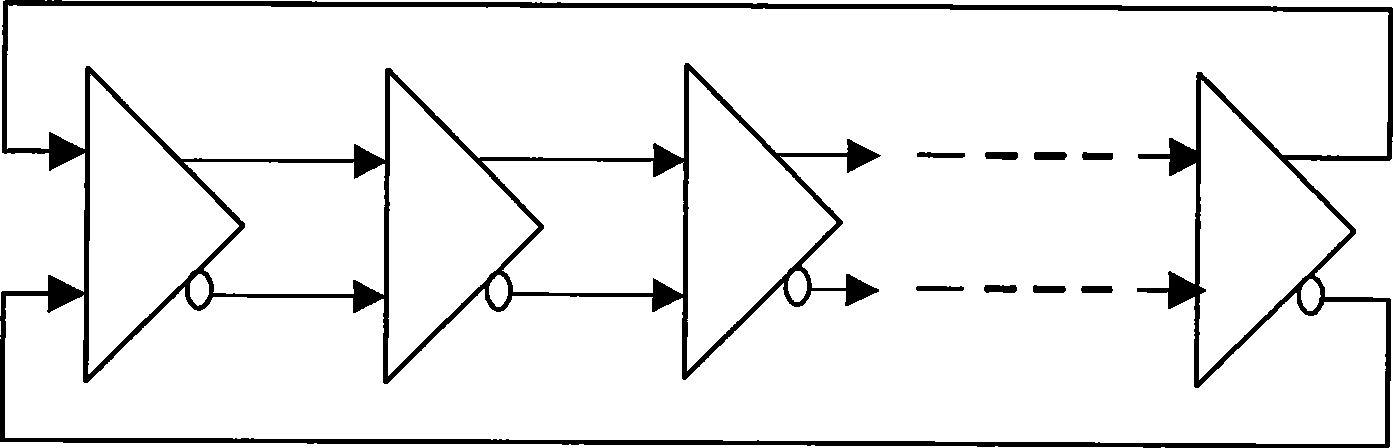

Differential circuit delay unit for high-speed voltage control oscillator

A voltage-controlled oscillator, differential circuit technology, used in electrical components, single output arrangements, automatic control of power, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

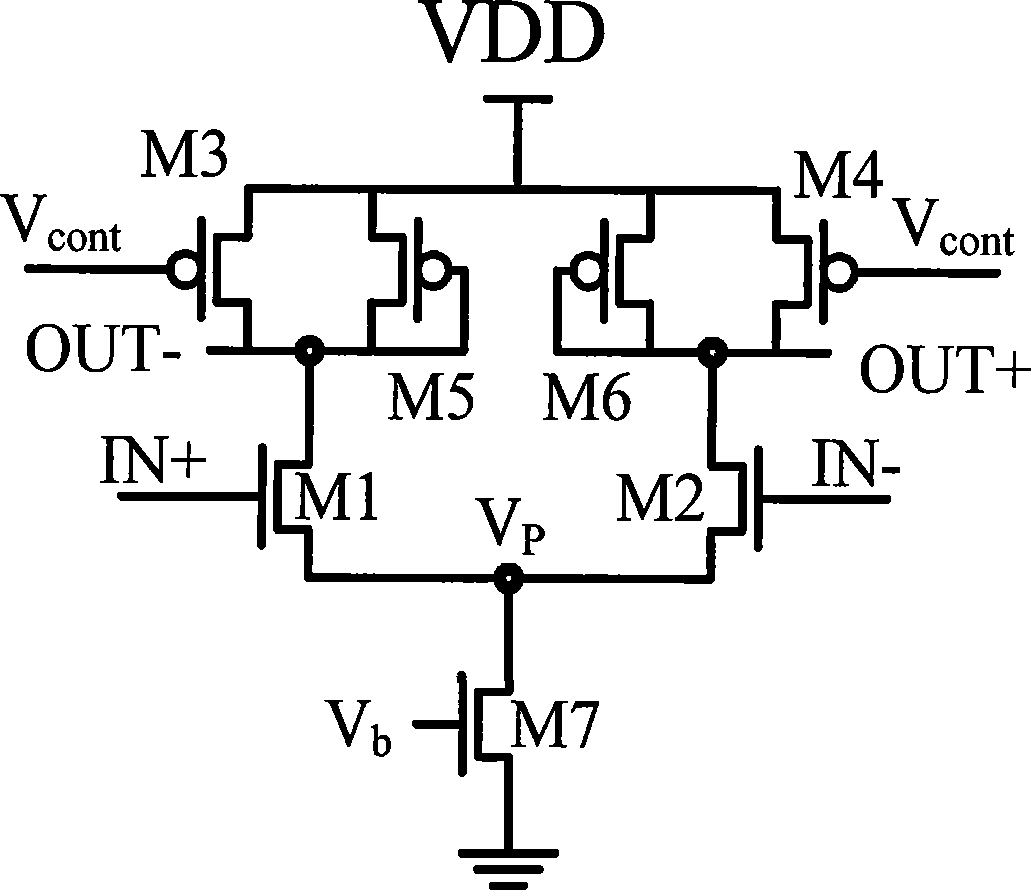

[0021] Such as Figure 5 As shown, the present invention is used for a differential circuit delay unit of a high-speed voltage-controlled oscillator, which includes a first NMOS transistor M1, a second NMOS transistor M2, a first PMOS transistor M3, a second PMOS transistor M4, a third PMOS transistor M5, The structure of the fourth PMOS transistor M6, the fifth PMOS transistor M7 and the sixth PMOS transistor M8 has no tail current source. Among them, the first NMOS transistor M1 and the second NMOS transistor M2 form a differential pair, the gates of which are respectively connected to the differential inputs IN+ and IN-, the drains of the cross-coupled MOS transistors M3 and M4 are respectively connected to the differential outputs OUT- and OUT+, and the gates The poles are respectively connected to the differential outputs OUT+ a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More