Digital low-converter

A digital down-converter and filter technology, applied in phase-modulated carrier systems, electrical components, transmission systems, etc., can solve problems such as speed bottlenecks and achieve the effect of reducing processing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

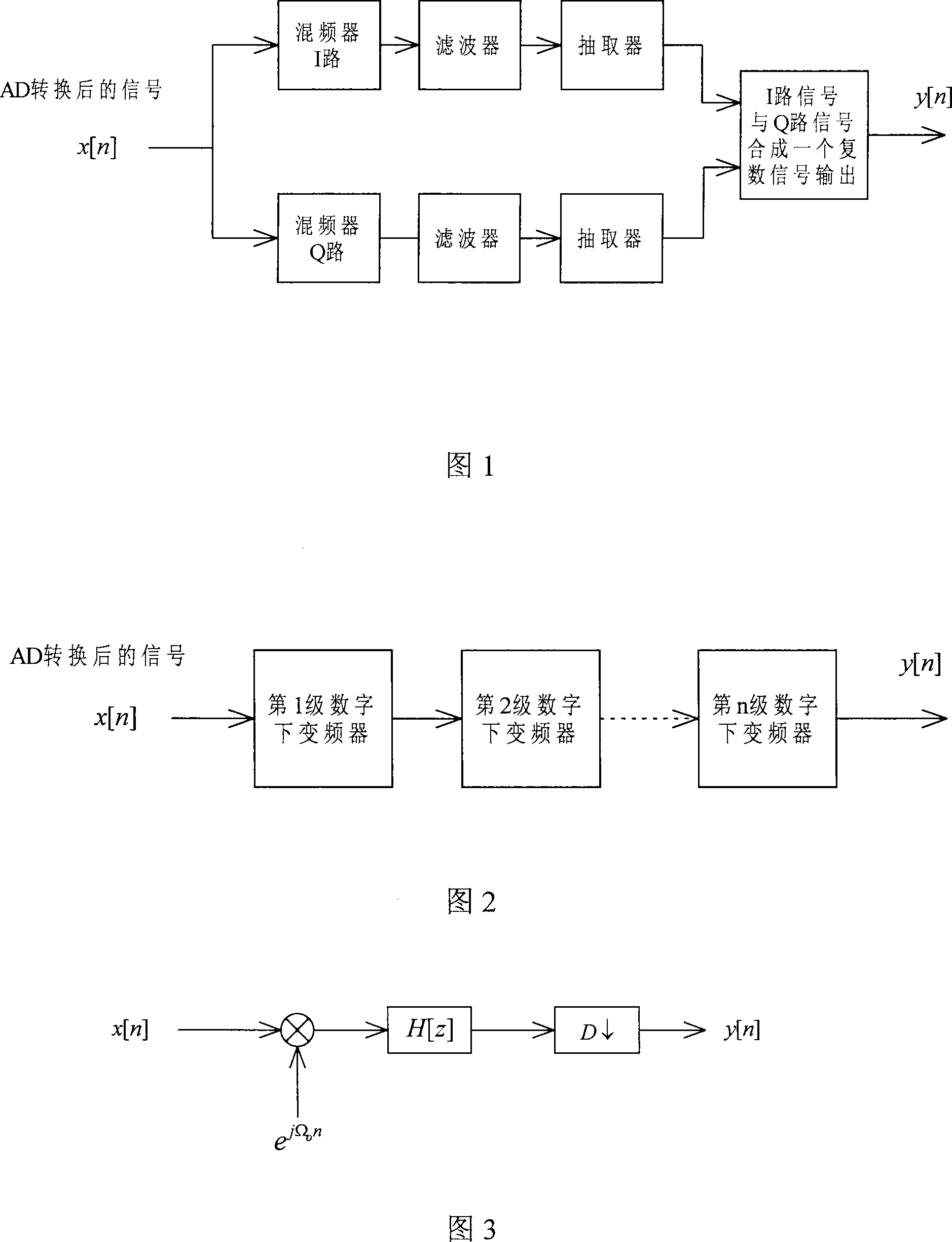

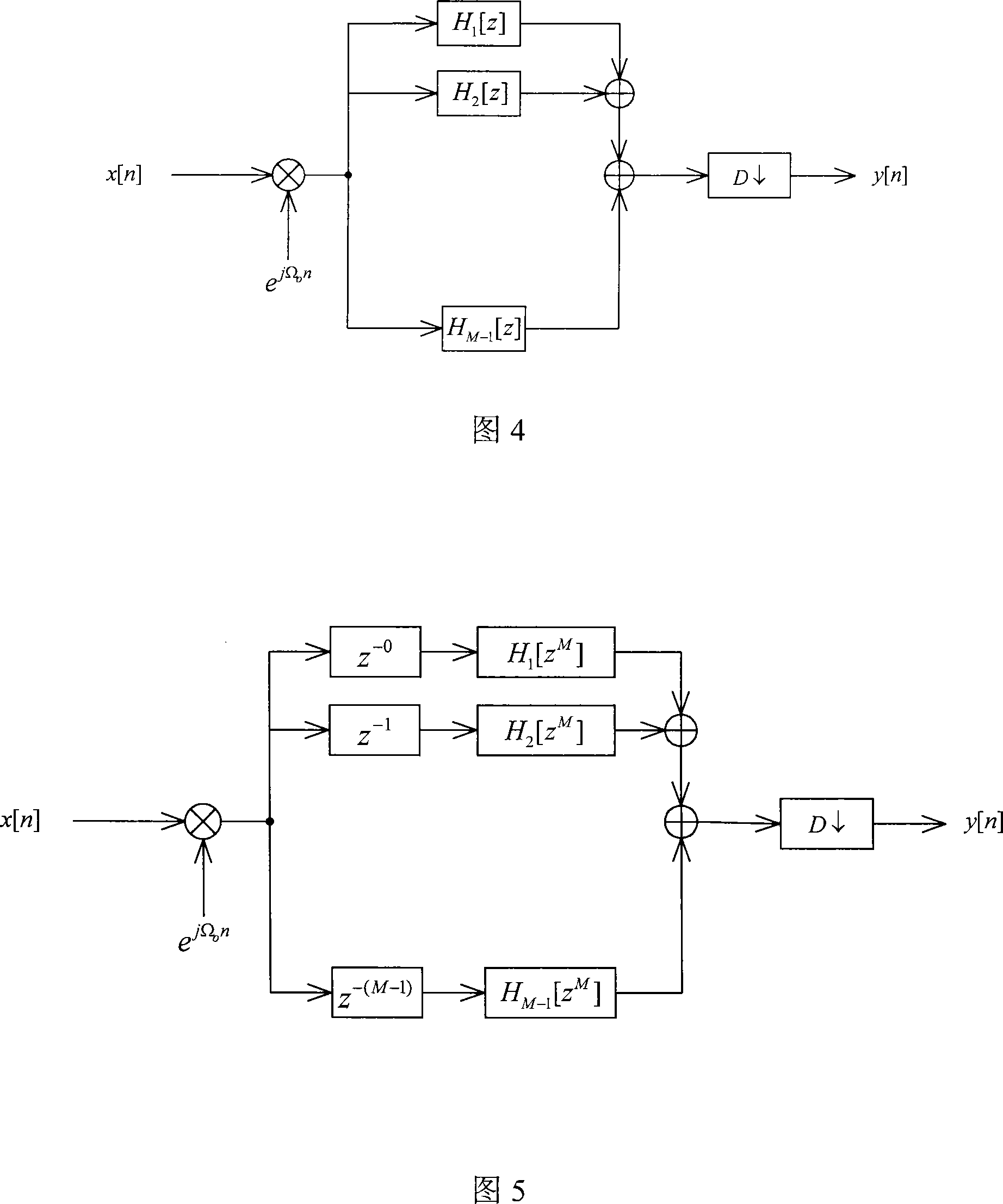

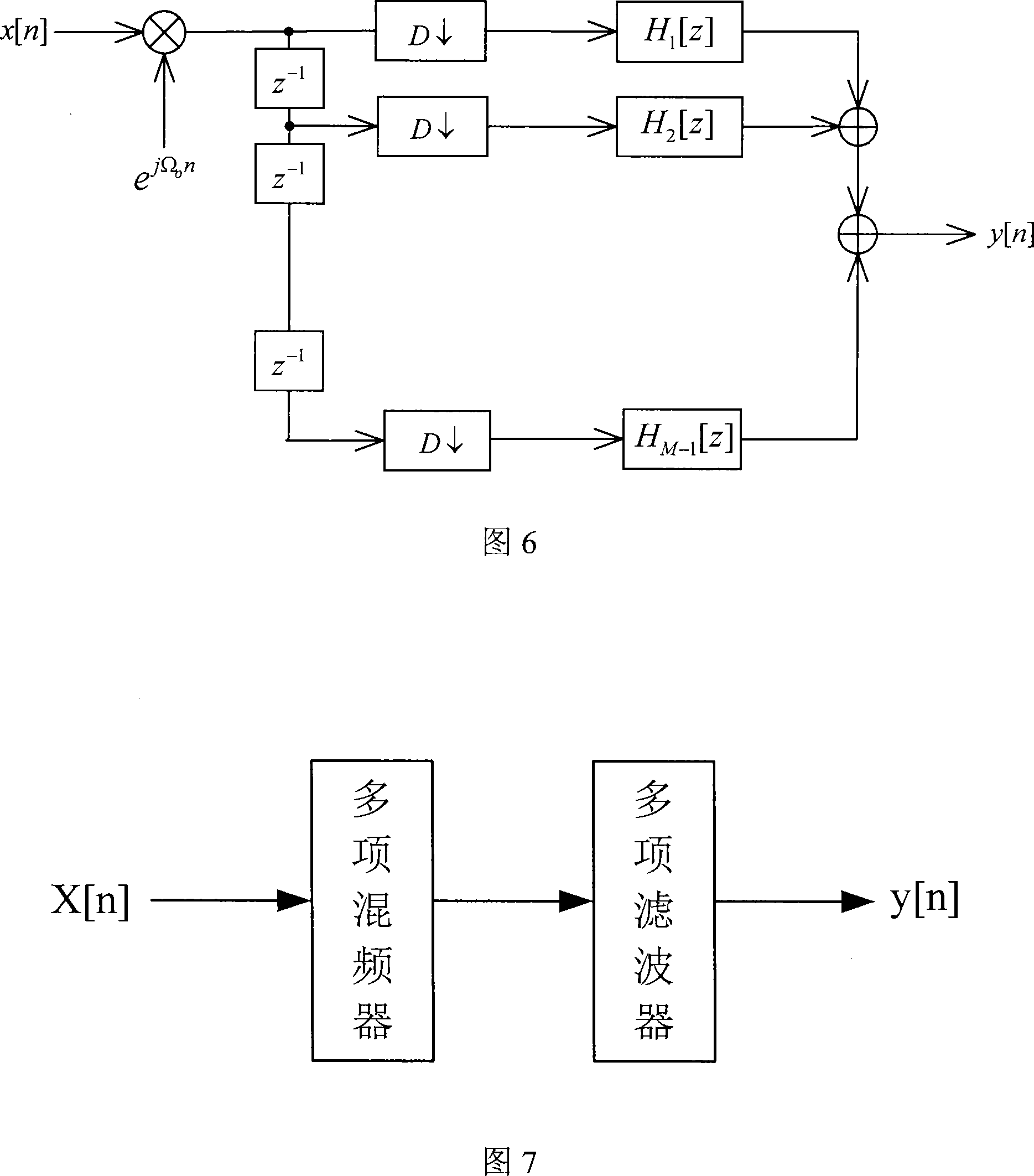

Method used

Image

Examples

Embodiment Construction

[0071] When the number of filter groups is equal to the number N of polyphase mixer groups, N is a natural number. It can be seen from Figure 10 that in each branch of the polyphase mixer:

[0072] c j [ l ] = b j [ n ] l = Nn 0 l ≠ Nn - - - ( 5 )

[0073] d [ l ] = Σ j = 0 N - ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More