Patents

Literature

31 results about "Clock cycle time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

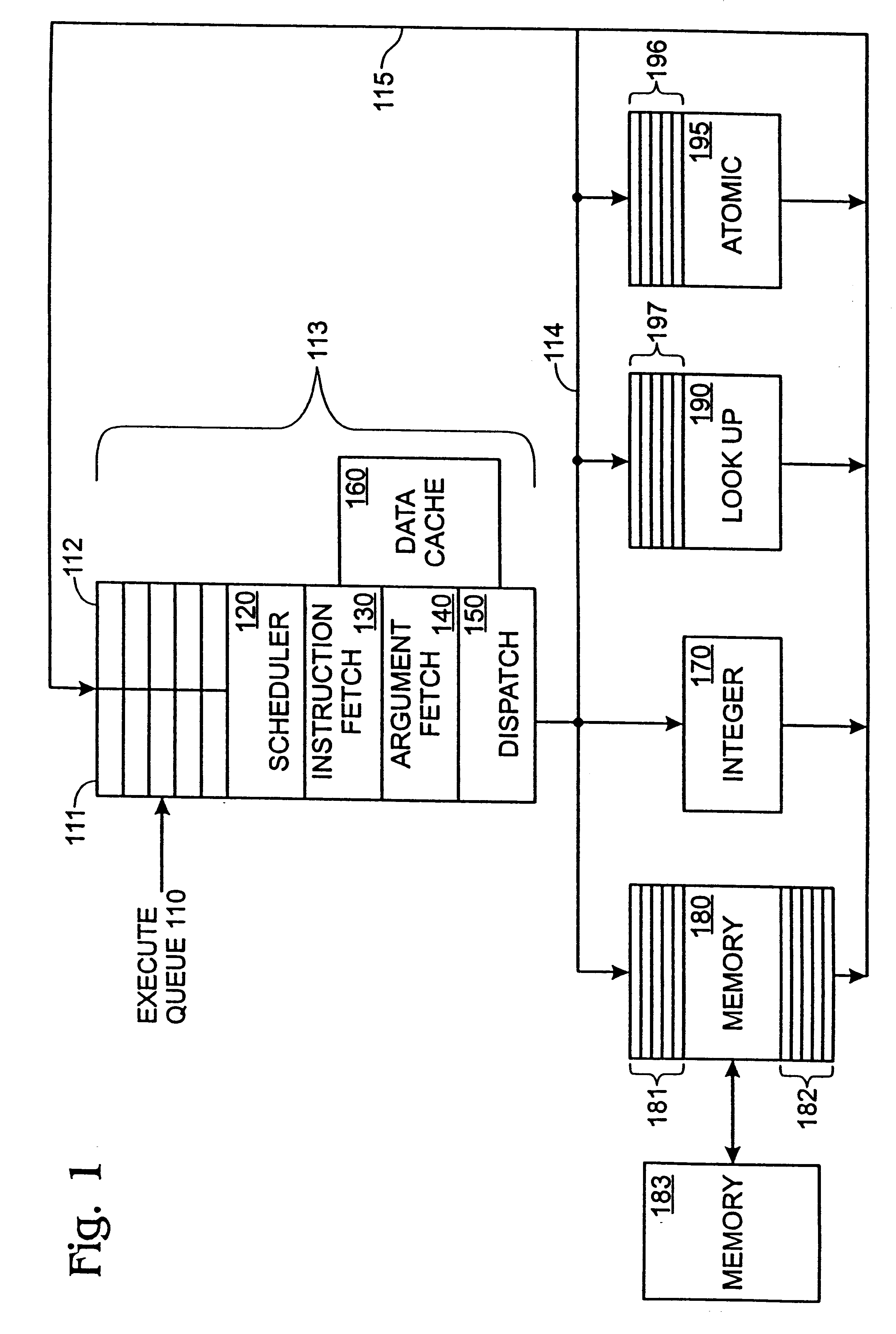

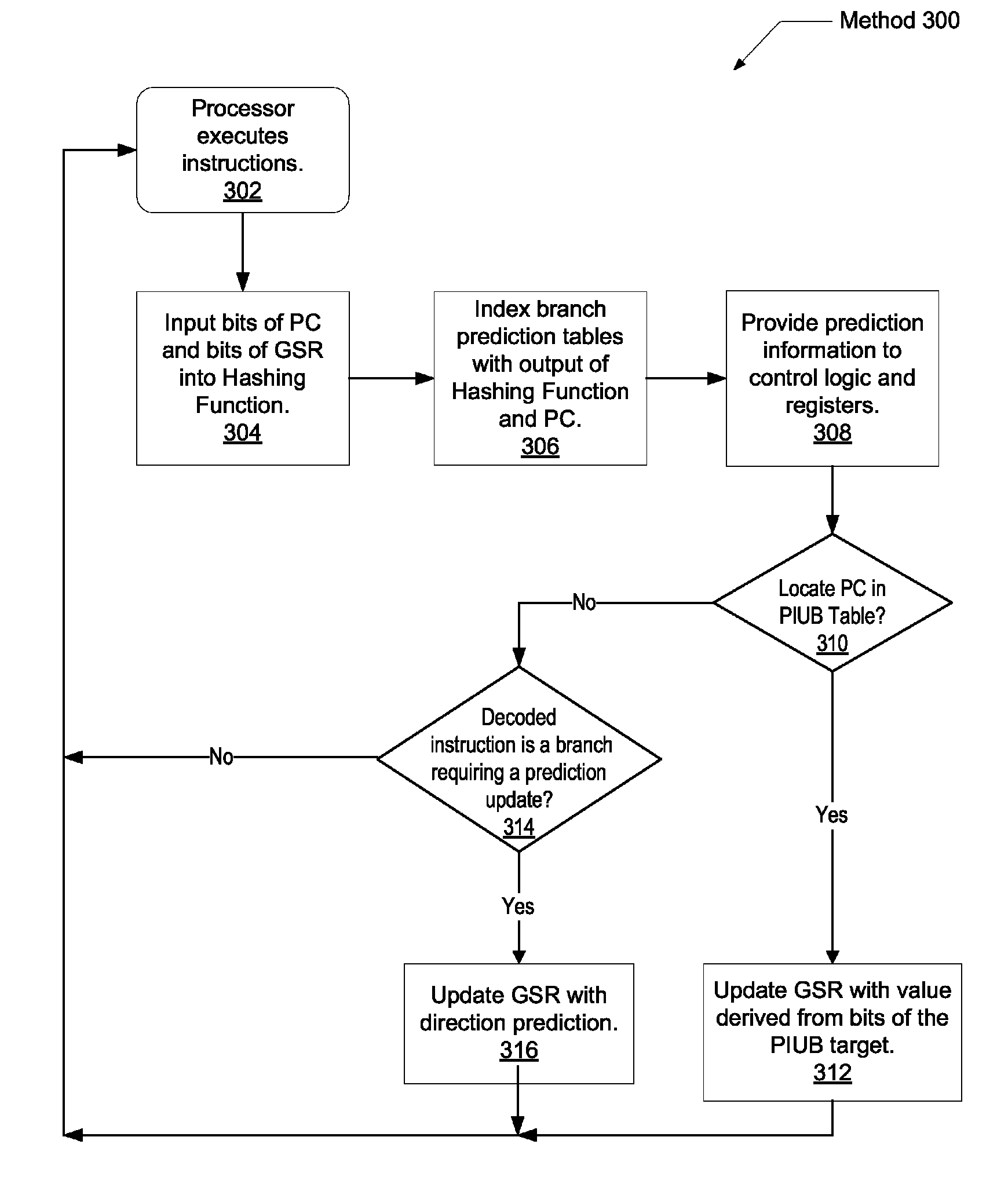

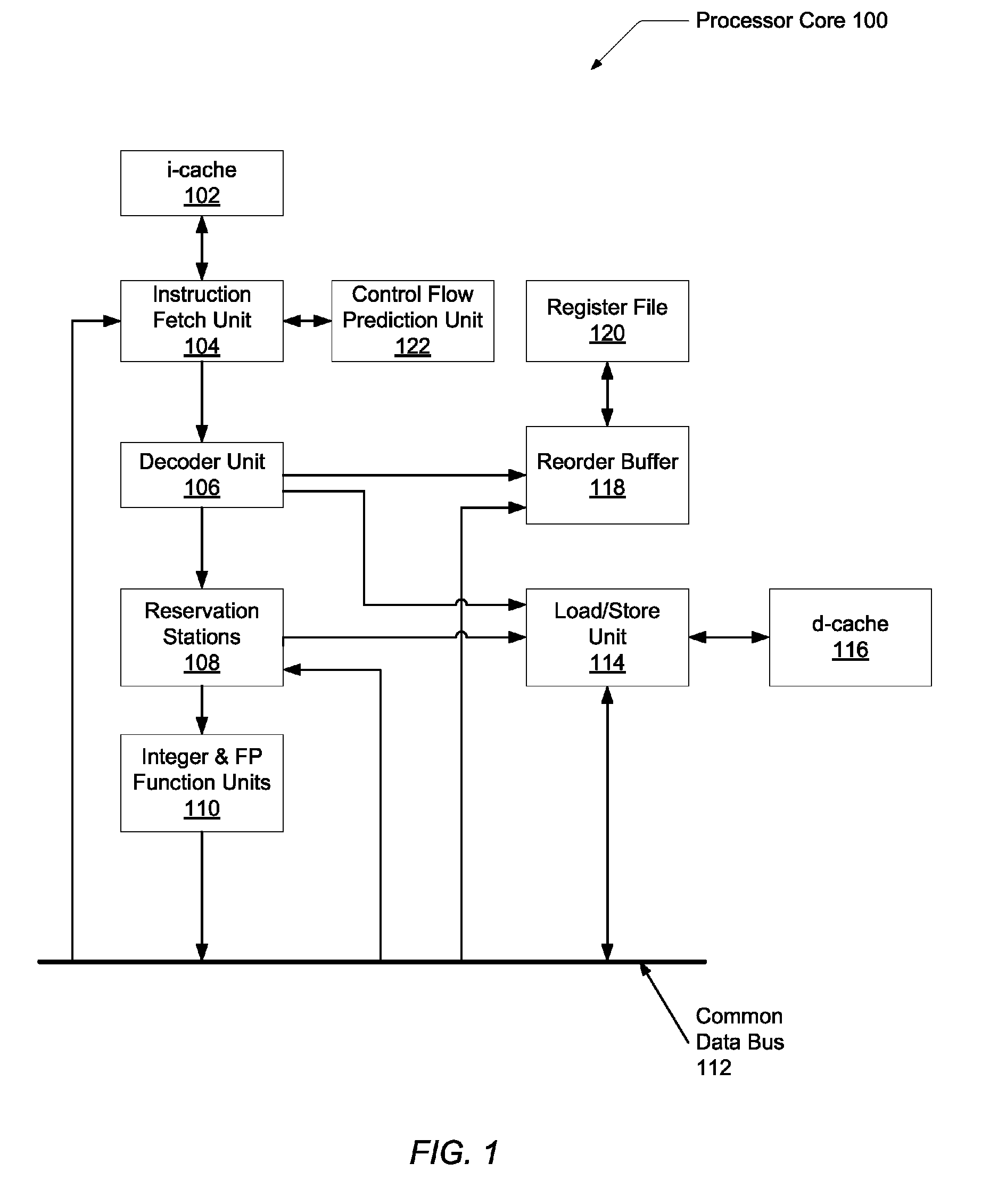

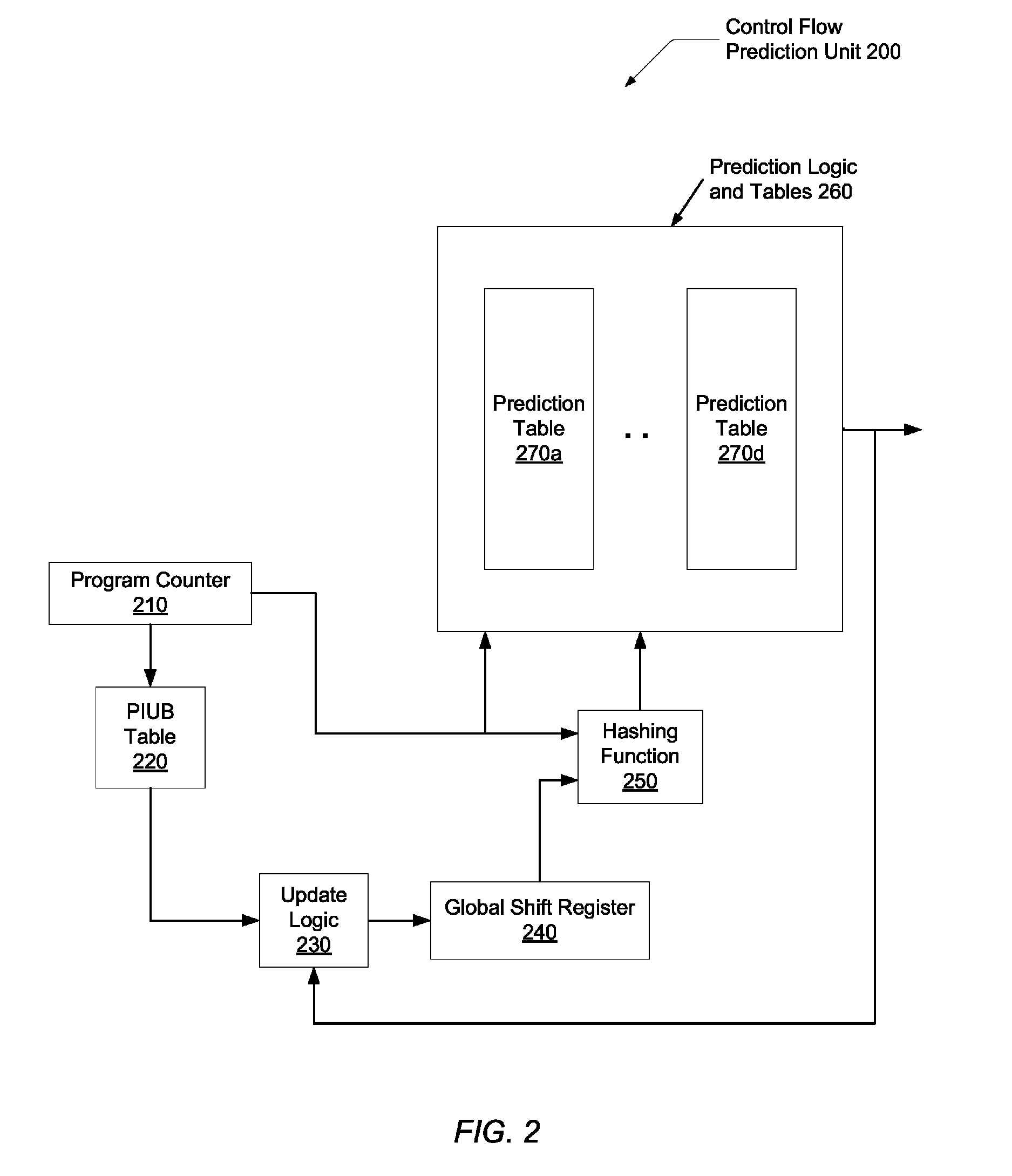

Branch history with polymorphic indirect branch information

ActiveUS20090164766A1Improve accuracyImprove forecast accuracyDigital computer detailsConcurrent instruction executionTarget arrayShift register

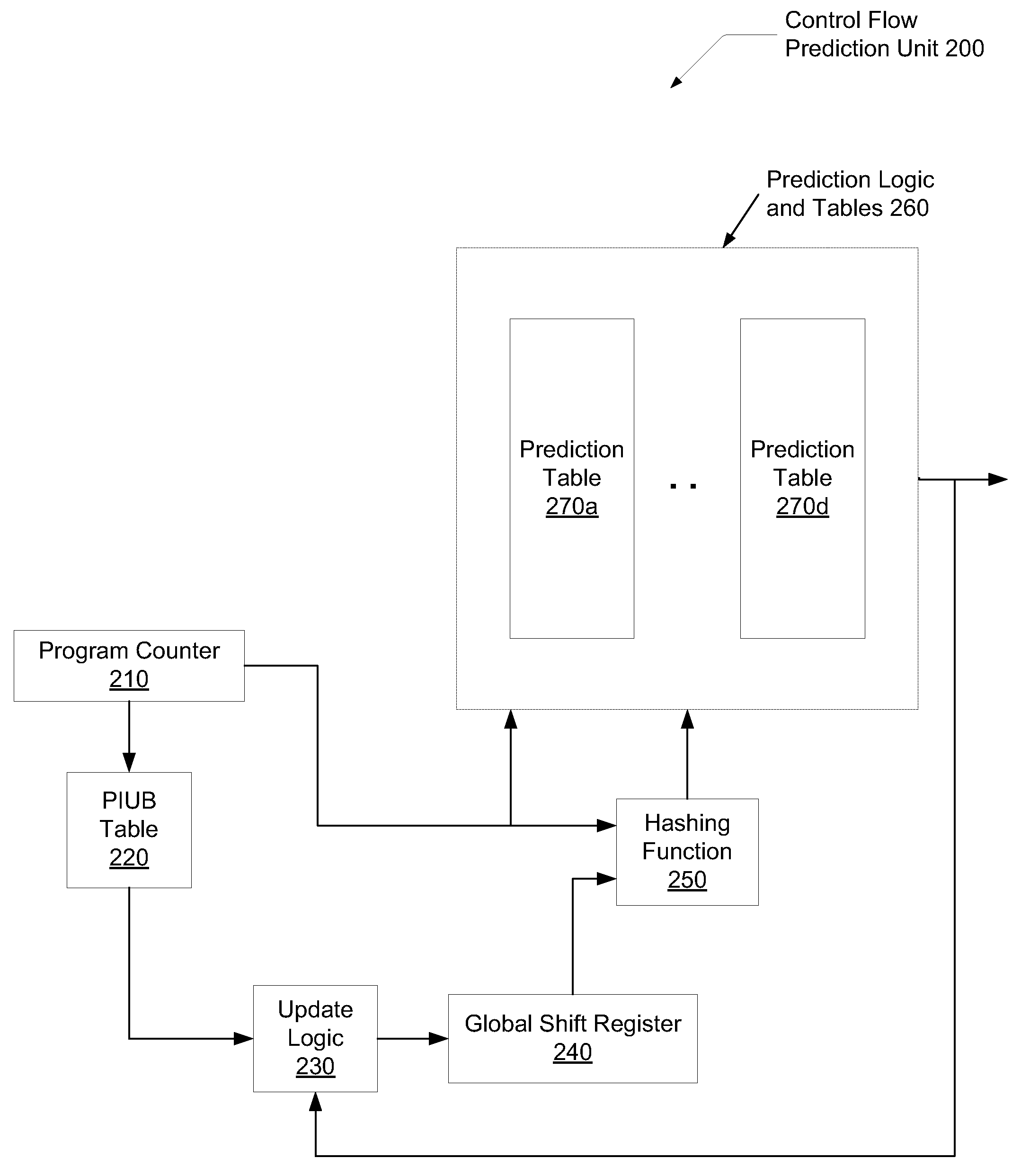

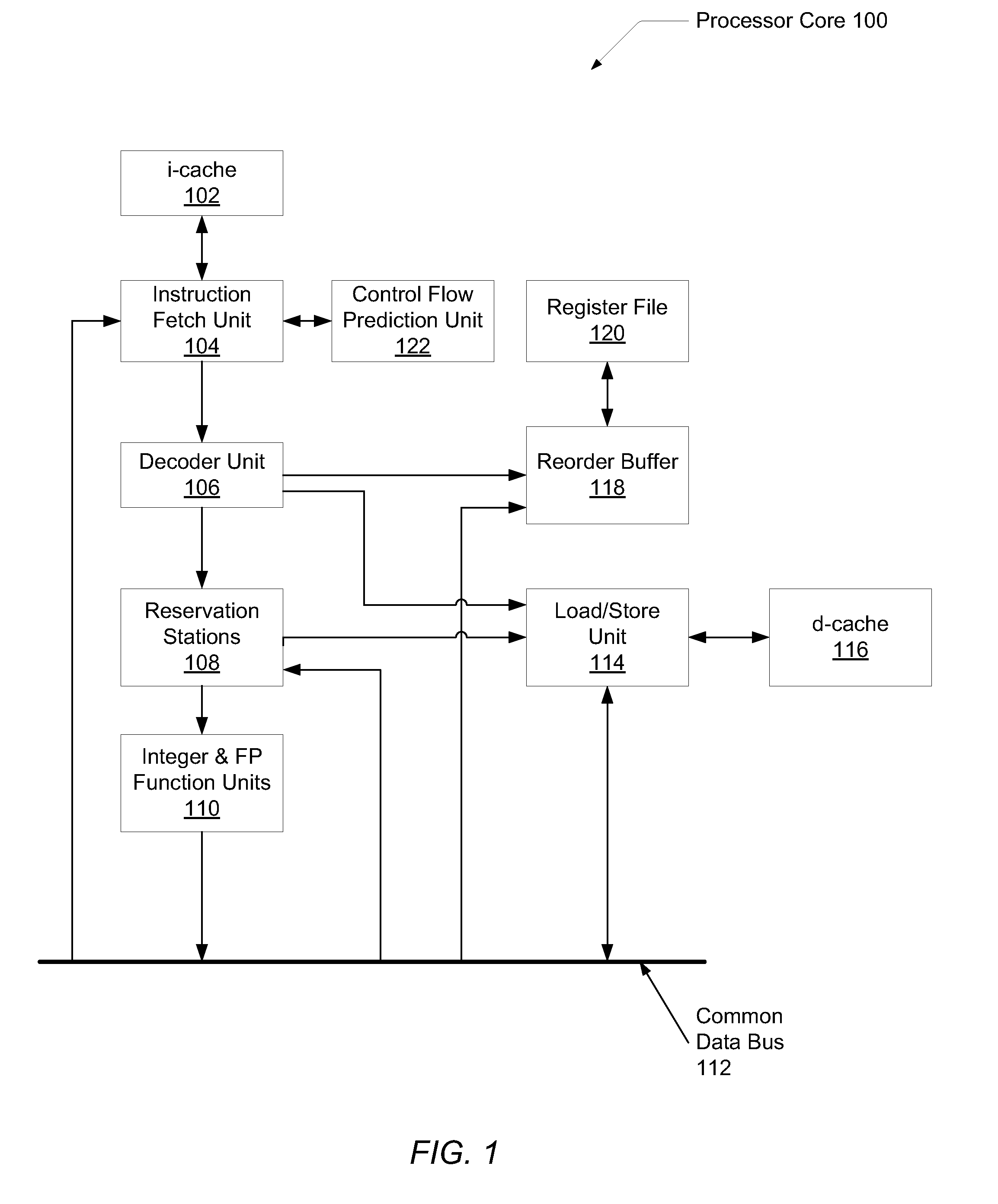

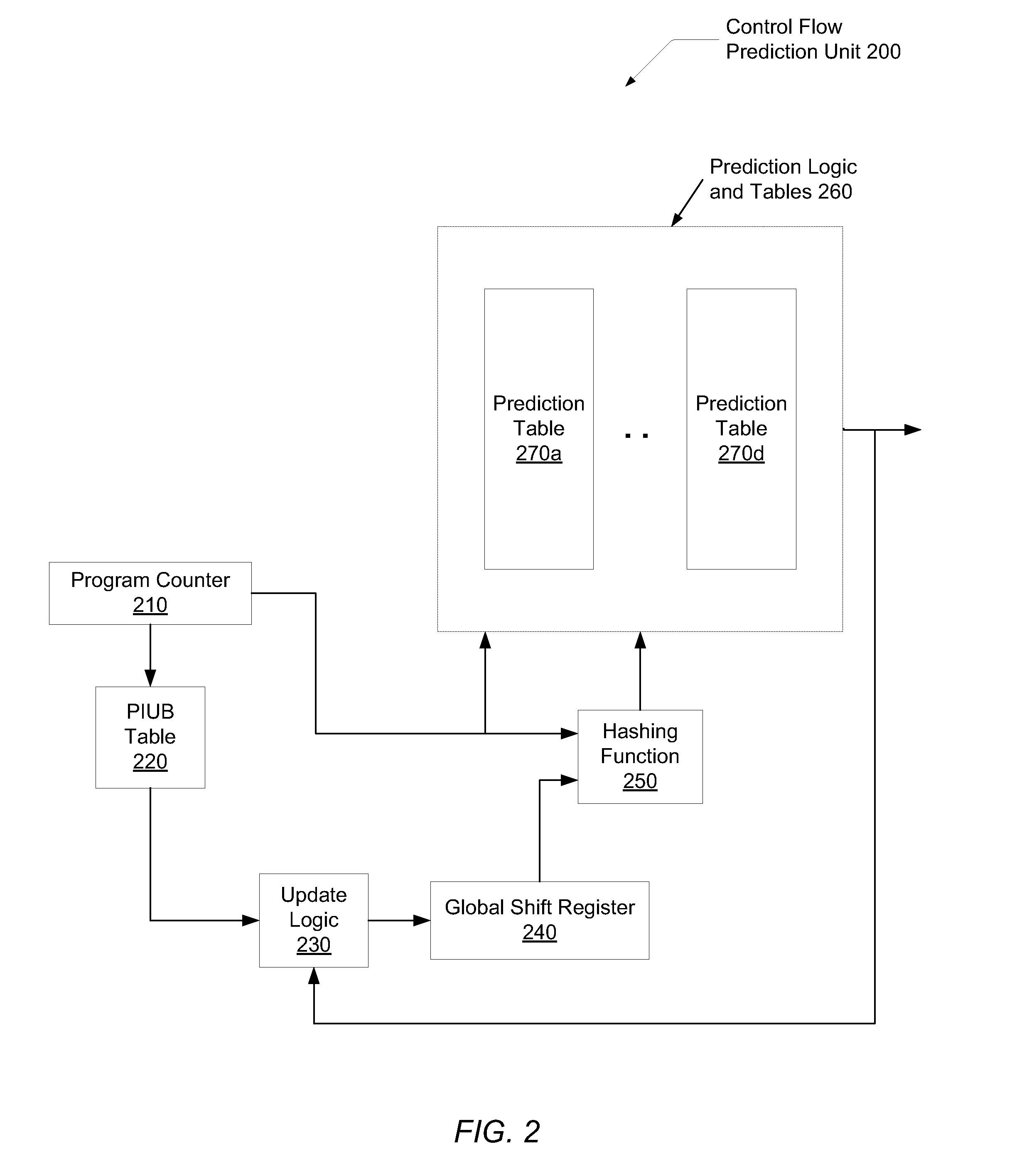

A system and method for efficient improvement of branch prediction in a microprocessor with negligible impact on die-area, power consumption, and clock cycle period. It is determined if a program counter (PC) register contains a polymorphic indirect unconditional branch (PIUB) instruction. One determination may be searching a table with a portion or all of a PC of past PIUB instructions. If a hit occurs in this table, the global shift register (GSR) is updated by shifting a portion of the branch target address into the GSR, rather than updating the GSR with a taken / not-taken prediction bit. The stored value in the GSR is input into a hashing function along with the PC in order to index prediction tables such as a pattern history table (PHT), a branch target buffer (BTB), an indirect target array, or other. The updated value due to the PIUB instruction improves the accuracy of the prediction tables.

Owner:ADVANCED MICRO DEVICES INC

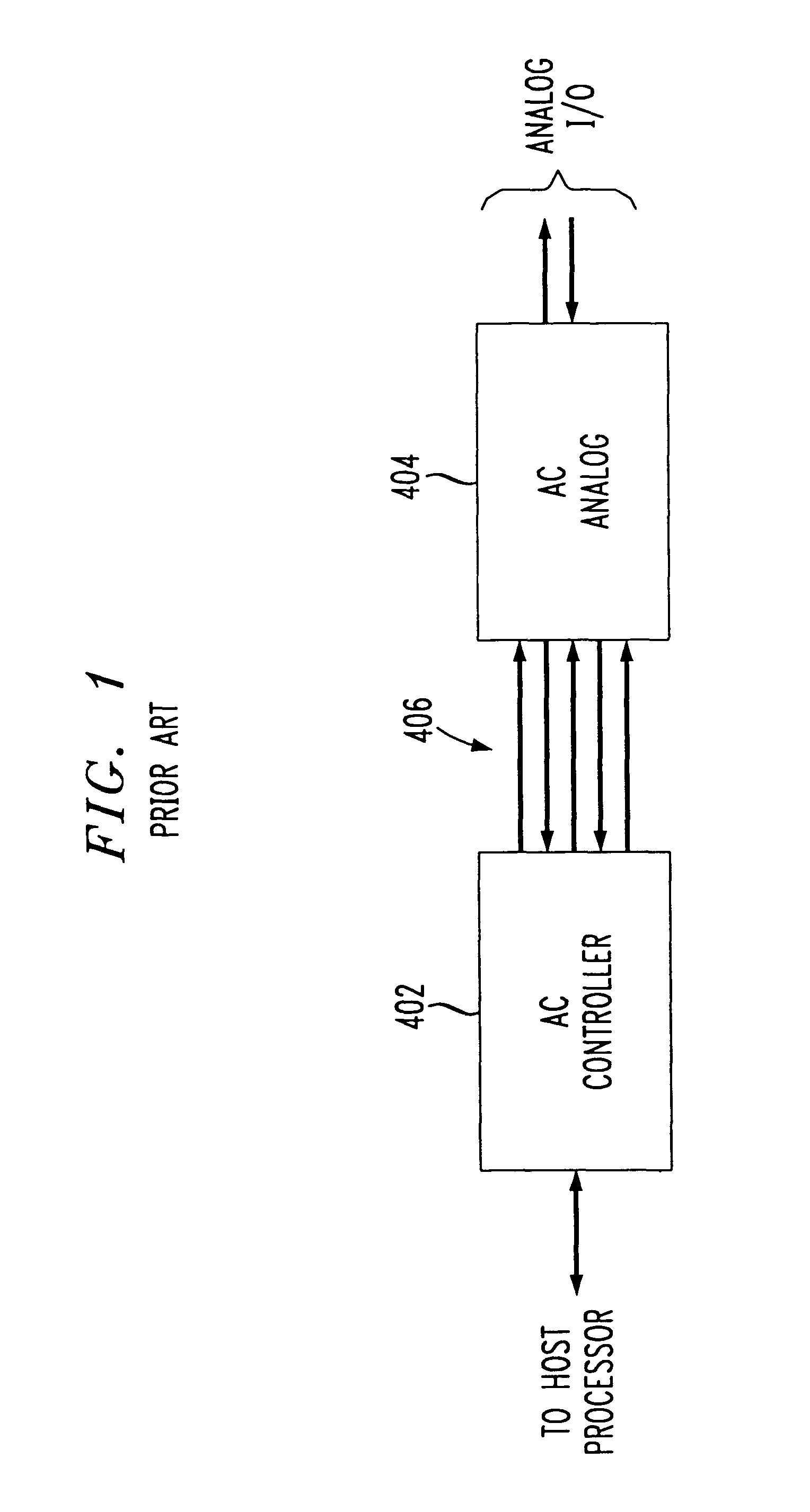

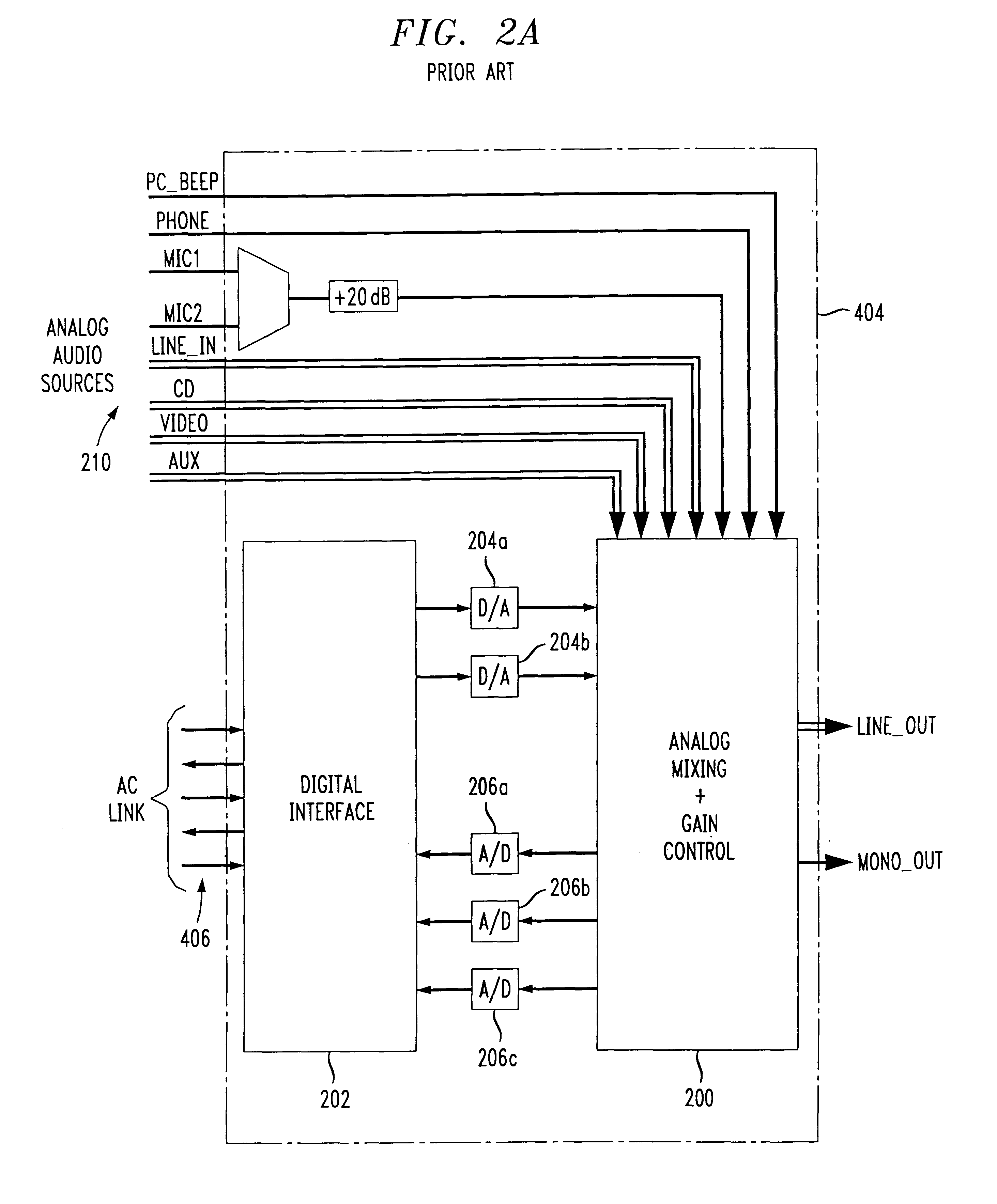

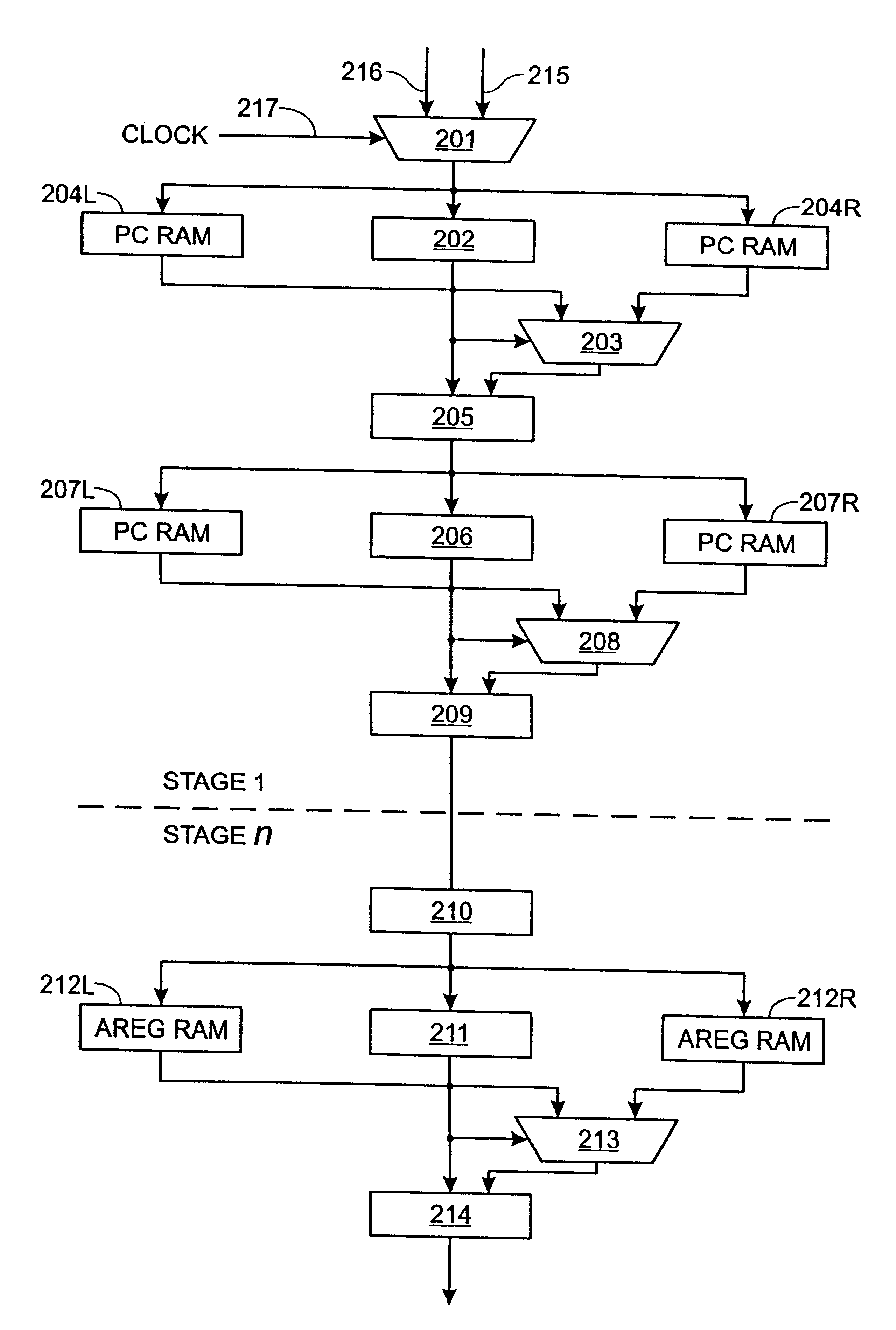

System for digital filtering in a fixed number of clock cycles

InactiveUS6175849B1Digital technique networkComplex mathematical operationsIir filteringState variable

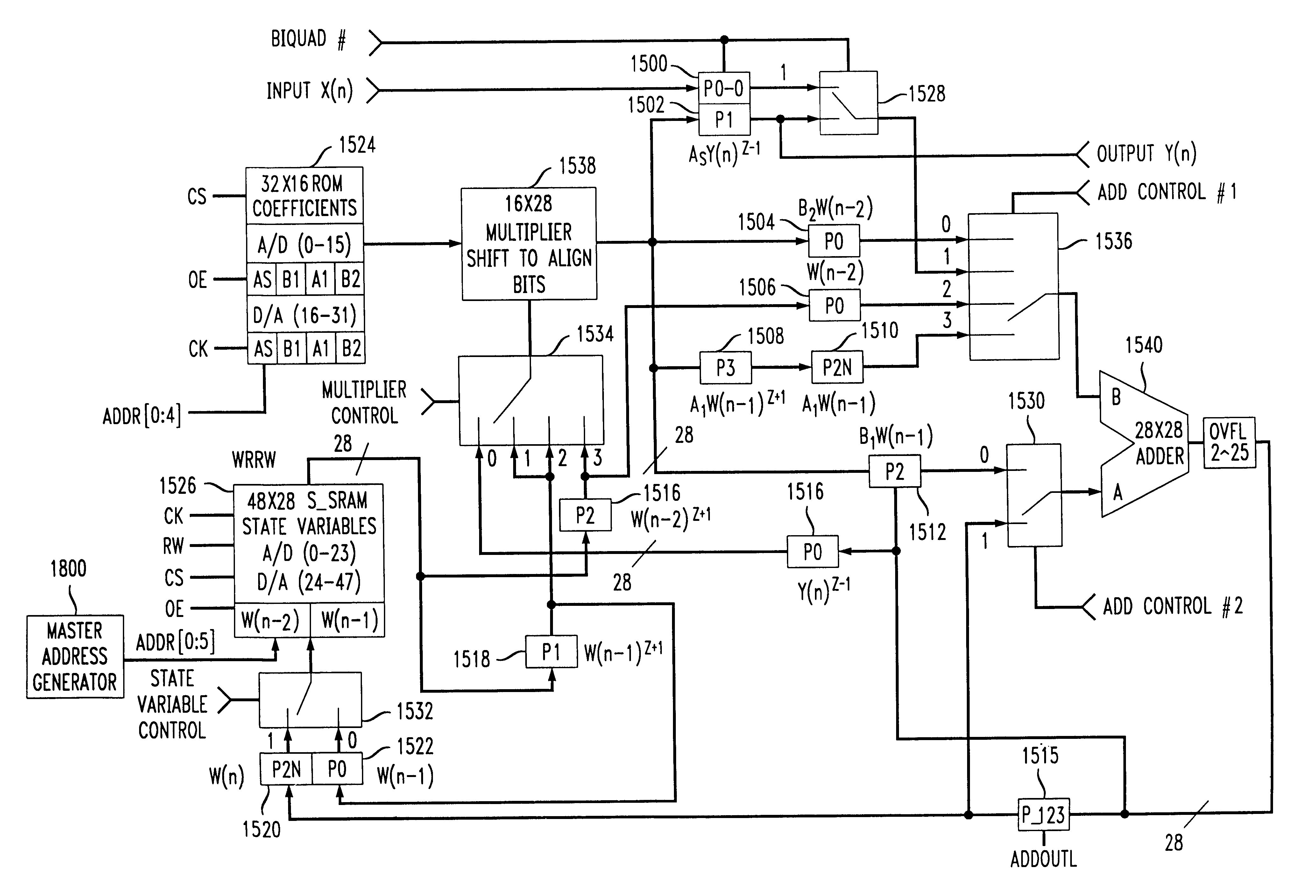

An integrated circuit, e.g. an AC '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a DC buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A RAM is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional modules of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional modules.

Owner:WSOU INVESTMENTS LLC +1

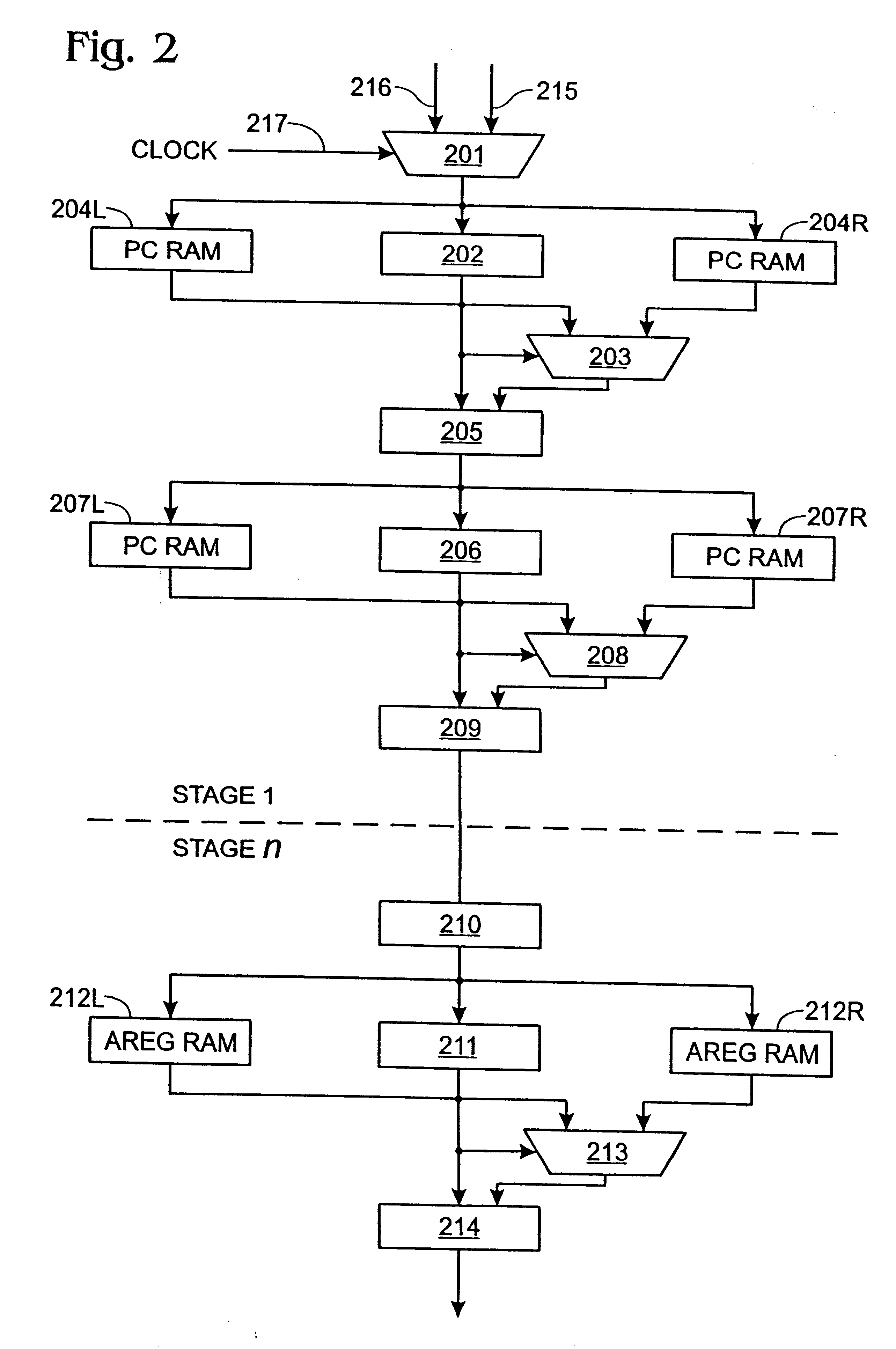

Distributed pipeline memory architecture for a computer system with even and odd pids

InactiveUS6209020B1General purpose stored program computerMultiprogramming arrangementsAccess timeComputerized system

A computer system architecture in which each processor has its own memory, strategically distributed along the stages of an execution pipeline of the processor, to provide fast access to often used information, such as the contents of the address and data registers, the program counter, etc. Memory storage is strategically located in close physical proximity to a stage in an execution pipeline at which memory is commonly or repeatedly accessed. Coupled to the pipeline at various stages are small memory cells for storing information that is consistently and repeatedly requested at that stage in the execution pipeline. The speed of the execution pipeline in a processor is critical to overall performance of the processor and the computer architecture of the present invention as a whole. To that end, the clock cycle time at which the pipeline is operated is increased as much as the operating characteristics of the logic and associated circuitry will allow. Generally, access times for memory are slower than the clock cycle times at which the pipeline logic can operate. Thus, there is a point of diminishing return at which increasing the clock cycle time of the pipeline is less advantageous if the pipeline must wait for memory access to complete. Thus, there is provided two sets of strategically located memory cells distributed along the execution pipeline of a processor, and alternately accesses the memory cells.

Owner:NORTEL NETWORKS LTD

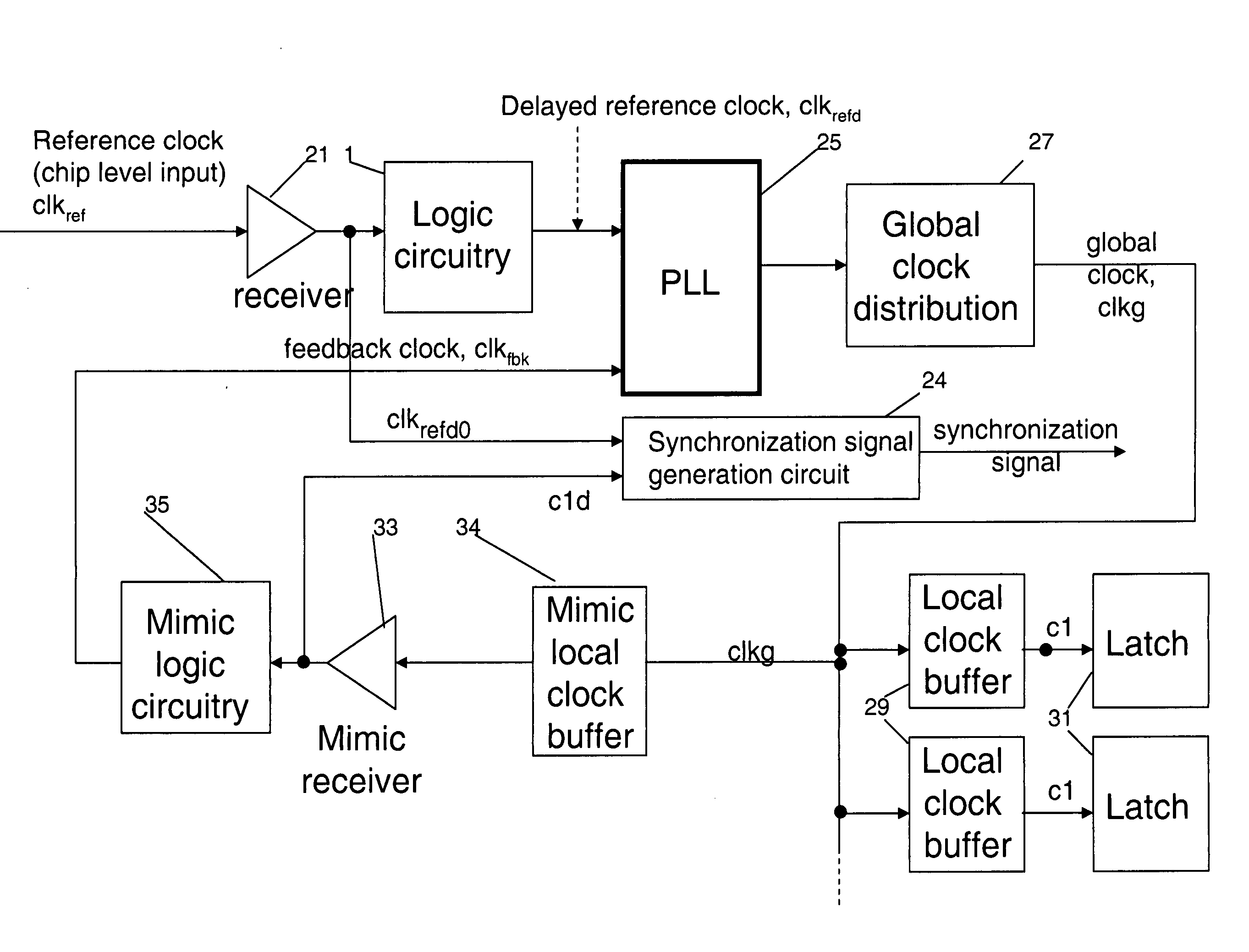

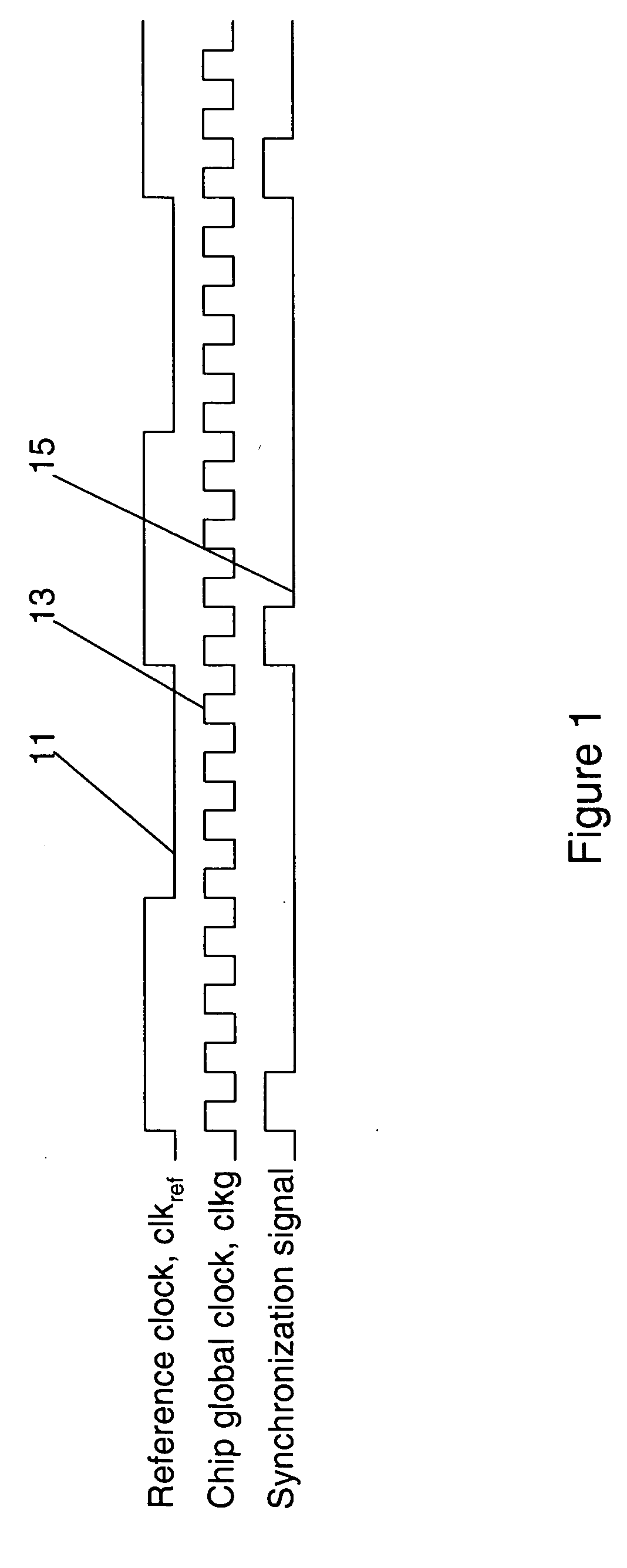

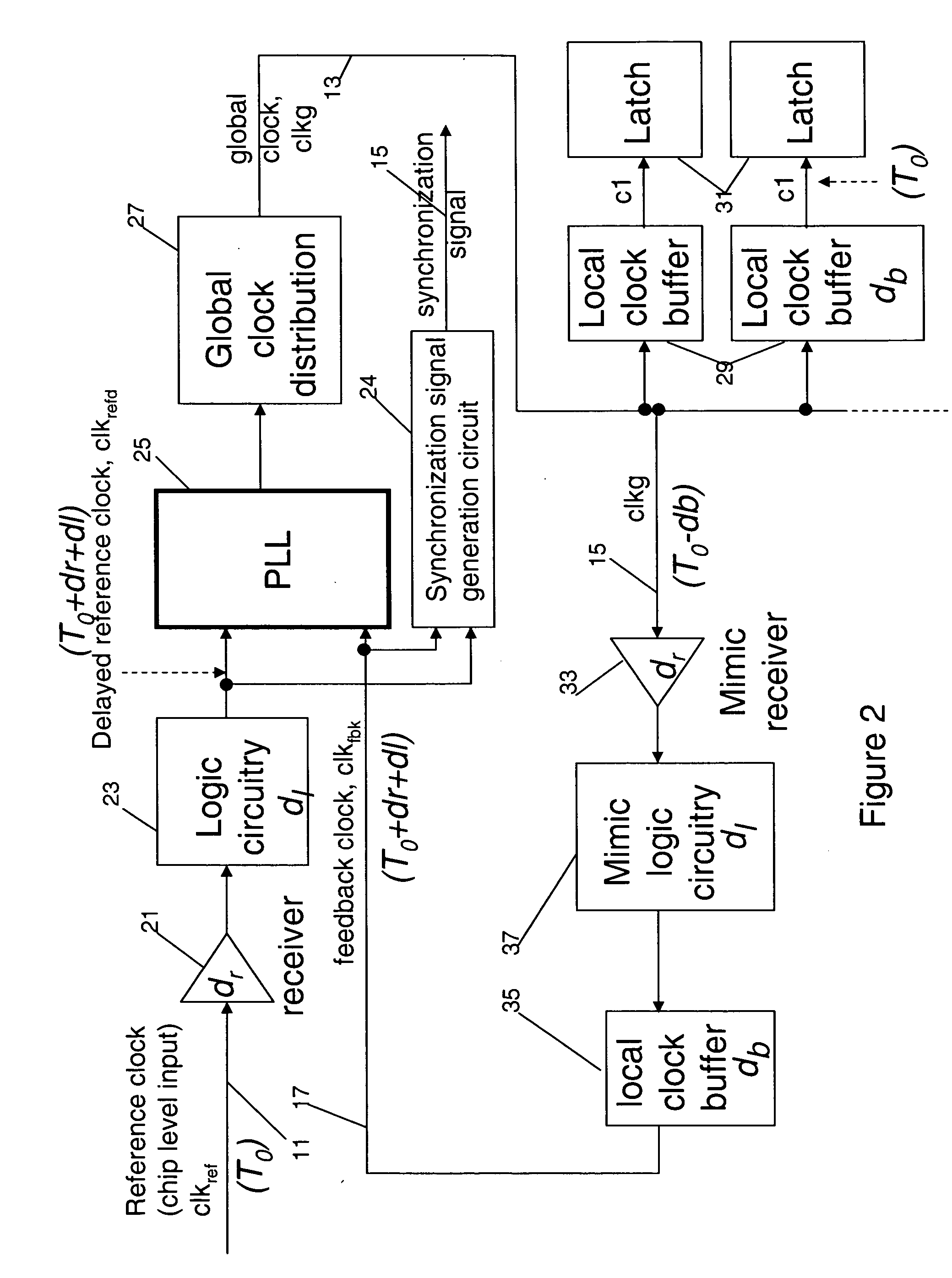

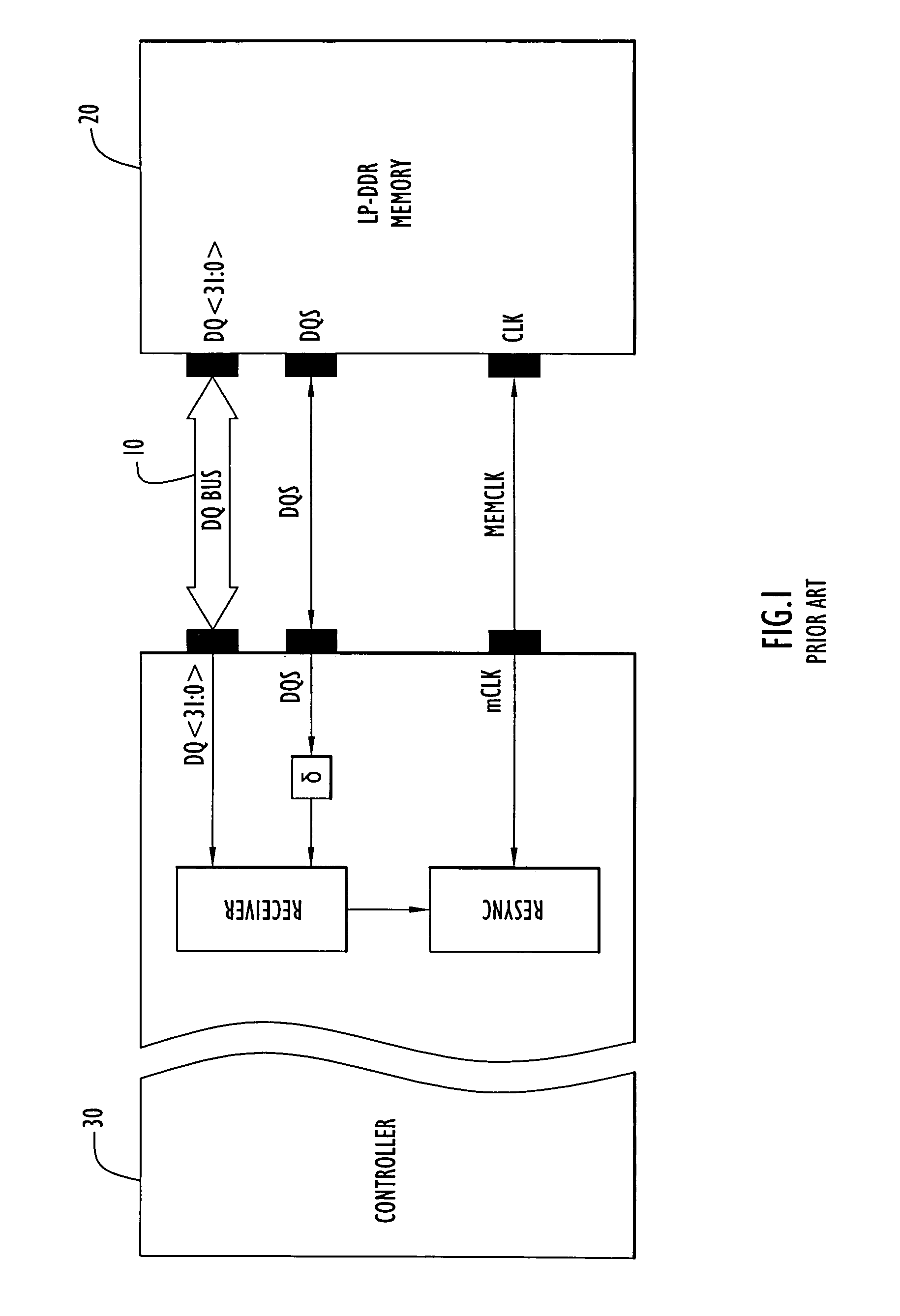

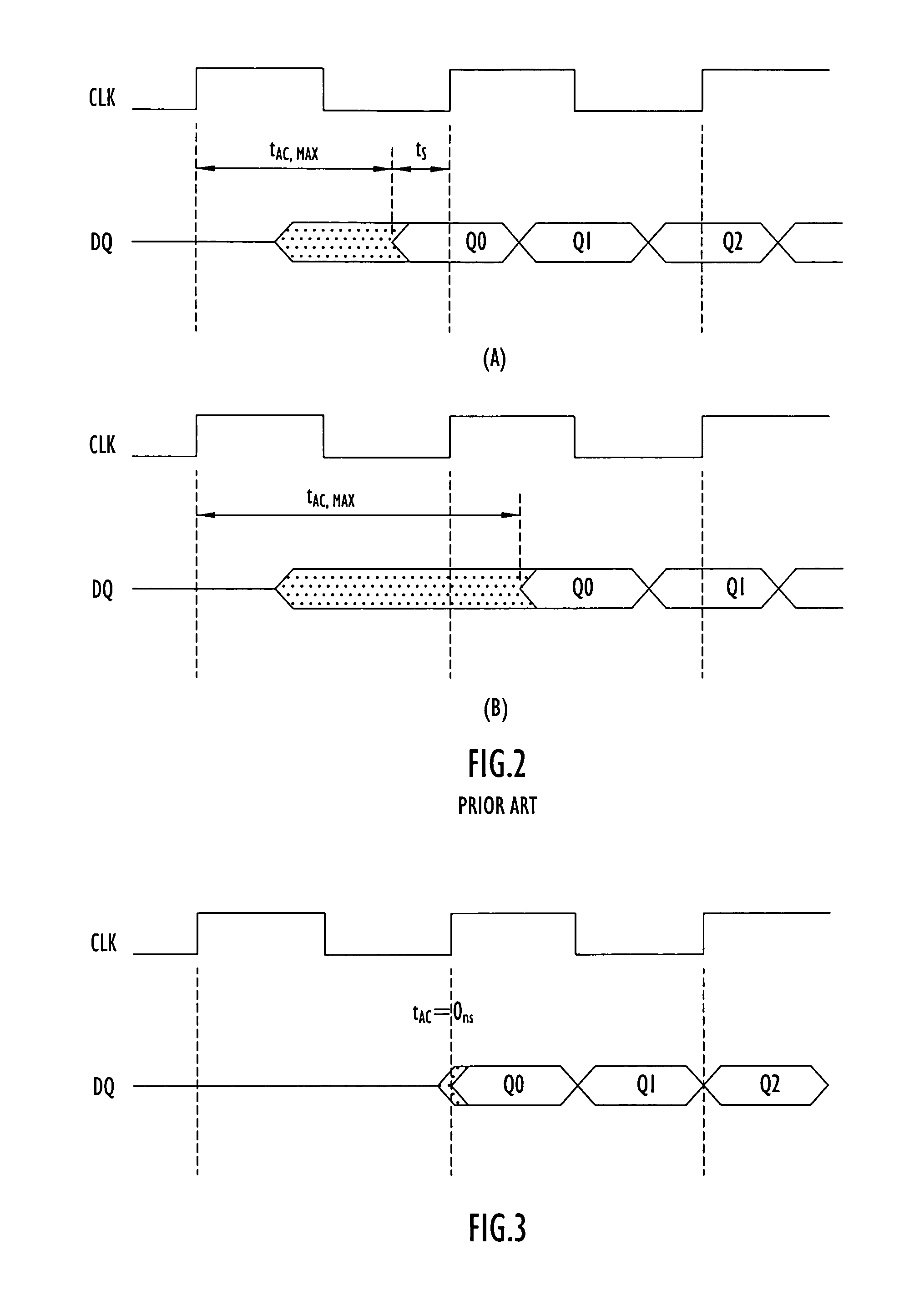

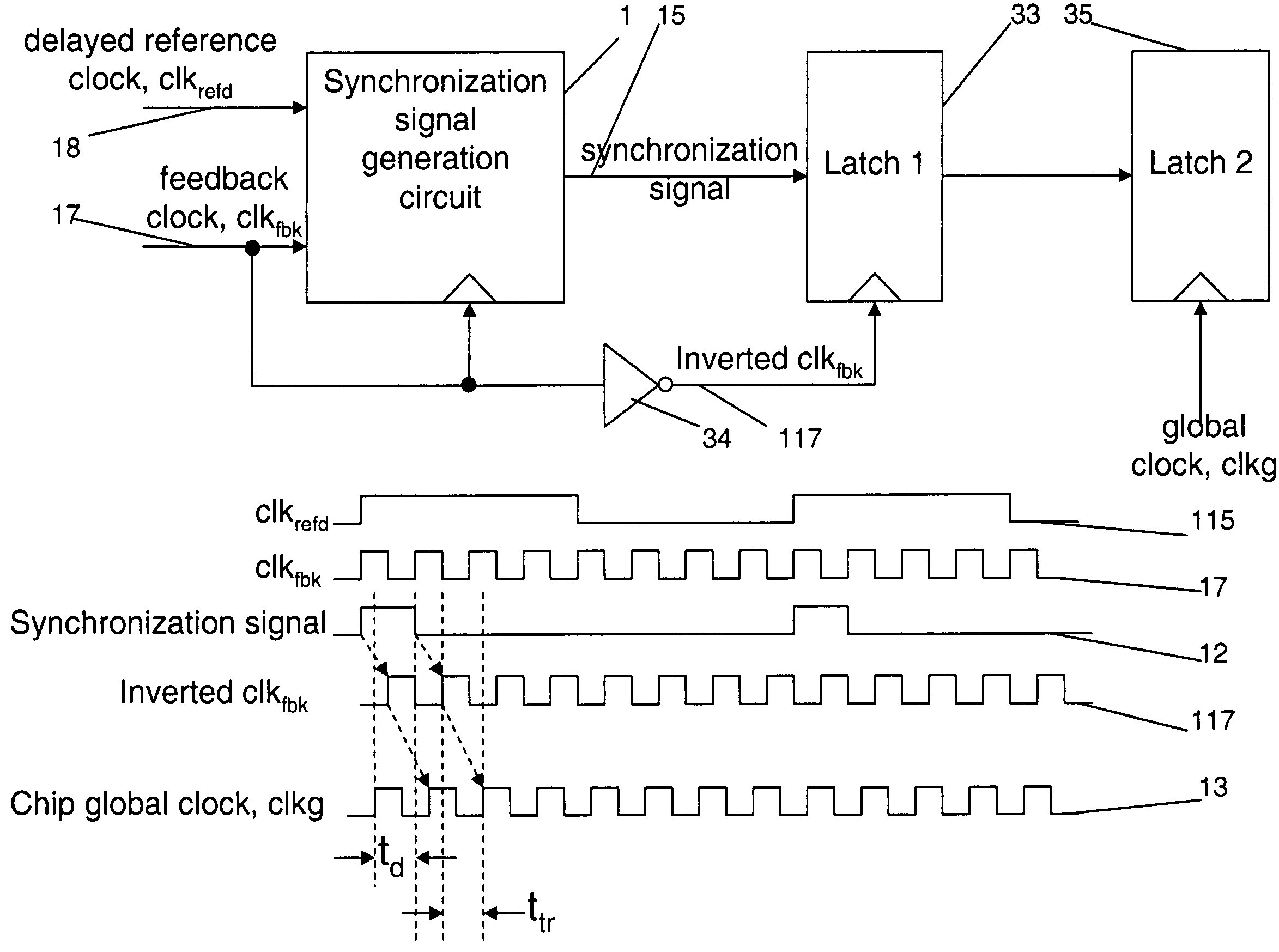

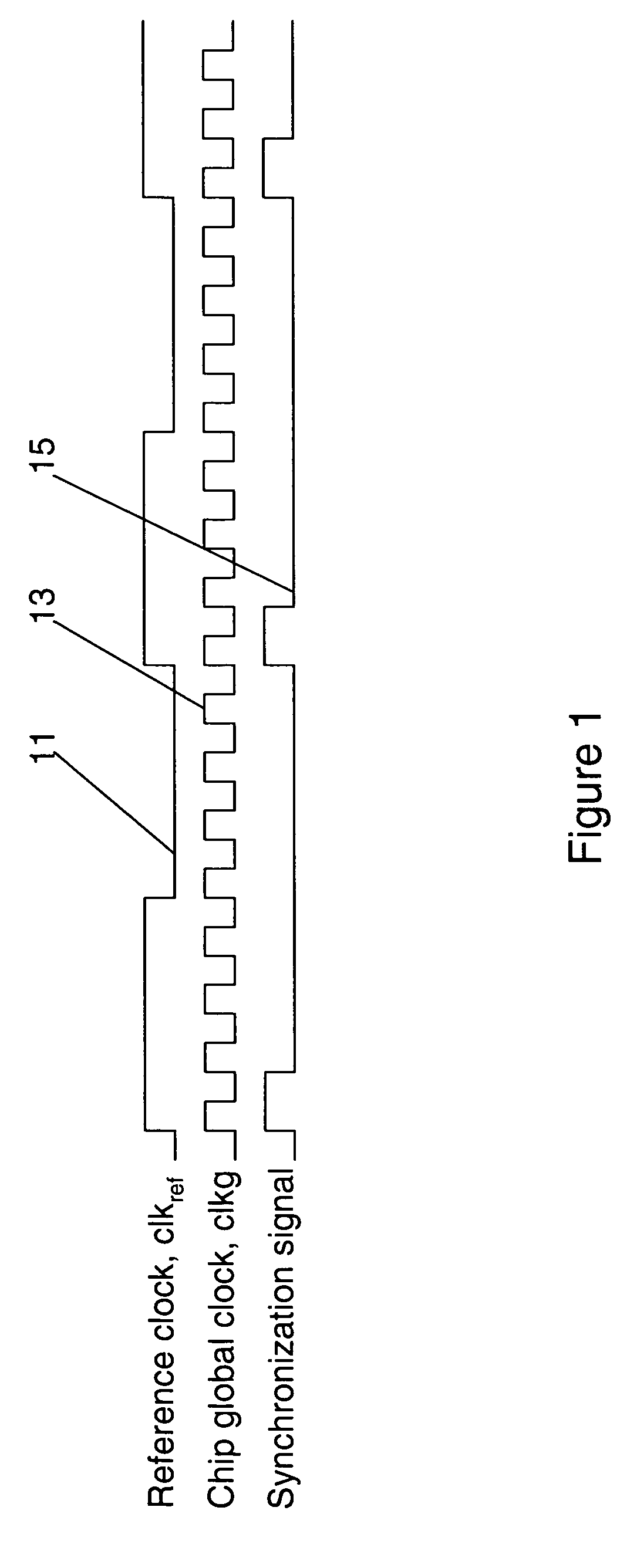

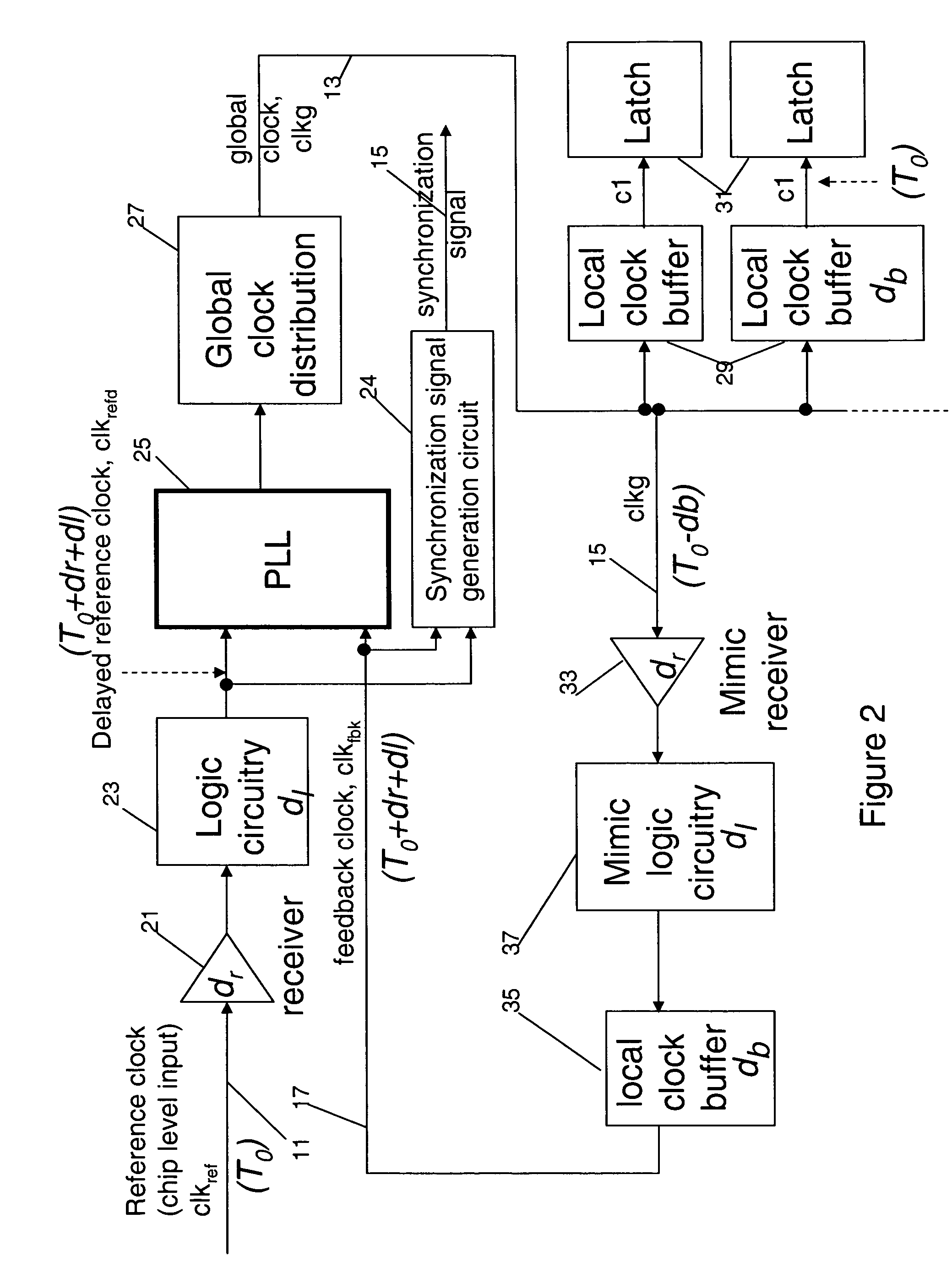

Method and apparatus for generating synchronization signals for synchronizing multiple chips in a system

InactiveUS20060182212A1Reduce time uncertaintyPromote generationPulse automatic controlSynchronisation signal speed/phase controlPhase differenceCycle time

A clock generator circuit for generating synchronization signals for a multiple chip system. The clock generator circuit comprises generation of a synchronization signal from a reference clock and chip global clock with edge detection logic. In high performance server system design with multiple chips, a common practice for server systems is to use feedback clock and delayed reference clock to generate the synchronization signal. The generated synchronization signal is transferred to latches clocked by the global clock to be used for chip synchronization functions. As the system clock frequency is pushed higher, the phase difference between generated synchronization signal clocked by feedback clock and receiving latch clocked by global clock is becoming such a large portion of cycle time that this signal cannot be transferred deterministically. This invention resolves the uncertainty problem and allows the synchronization signals to be generated deterministically independent of the chip global clock cycle time

Owner:IBM CORP

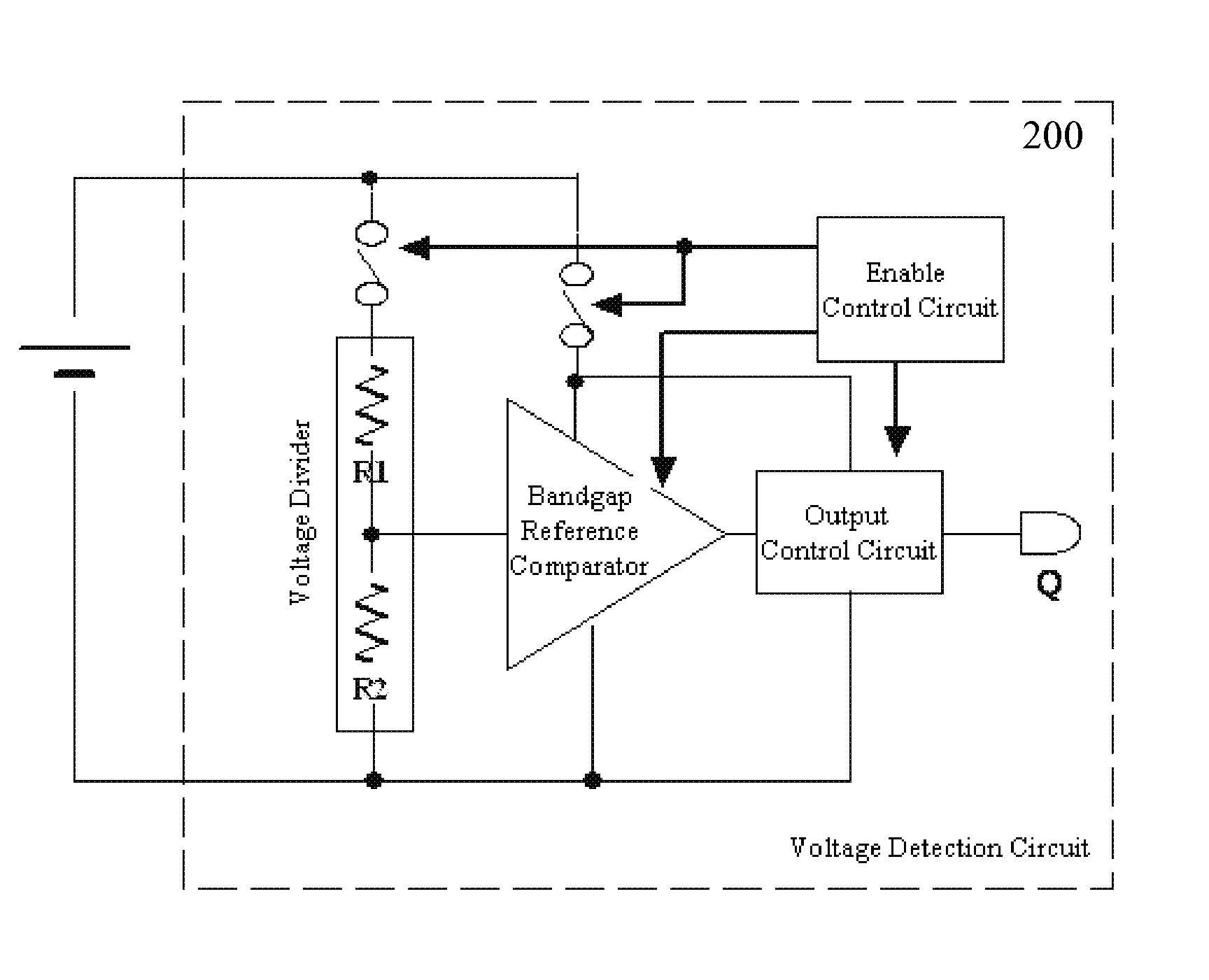

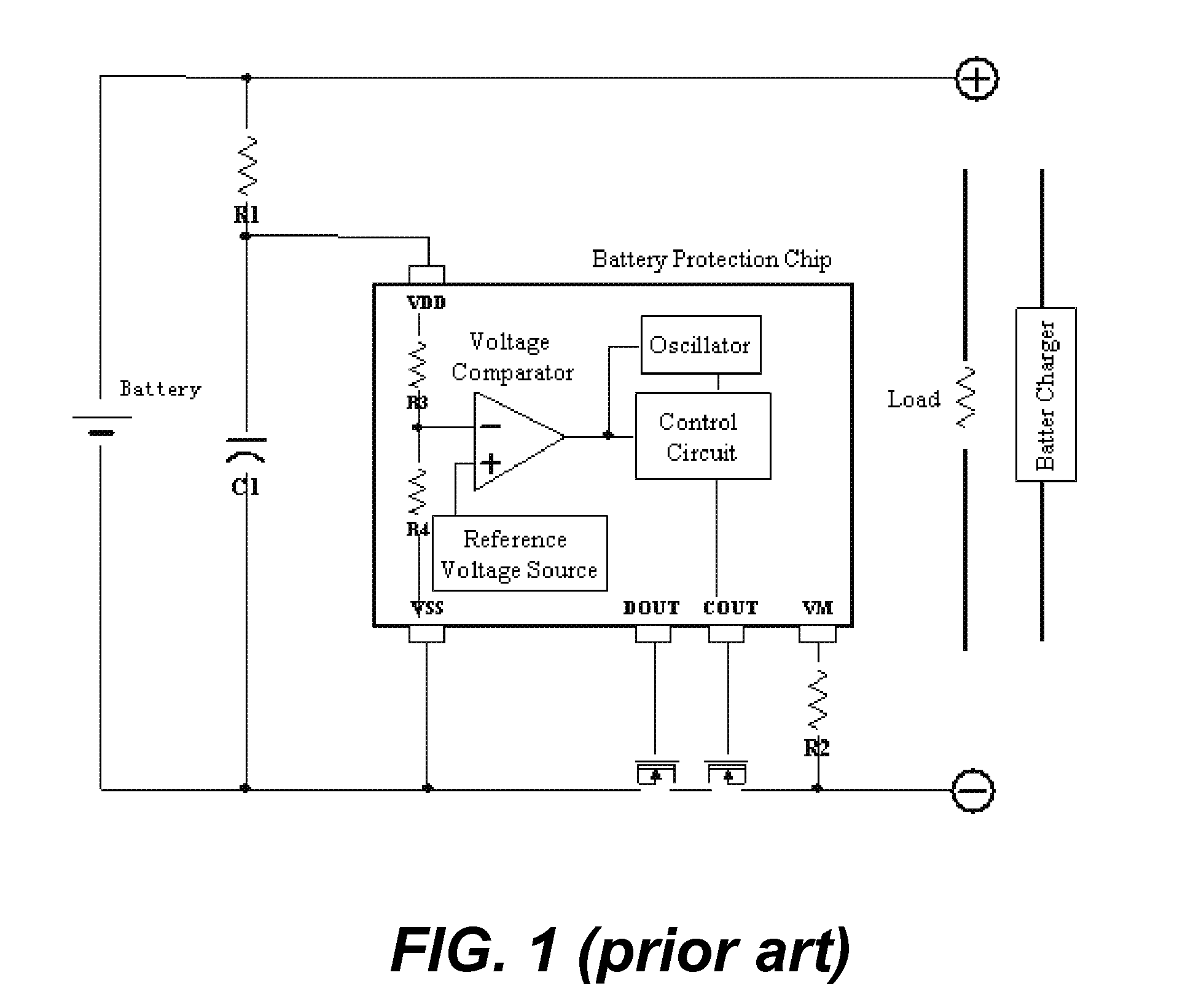

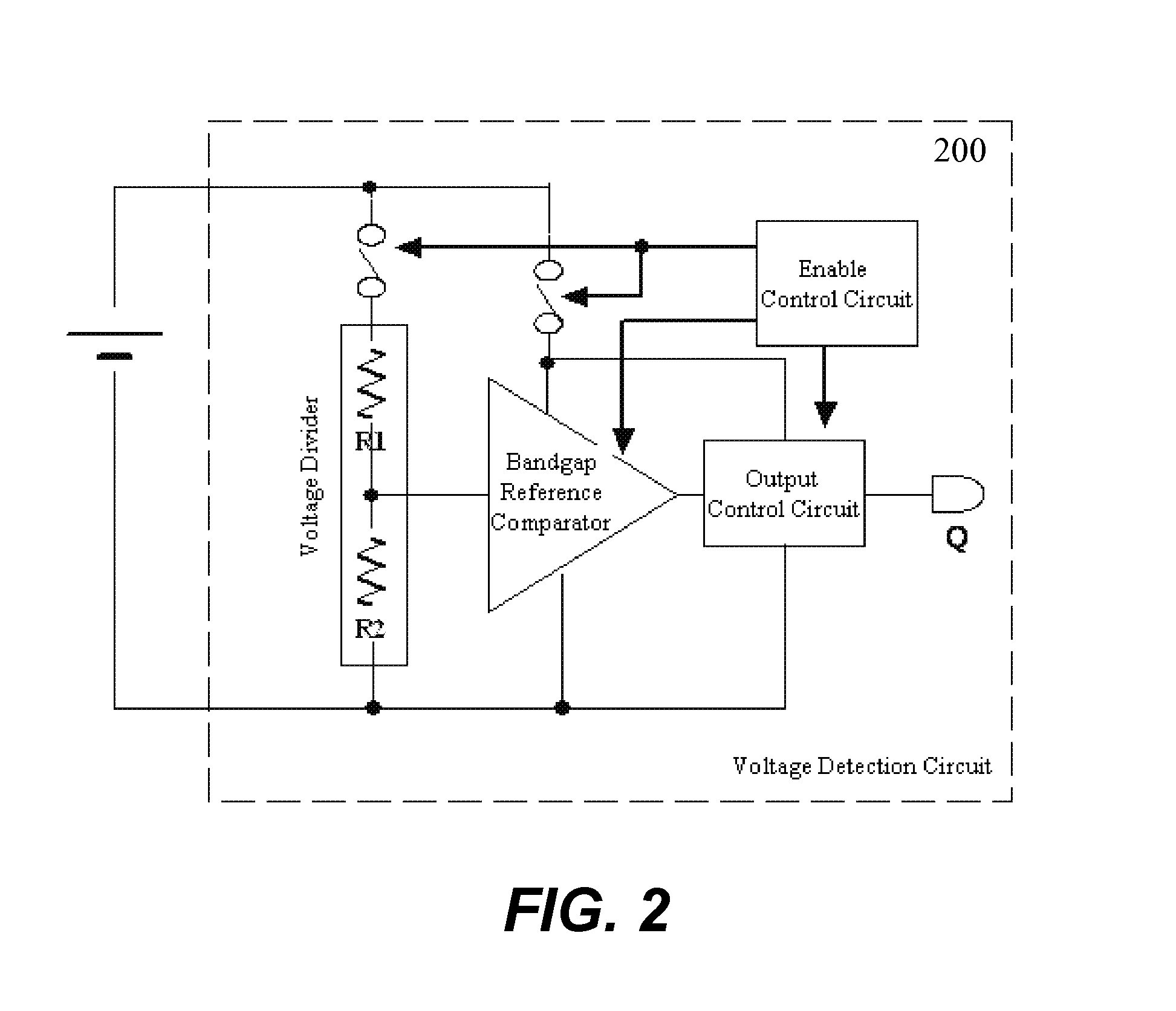

Accurate scan-mode voltage detection circuit

A scan mode is used in a voltage detection circuit. An oscillator in the circuit is always on and a system including the voltage detection circuit detects various abnormal conditions, such as overcharging, overdischarging and overcurrent one by one for some clocks. To reduce the power consumption, the voltage detection circuit is turned on only once for several clocks. The on-time is very short and lasts about only one tenth of a clock cycle time. In other times, the voltage detection circuit is turned off to save power consumption.

Owner:VIMICRO CORP

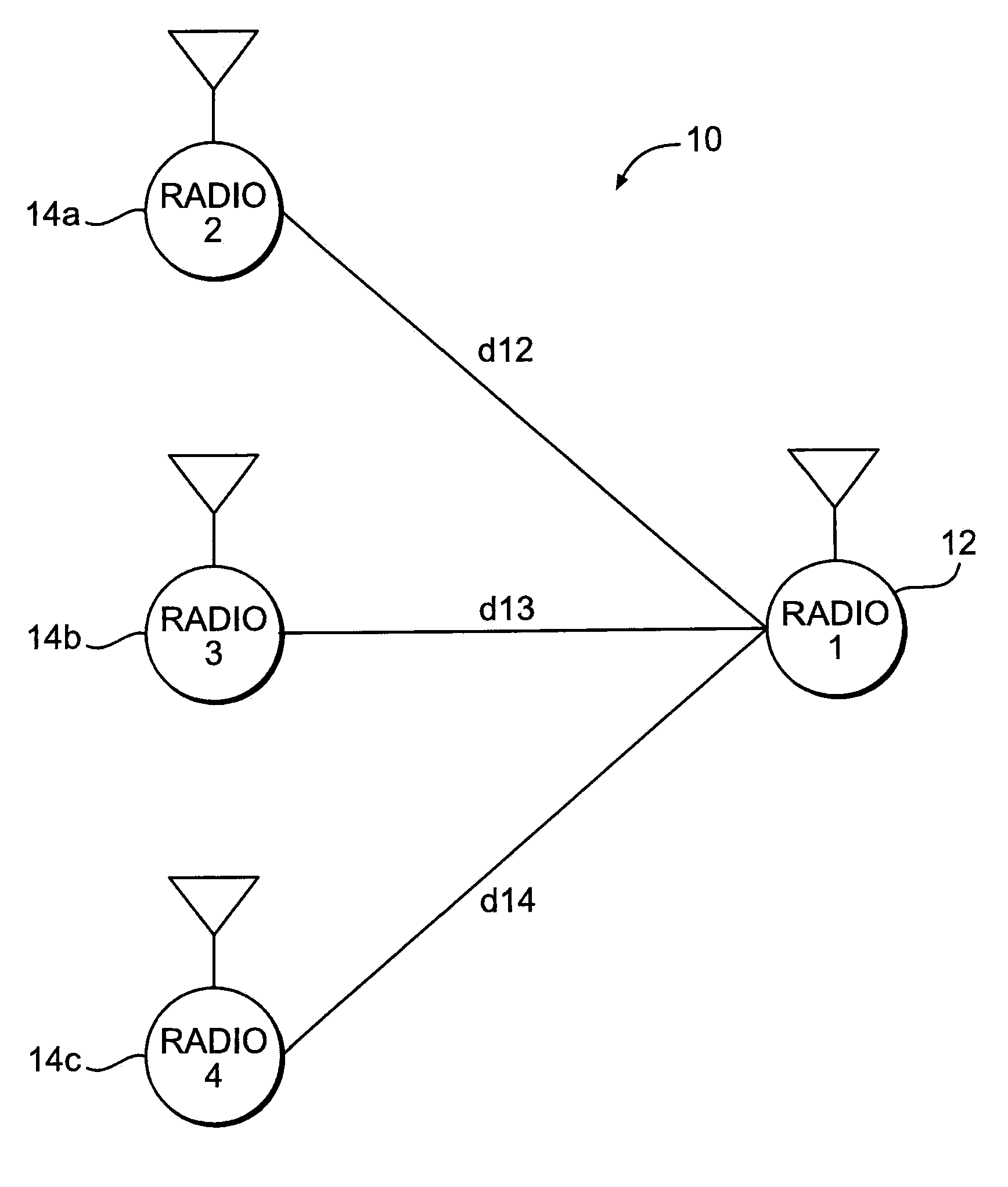

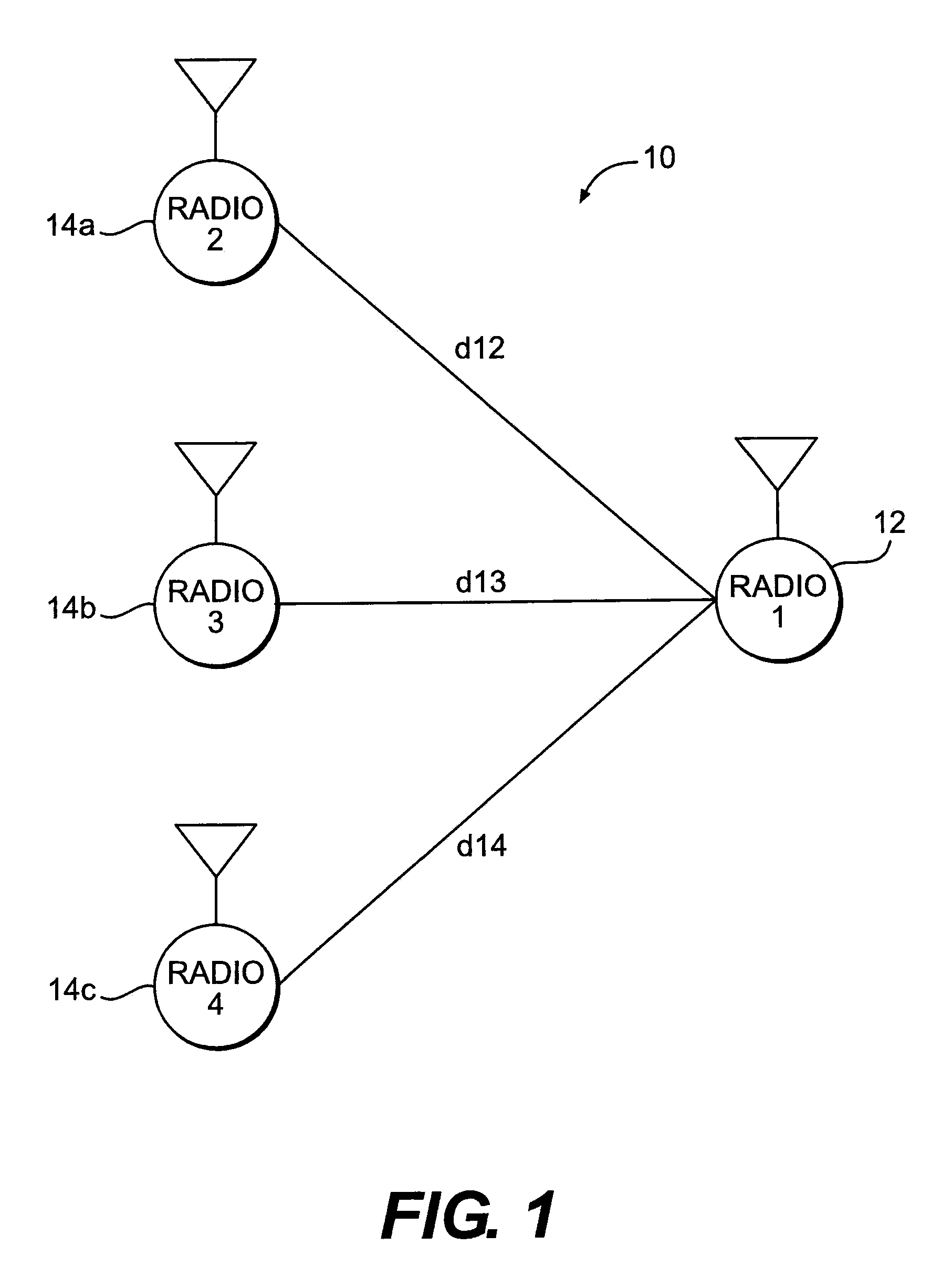

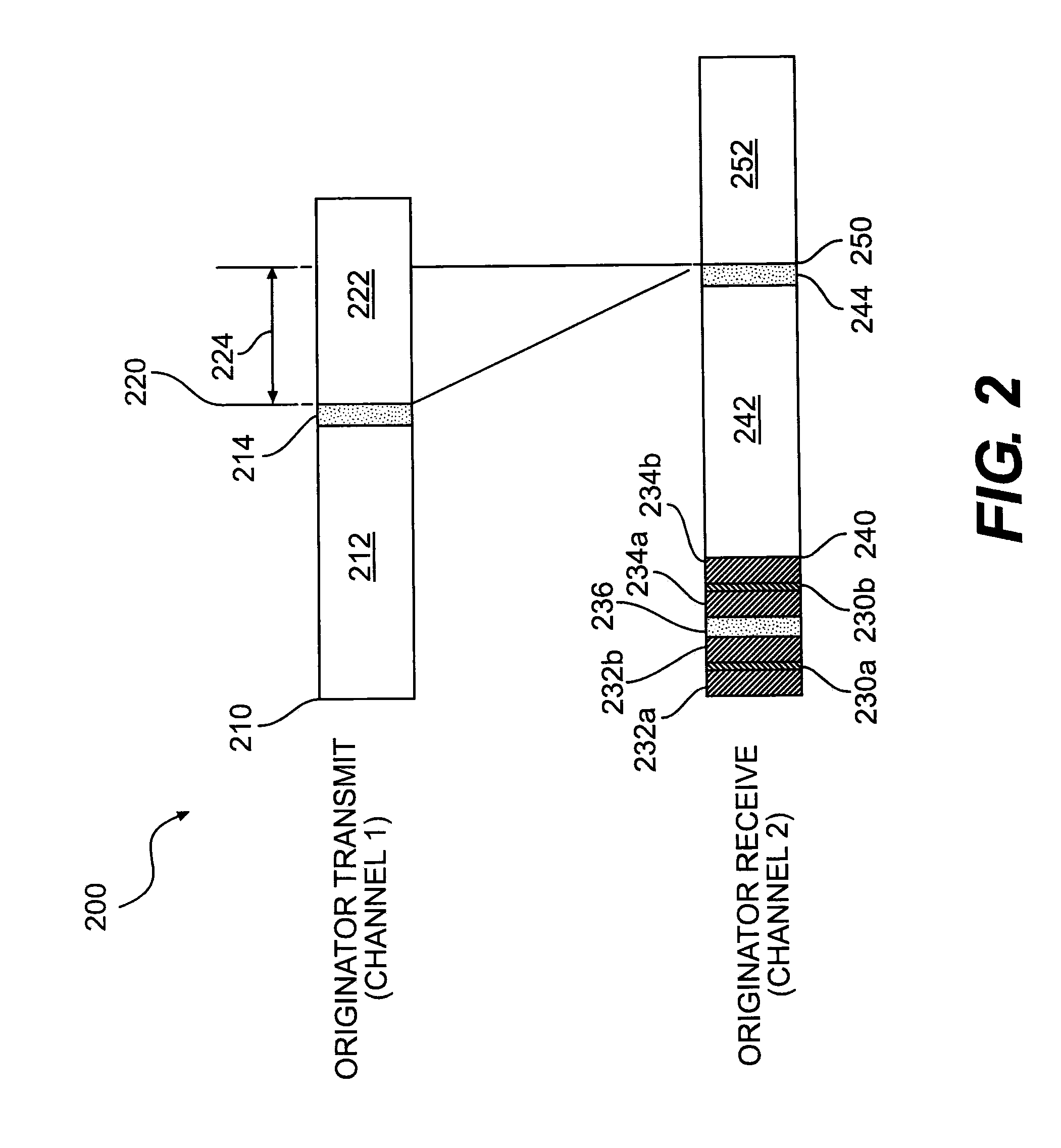

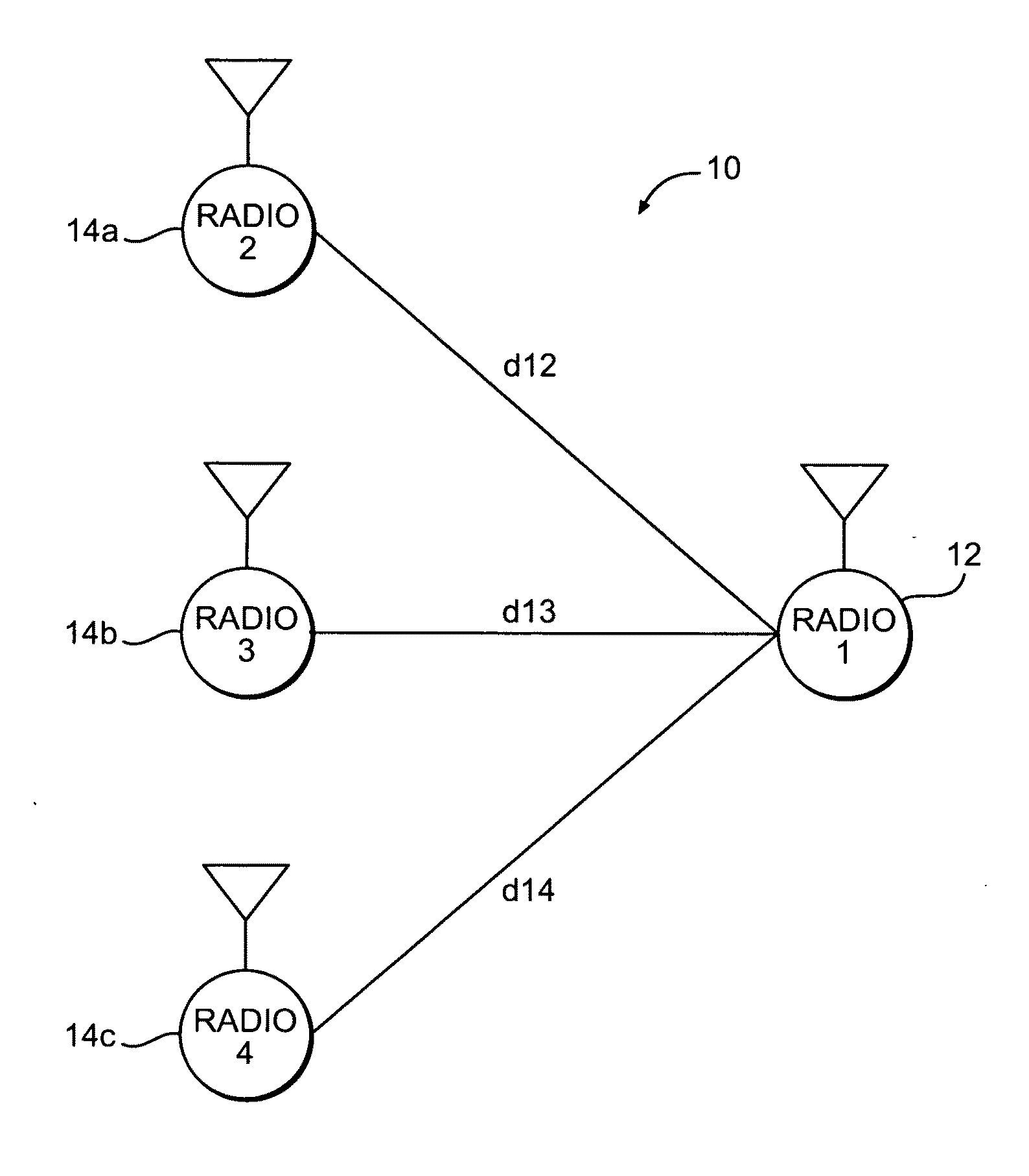

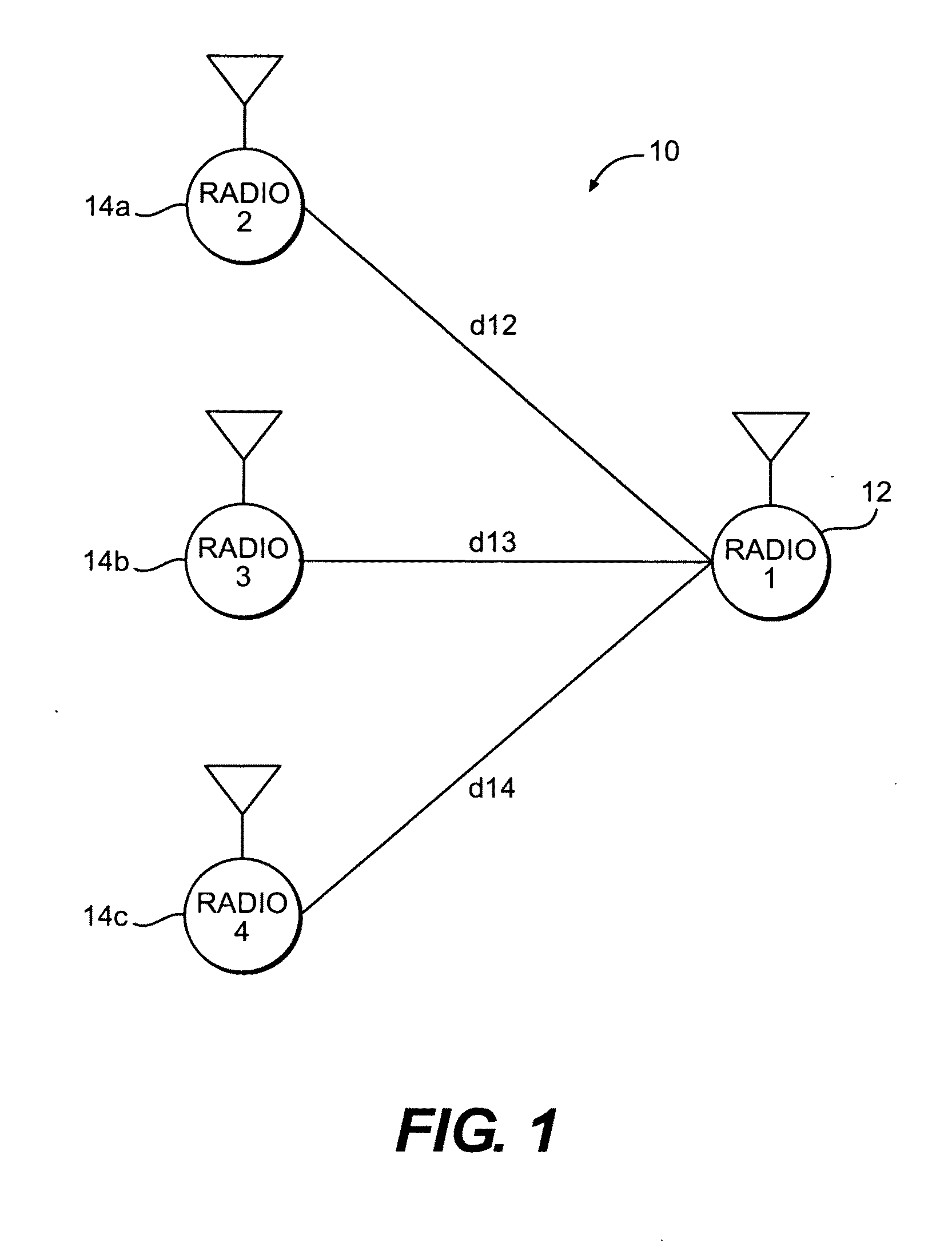

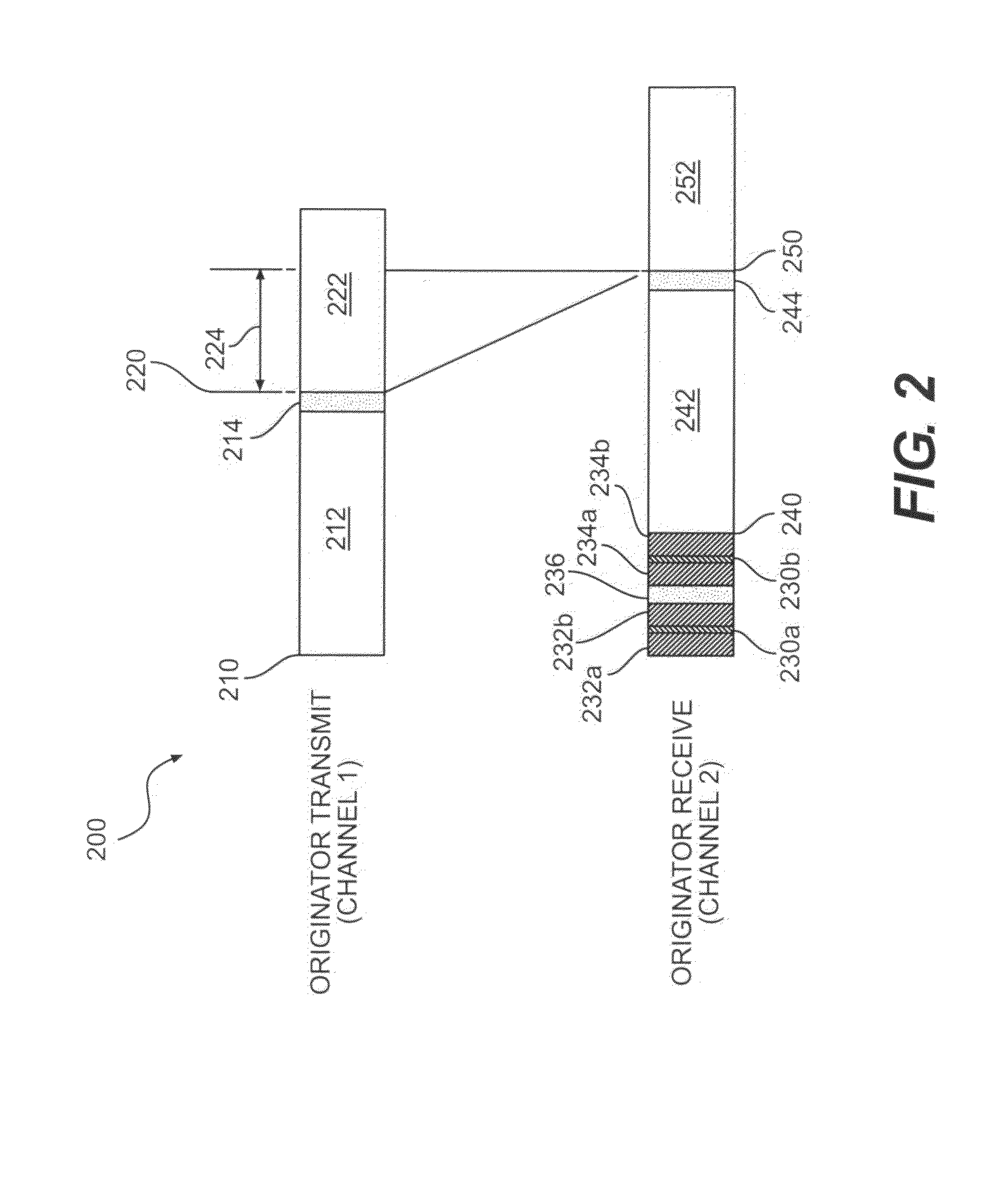

High-Precision Radio Frequency Ranging System

ActiveUS20120133558A1Radio wave direction/deviation determination systemsBeacon systemsImage resolutionSimulation

Methods for estimating a distance between an originator and a transponder, methods for calculating a fine time adjustment in a radio, computer-readable storage media containing instructions to configure a processor to perform such methods, originators used in a system for estimating a distance to a transponder, and transponders used in a system for estimating a distance to an originator. The methods utilize fine time adjustments to achieve sub-clock cycle time resolution. The methods may utilize offset master clocks. The methods may utilize a round-trip full-duplex configuration or a round-trip half-duplex configuration. The method produces accurate estimates of the distance between two radios.

Owner:ENSCO INC

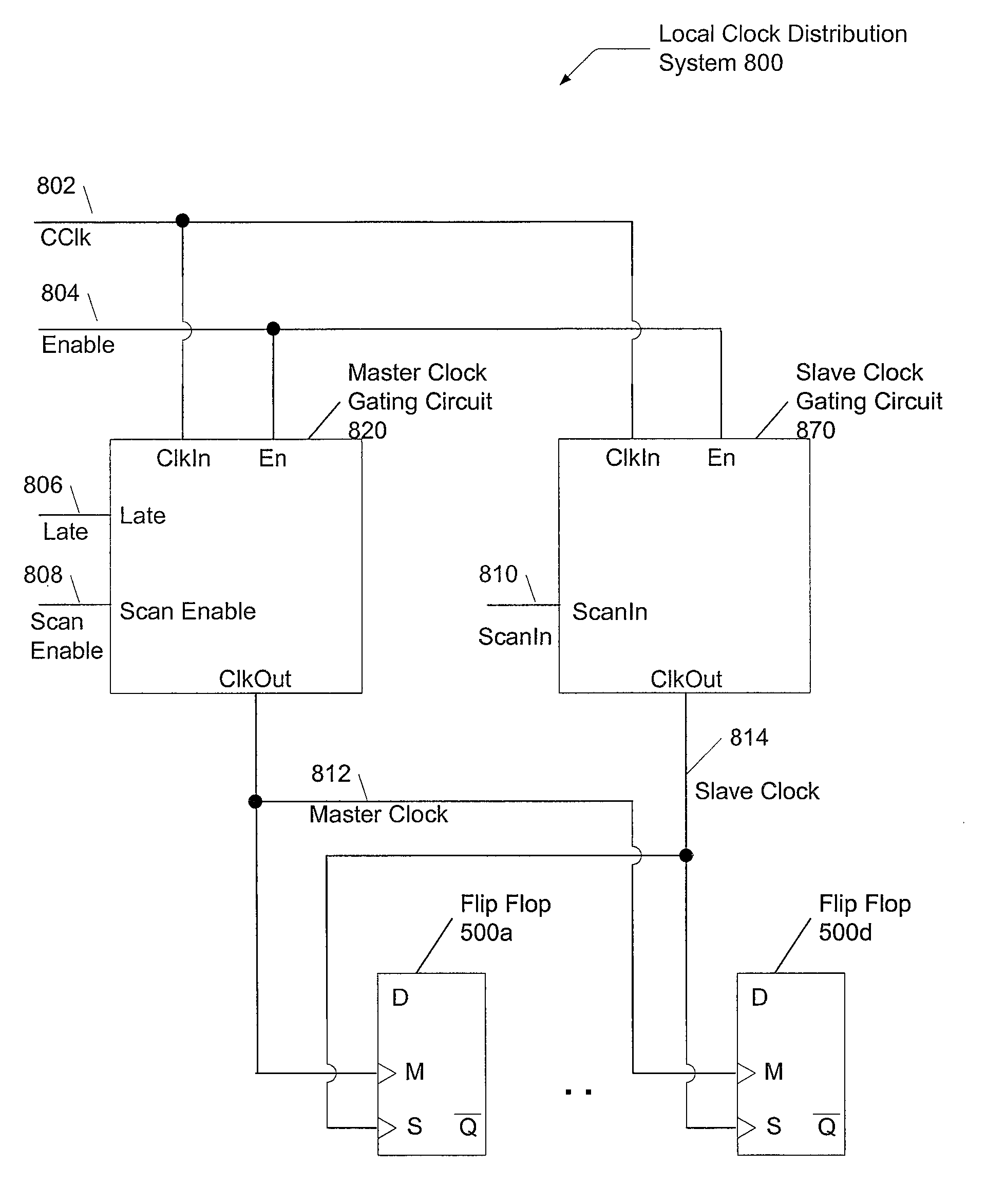

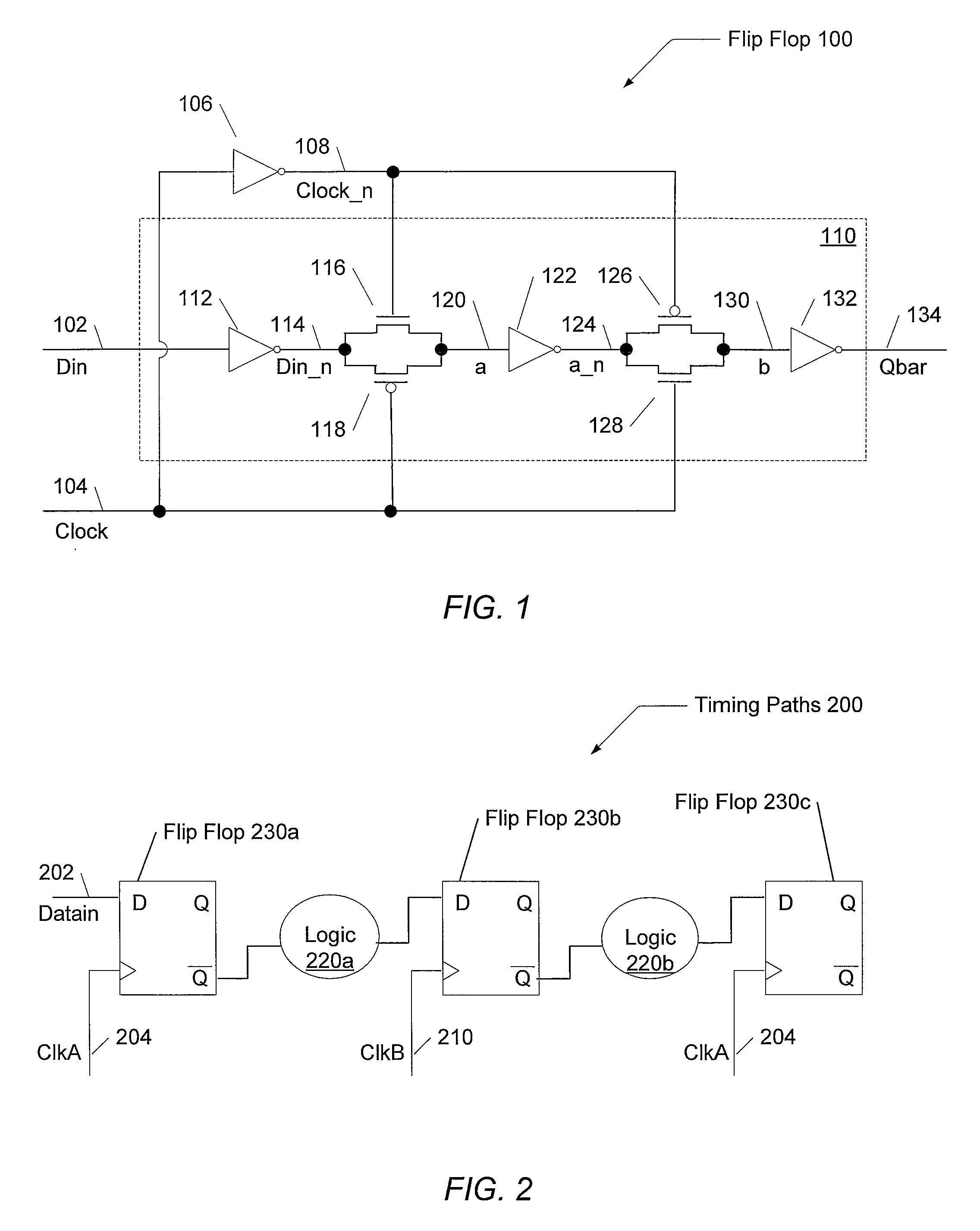

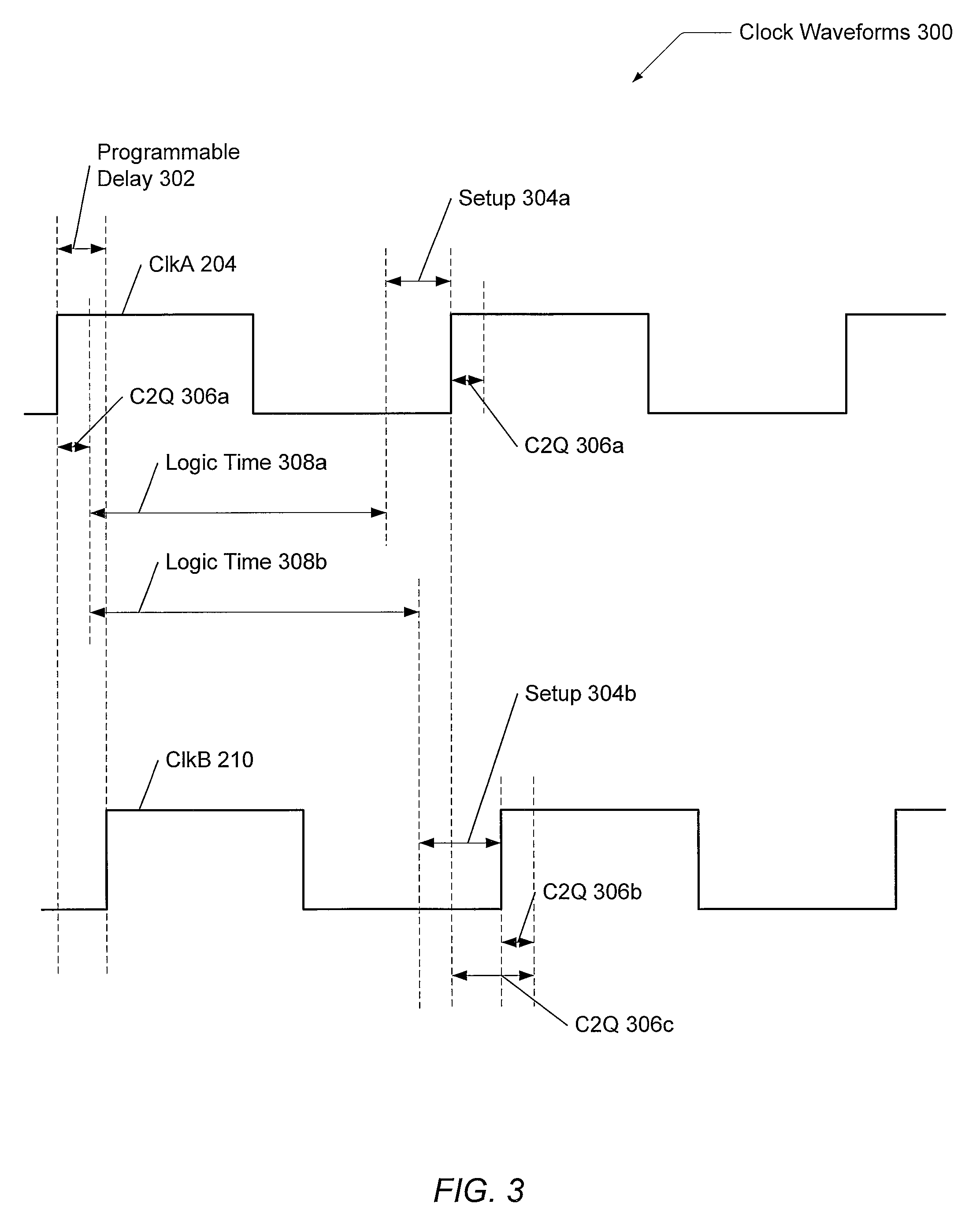

Programmable sample clock for empirical setup time selection

ActiveUS7772889B2Many timesElectric pulse generatorLogic circuits using elementary logic circuit componentsControl signalSlave clock

Owner:MEDIATEK INC

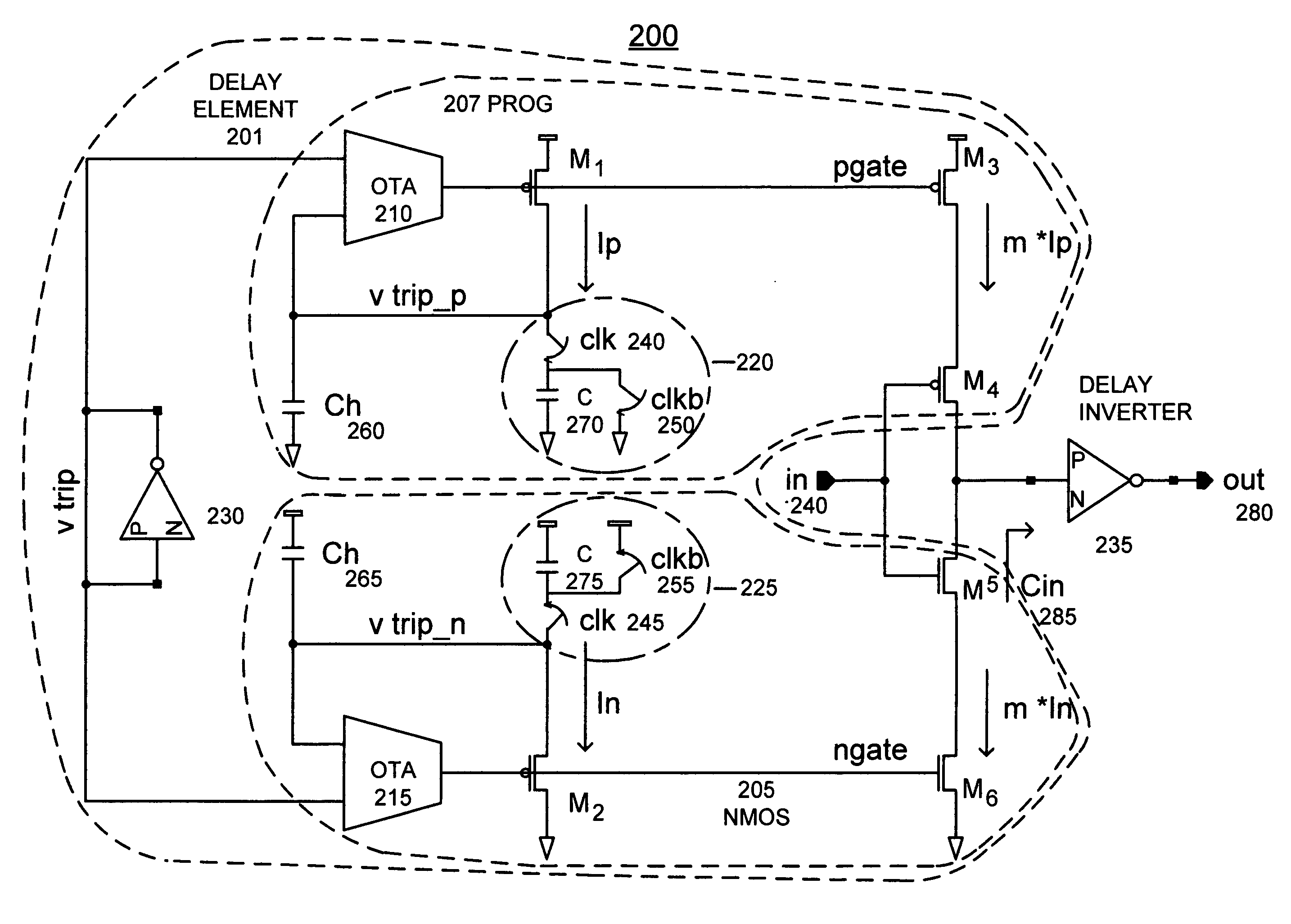

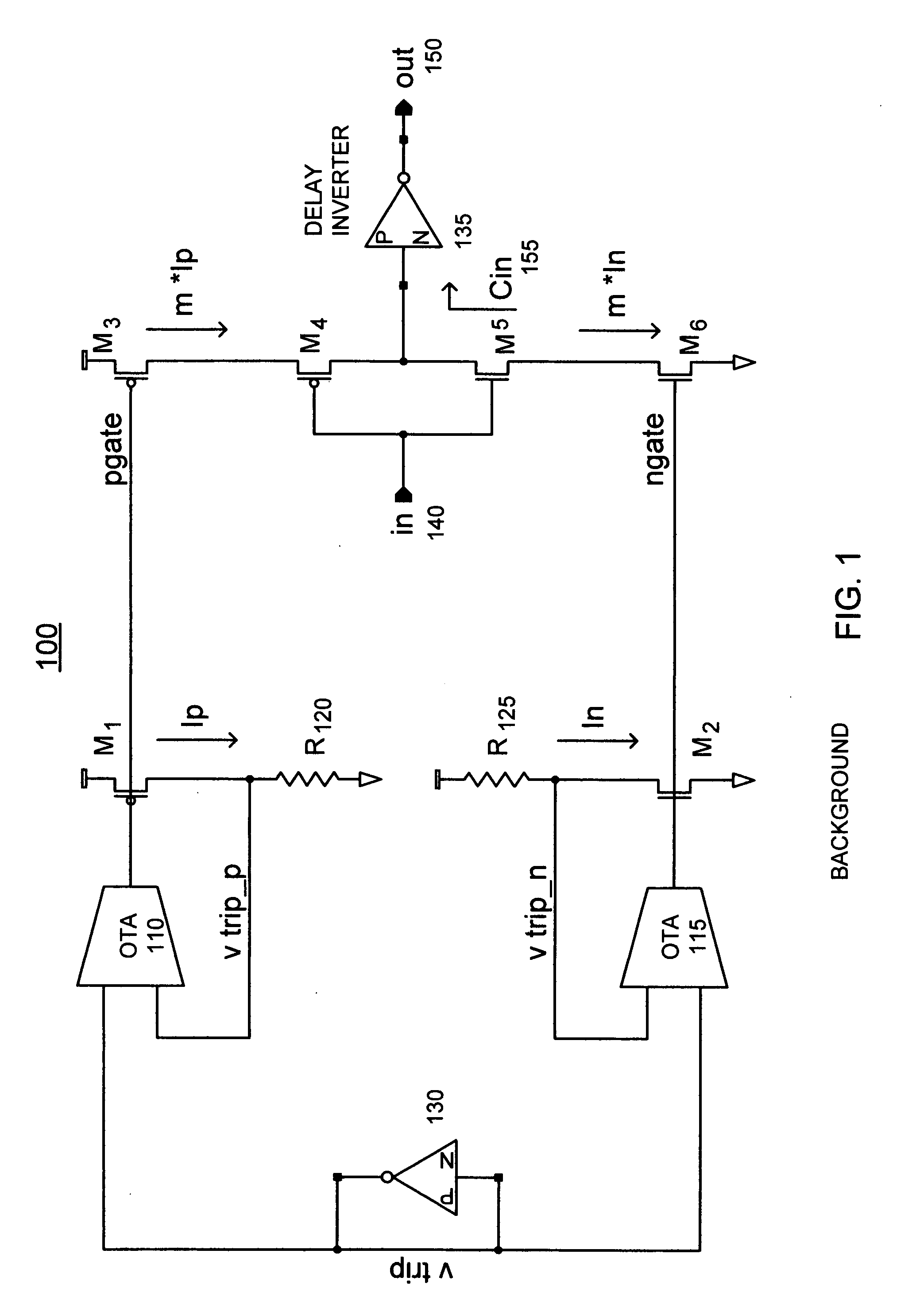

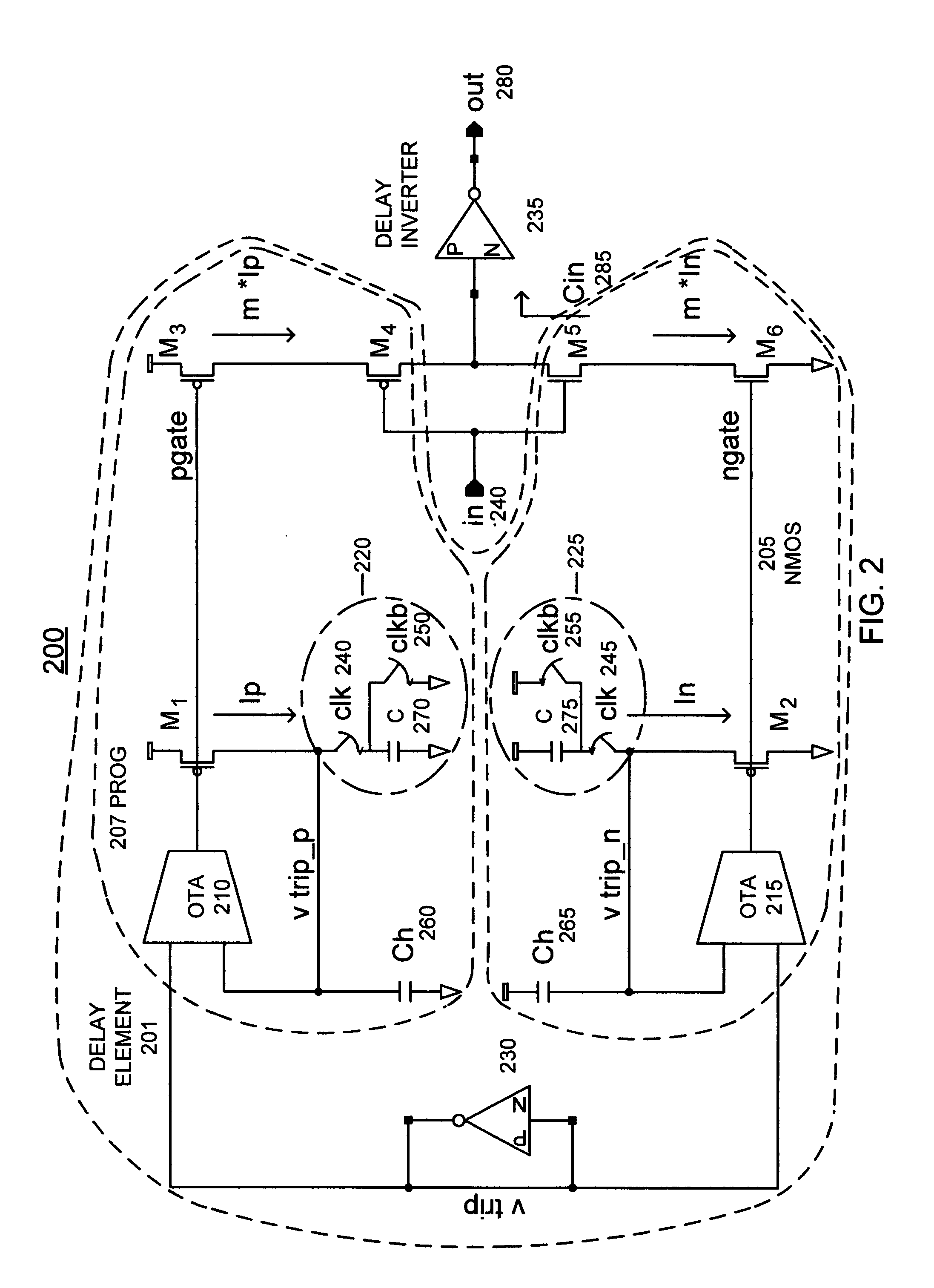

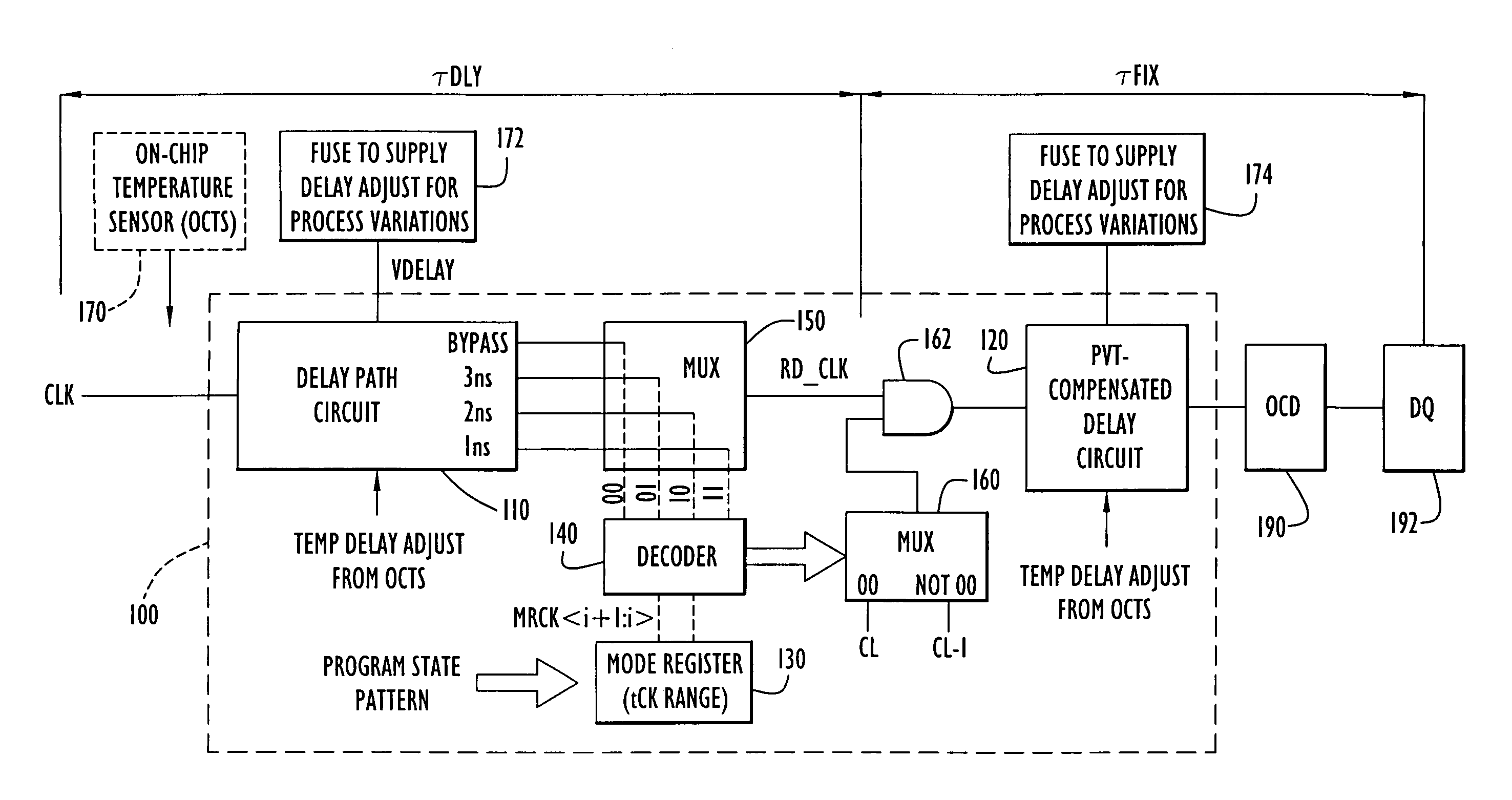

Delay circuit that scales with clock cycle time

A circuit having a process, voltage, and temperature (PVT) invariant delay element is disclosed. In one embodiment, the present invention includes a first and second operational transconductance amplifier (OTA), a first and second switched capacitor driven by a clock, and a first and second clock-controlled switch. In addition, the present invention includes a trip inverter, a delay inverter, and a plurality of transistors. In so coupling the first and second OTA, the first and second switched capacitor, the first and second clock-controlled switch, the trip inverter, the delay inverter, and the plurality of transistors, a circuit having a PVT invariant delay element is provided.

Owner:MONTEREY RES LLC

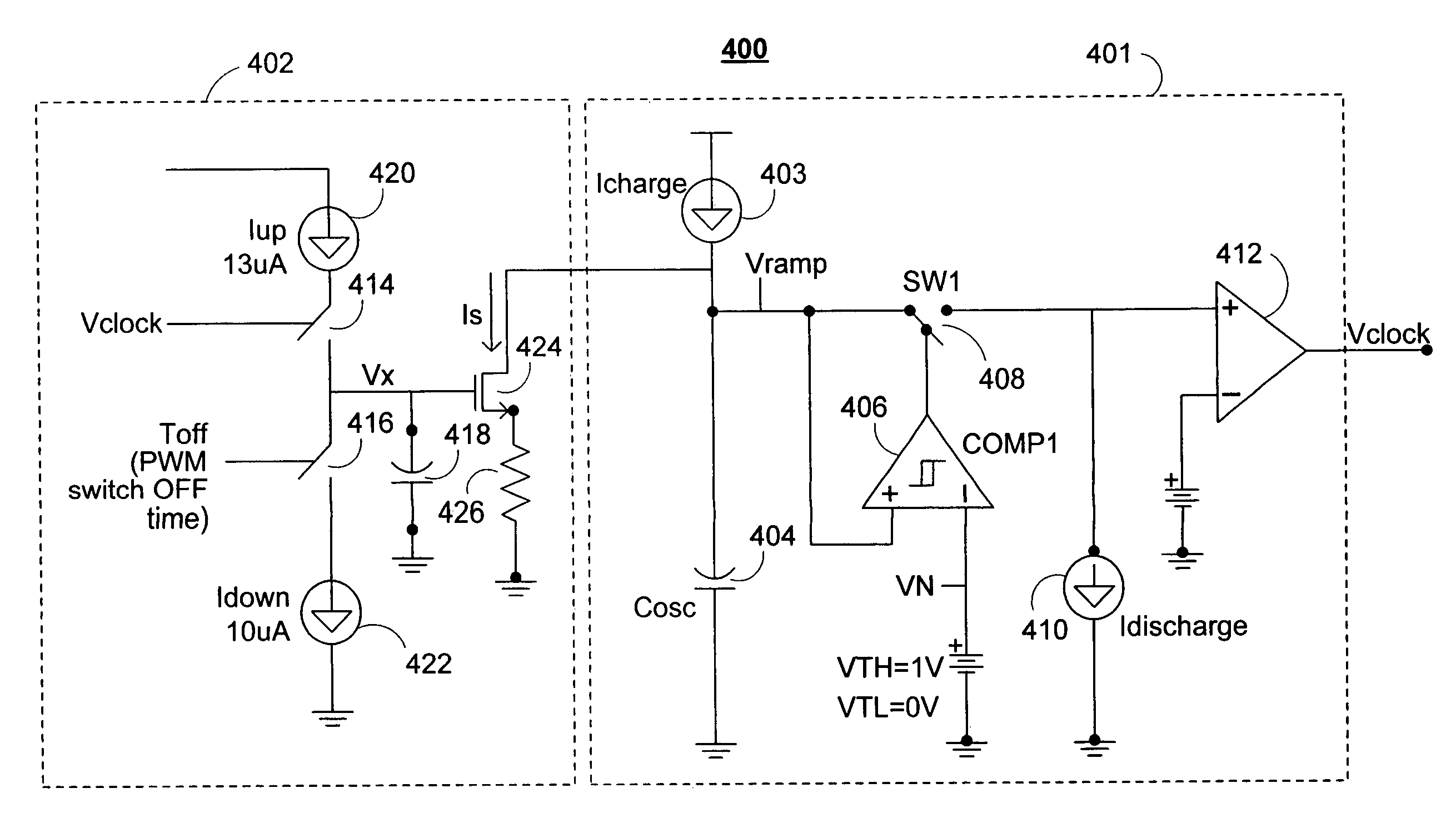

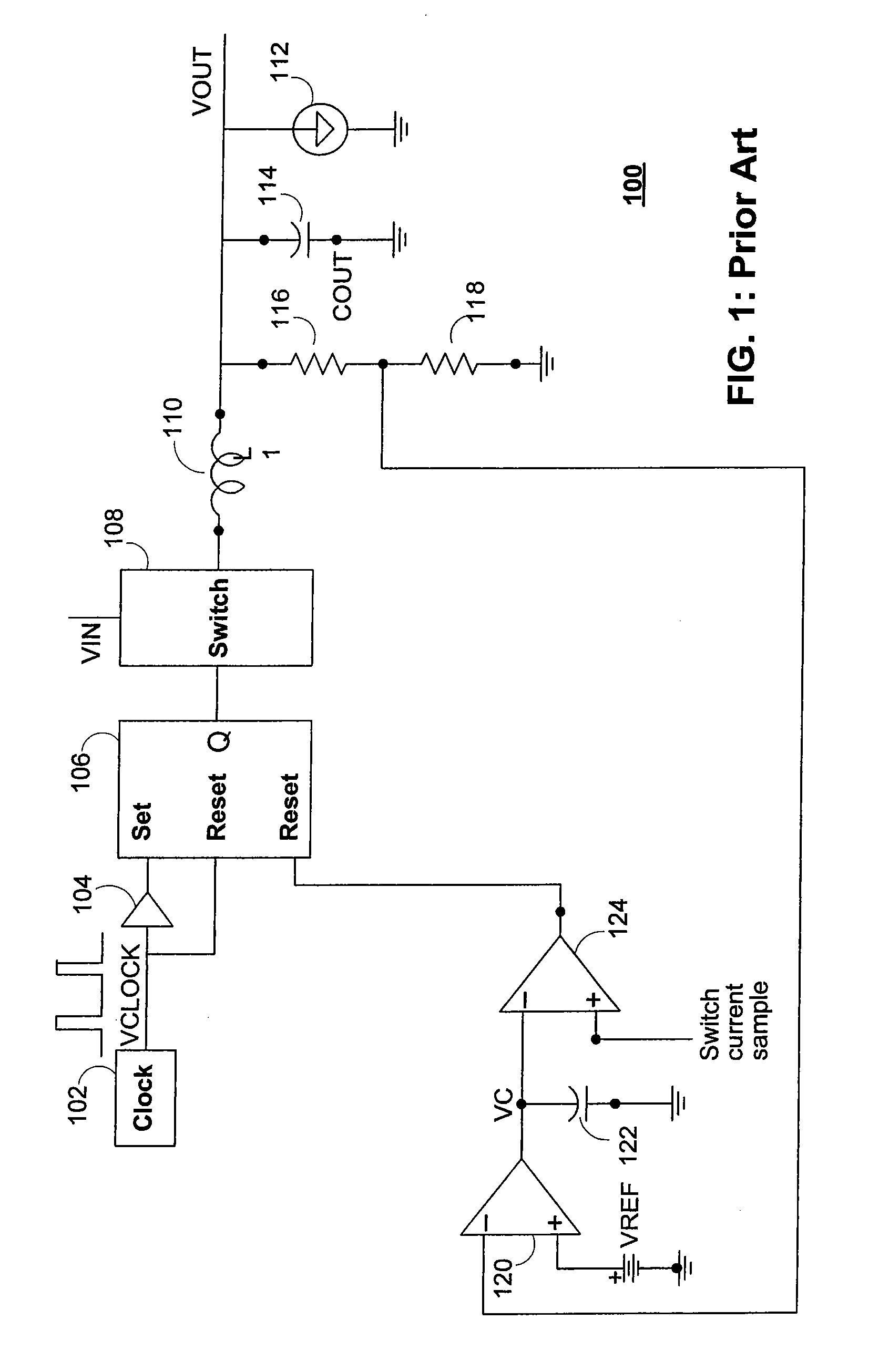

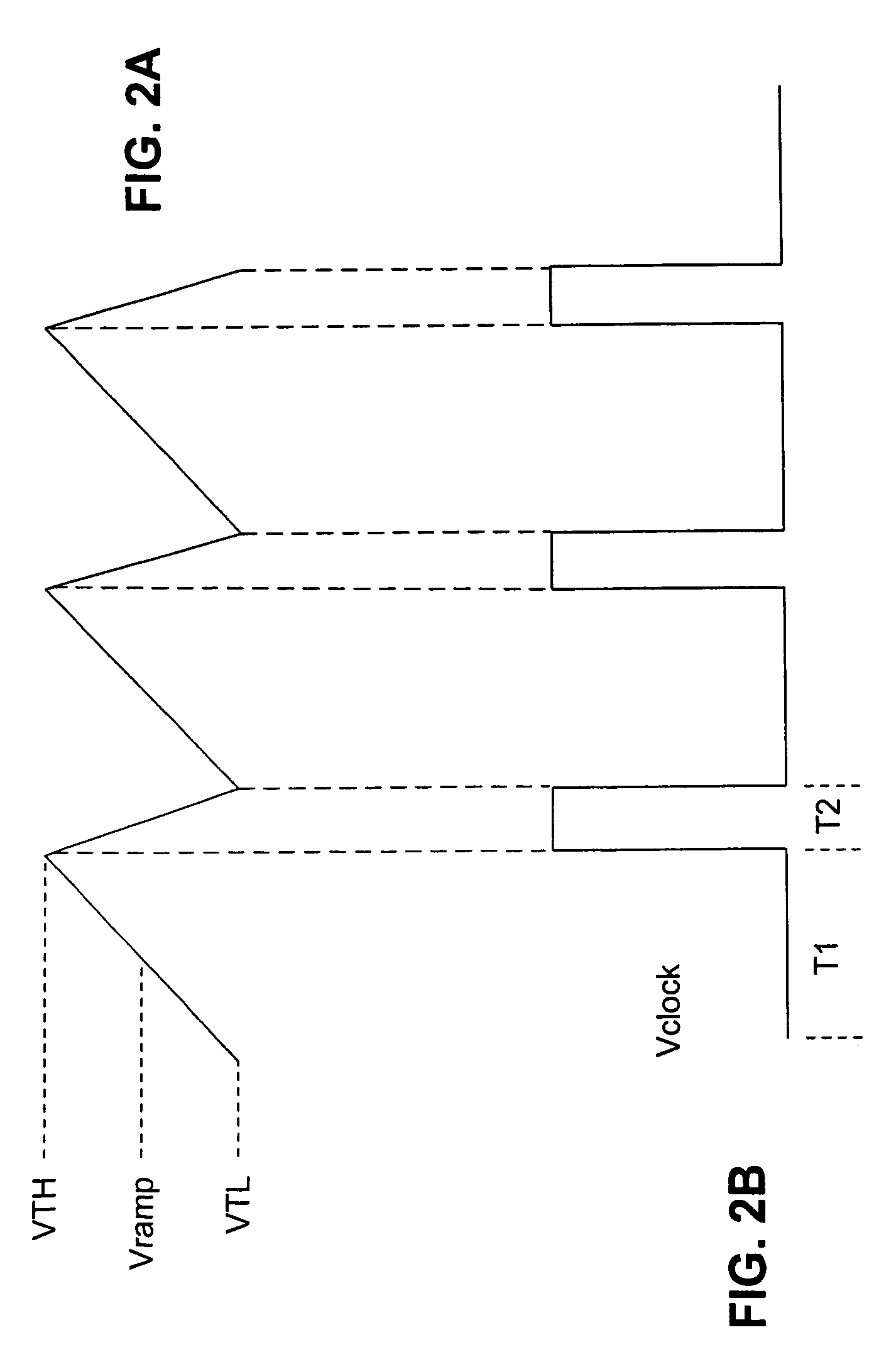

Switching regulator duty cycle control in a fixed frequency operation

ActiveUS7388444B2Increase duty cyclePulse generation by bipolar transistorsDc-dc conversionCharge currentAnalog feedback

A clock oscillator system for use in providing the switching regulator duty cycle control in a fixed frequency (no cycle skipping) operation is provided. In one embodiment, the circuit according to the invention uses an analog feedback loop to extend the switch ON time of the clock cycle by controlling the oscillator charging current and, thereby, increase the duty cycle. Preferably, this circuit can achieve very high switching duty cycle and / or very low switching duty cycle in a PWM switching regulator operated in very low drop-out operation when very high duty cycle is required or in other conditions when very low duty cycle is required.

Owner:ANALOG DEVICES INT UNLTD

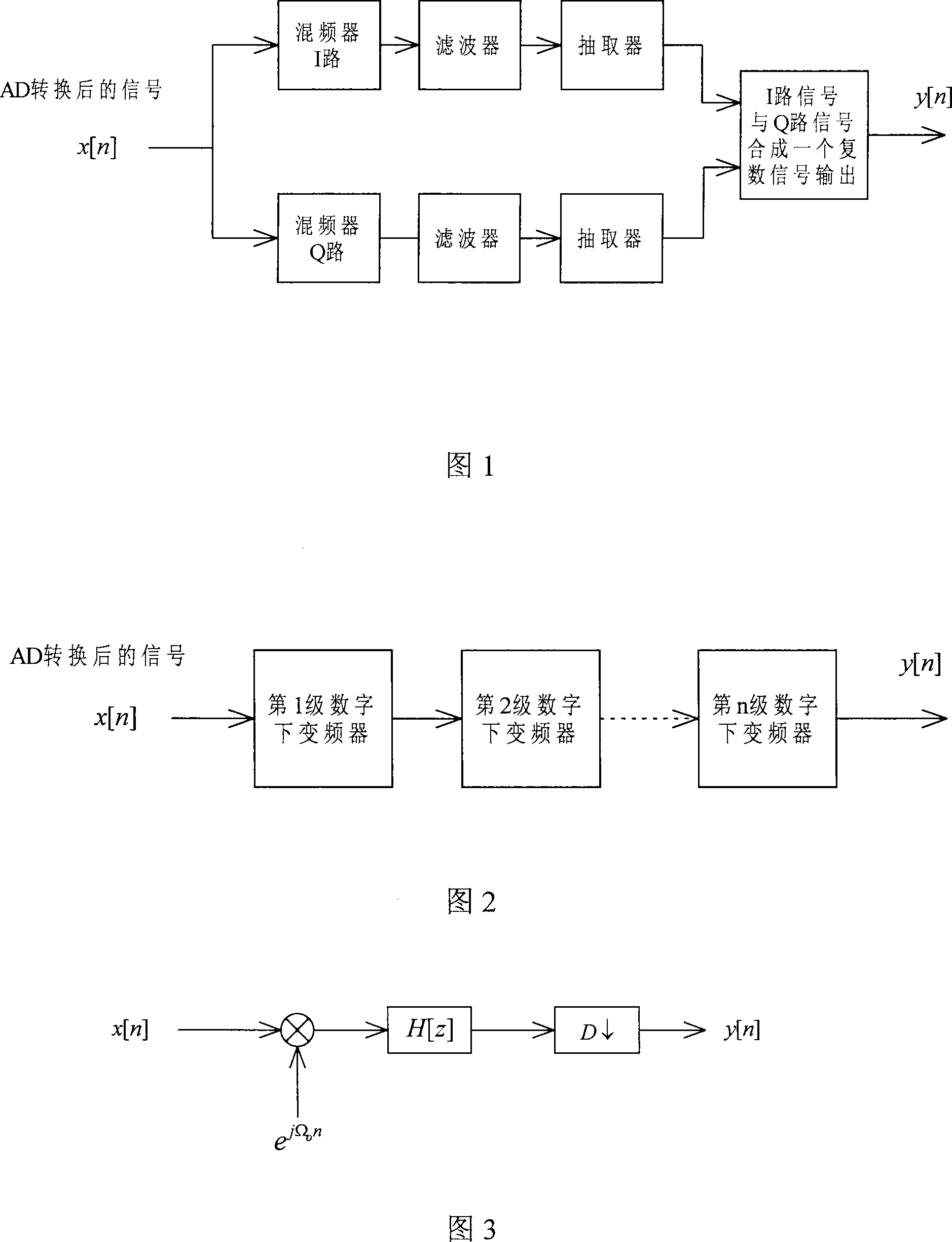

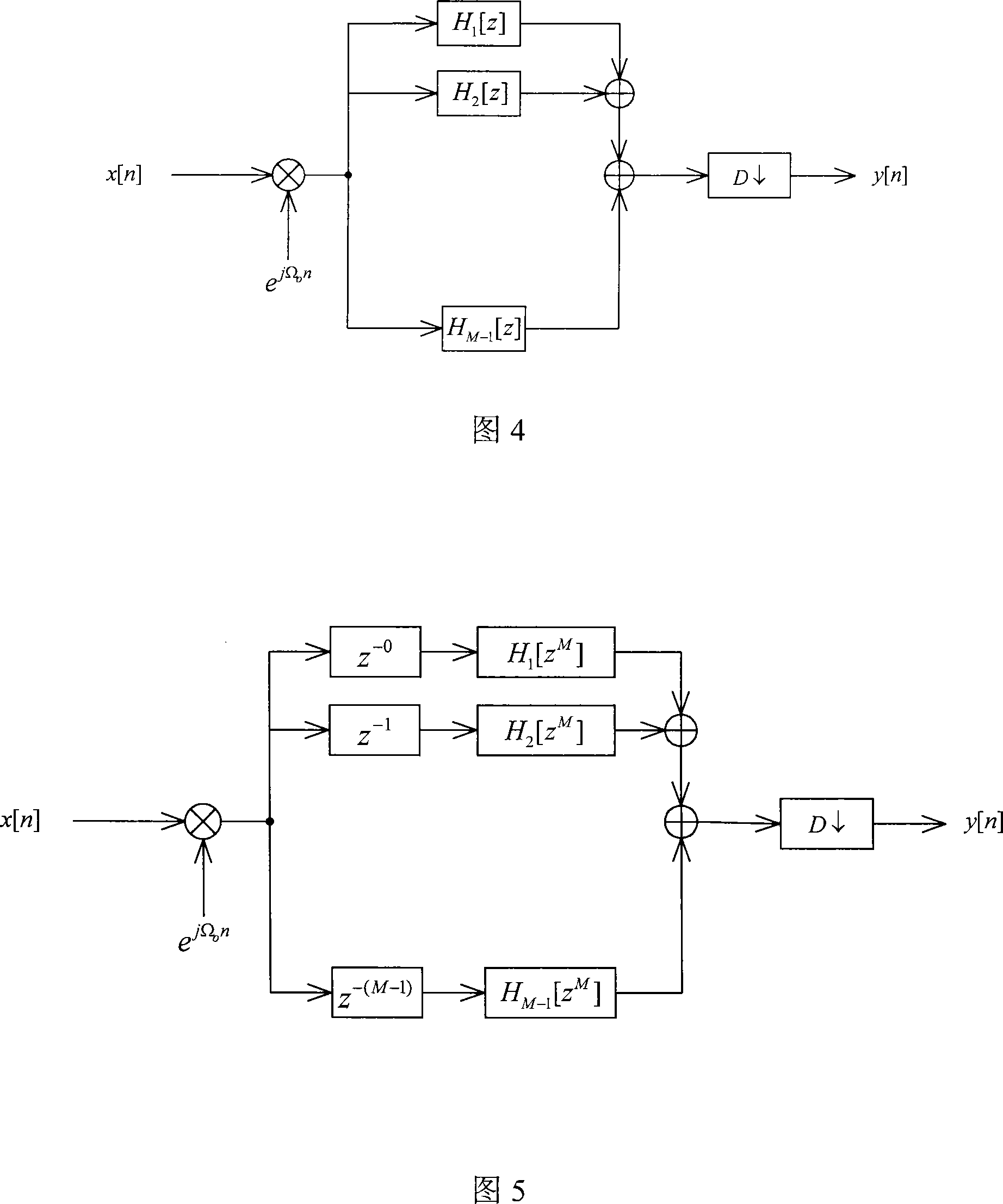

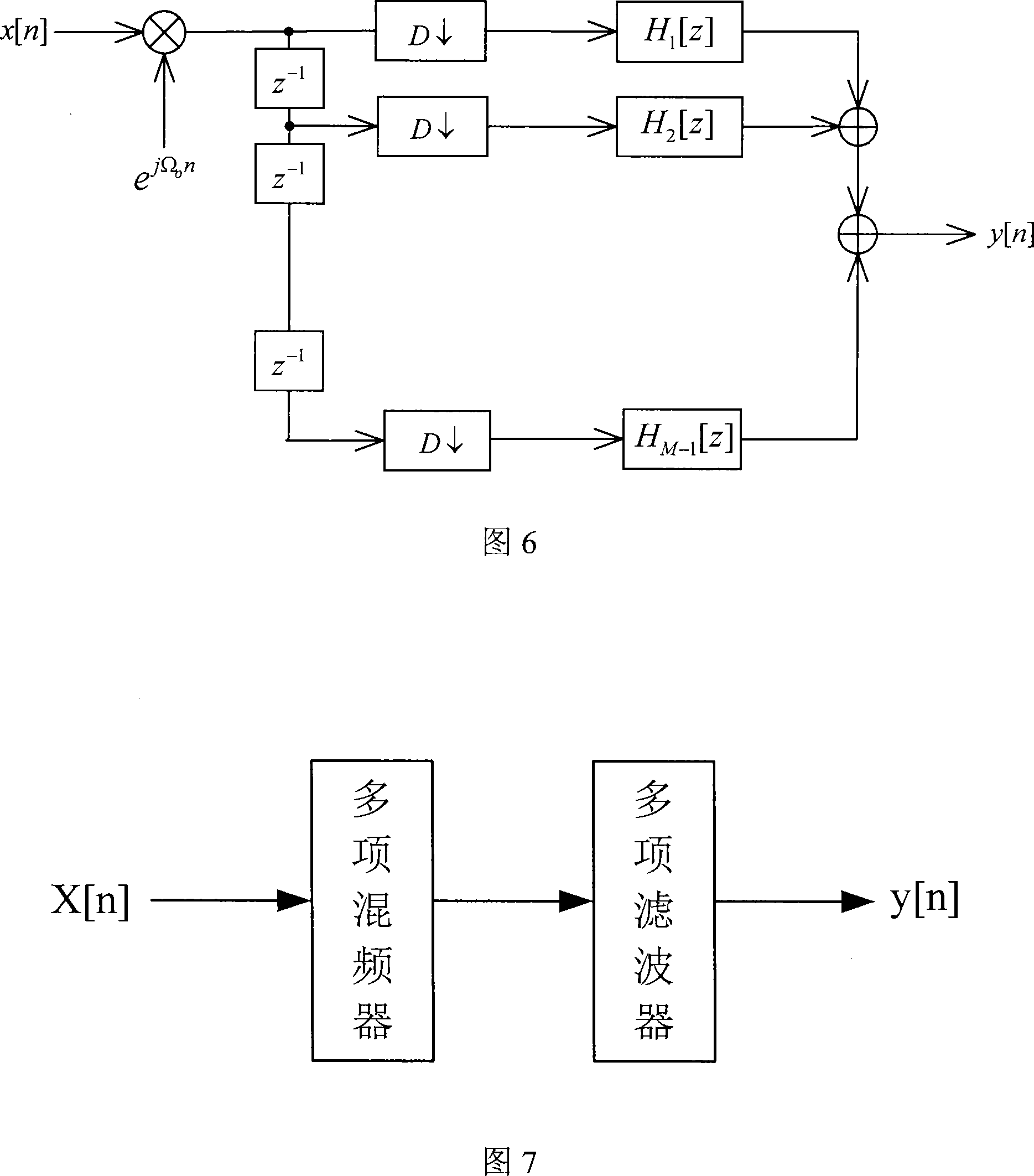

Digital low-converter

InactiveCN101197801AReduce processing difficultyPhase-modulated carrier systemsFrequency changerDigital down converter

The invention discloses a digital down converter which comprises a signal input end which is used for receiving input signals and a signal output end which is used for outputting signals, wherein, N independent operation branches are arranged between the signal input end and the signal output end; each operation branch comprises an extractor the extraction factor of which is N, a multiphase branch mixer which is constructed according to an N-phase digital mixer, and a multiphase branch filter which is constructed according to an H(z) expression of an N-phase digital filter which are connected with each other in order; input ends of extractors of various operation branches are coupled with the signal input end; outputs of branch filters of various operation branches are outputted to the signal output end through addition by an adder; an i operation branch corresponding to the input signals comprises i-1 clock cycle time delays; N and i are all natural numbers, and i is more than or equal to 1 and less than or equal to N. Arithmetic speed of each operation branch is lowered to be 1 / N of the prior arithmetic speed, and modules for improving the arithmetic speed do not exist because each operation branch is completely independent, thereby processing difficulty of a system is reduced.

Owner:ARTEK MICROELECTRONICS

High-precision radio frequency ranging system

Methods for estimating a distance between an originator and a transponder, methods for calculating a fine time adjustment in a radio, computer-readable storage media containing instructions to configure a processor to perform such methods, originators used in a system for estimating a distance to a transponder, and transponders used in a system for estimating a distance to an originator. The methods utilize fine time adjustments to achieve sub-clock cycle time resolution. The methods may utilize offset master clocks. The methods may utilize a round-trip full-duplex configuration or a round-trip full-duplex configuration. The method produces accurate estimates of the distance between two radios.

Owner:ENSCO INC

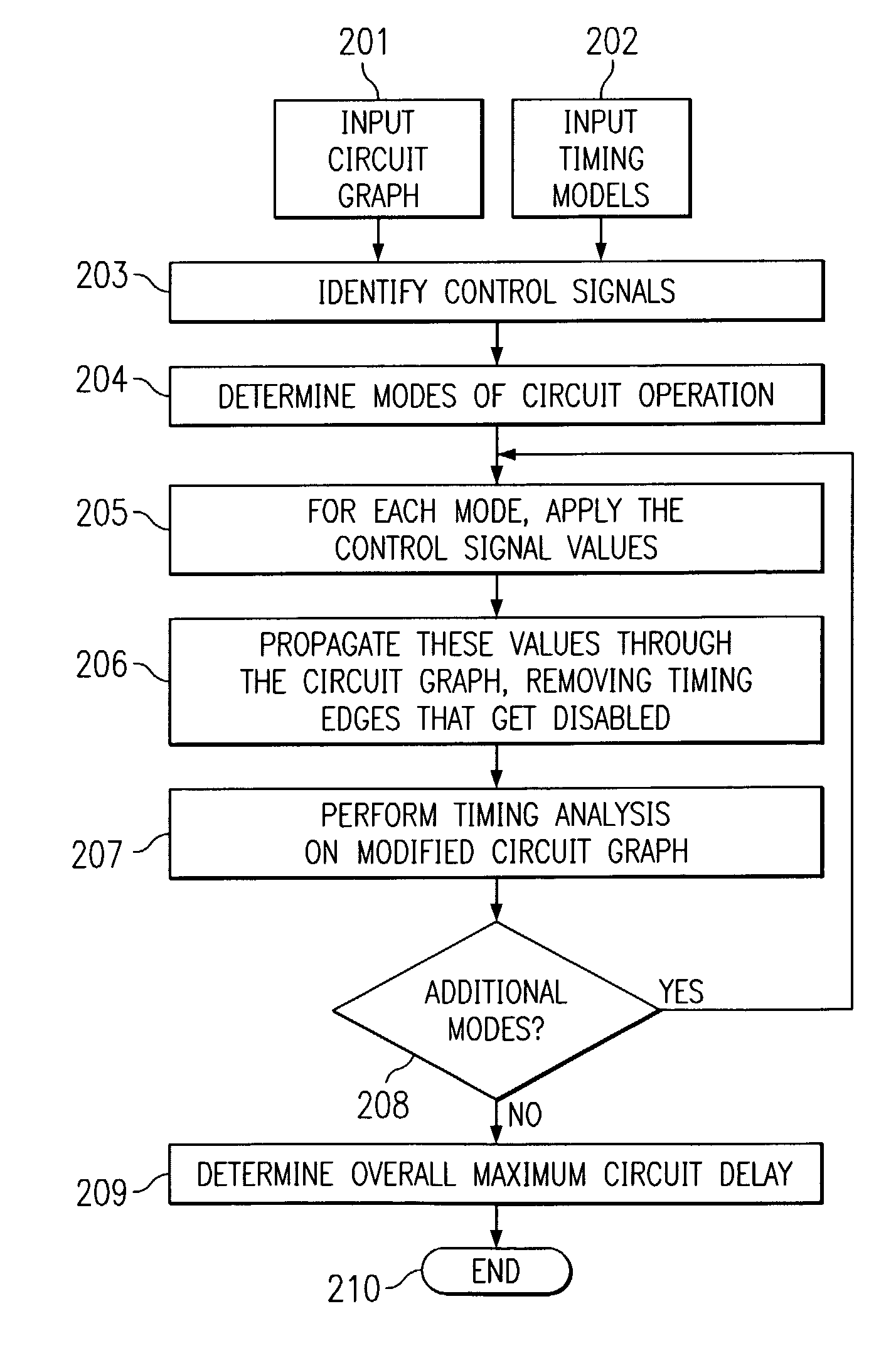

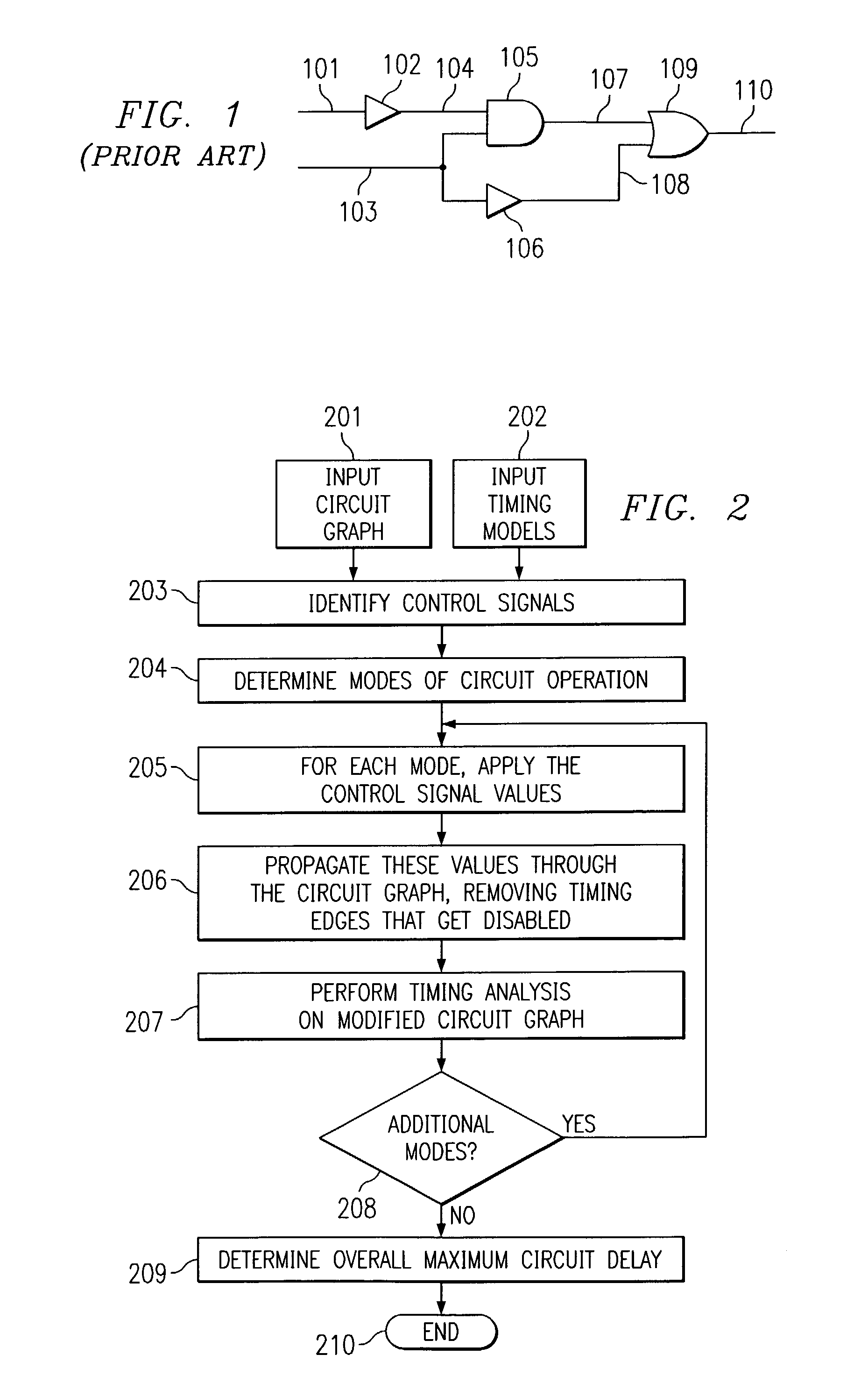

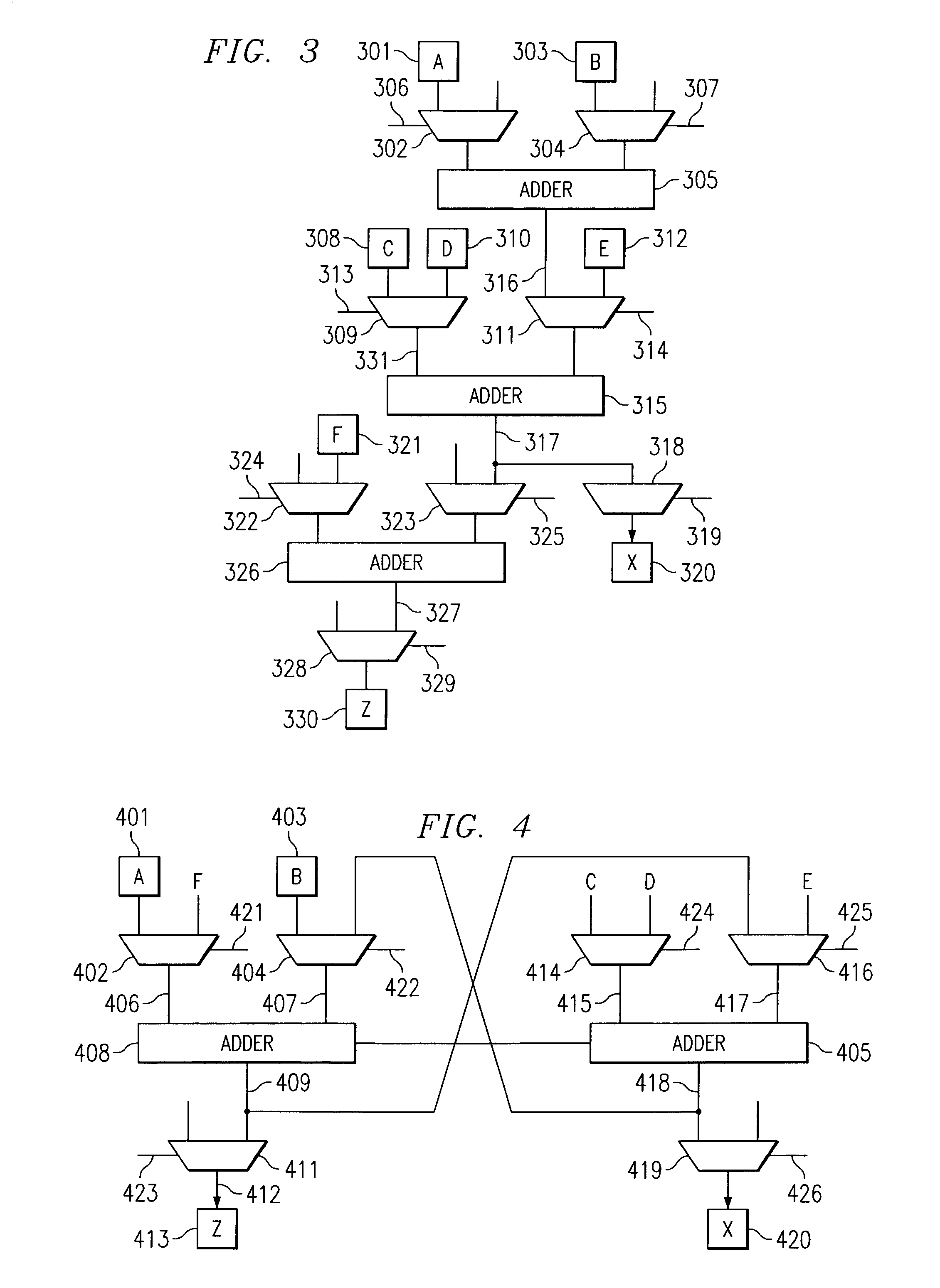

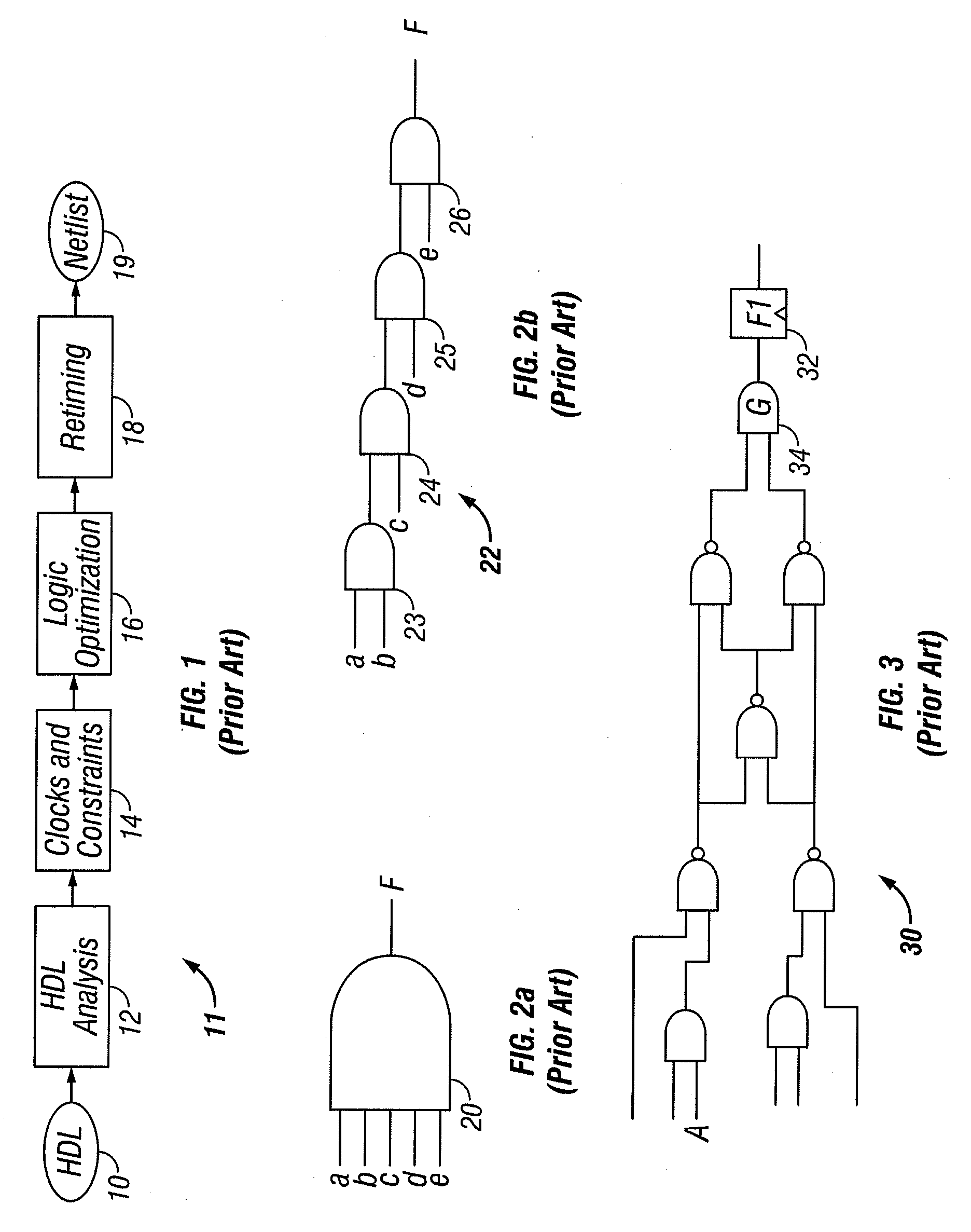

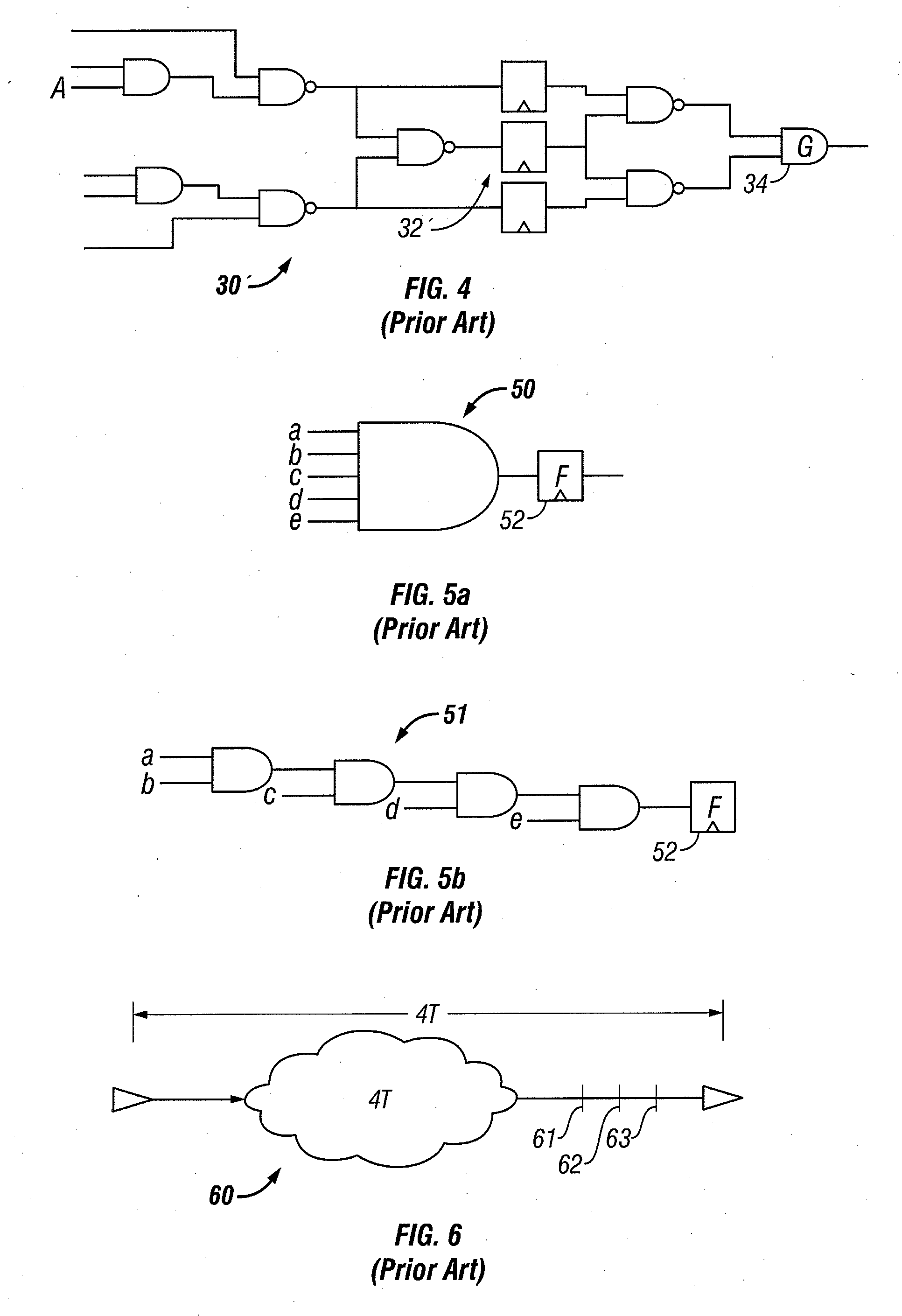

System for and method of clock cycle-time analysis using mode-slicing mechanism

A method for performing a global timing analysis of a proposed digital circuit comprising receiving timing models and the proposed digital circuit; determining at least one mode of circuit operation of the proposed digital circuit; deriving a sub-circuit corresponding to each of at least one mode of circuit operation; performing timing analysis on each of the sub-circuits derived corresponding to each of the modes; and combining the timing analysis results for all of the modes to determine an overall maximum circuit delay.

Owner:SAMSUNG ELECTRONICS CO LTD

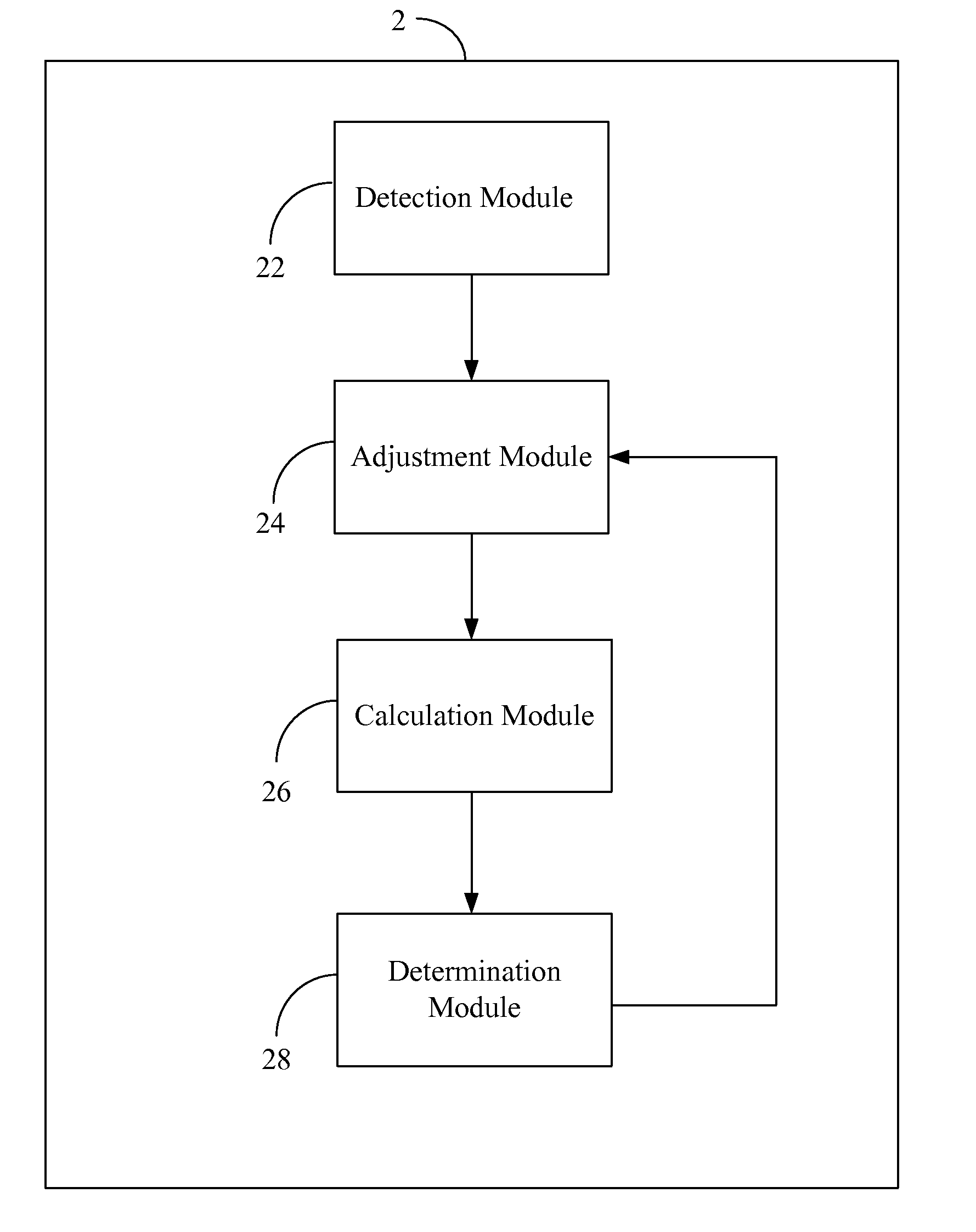

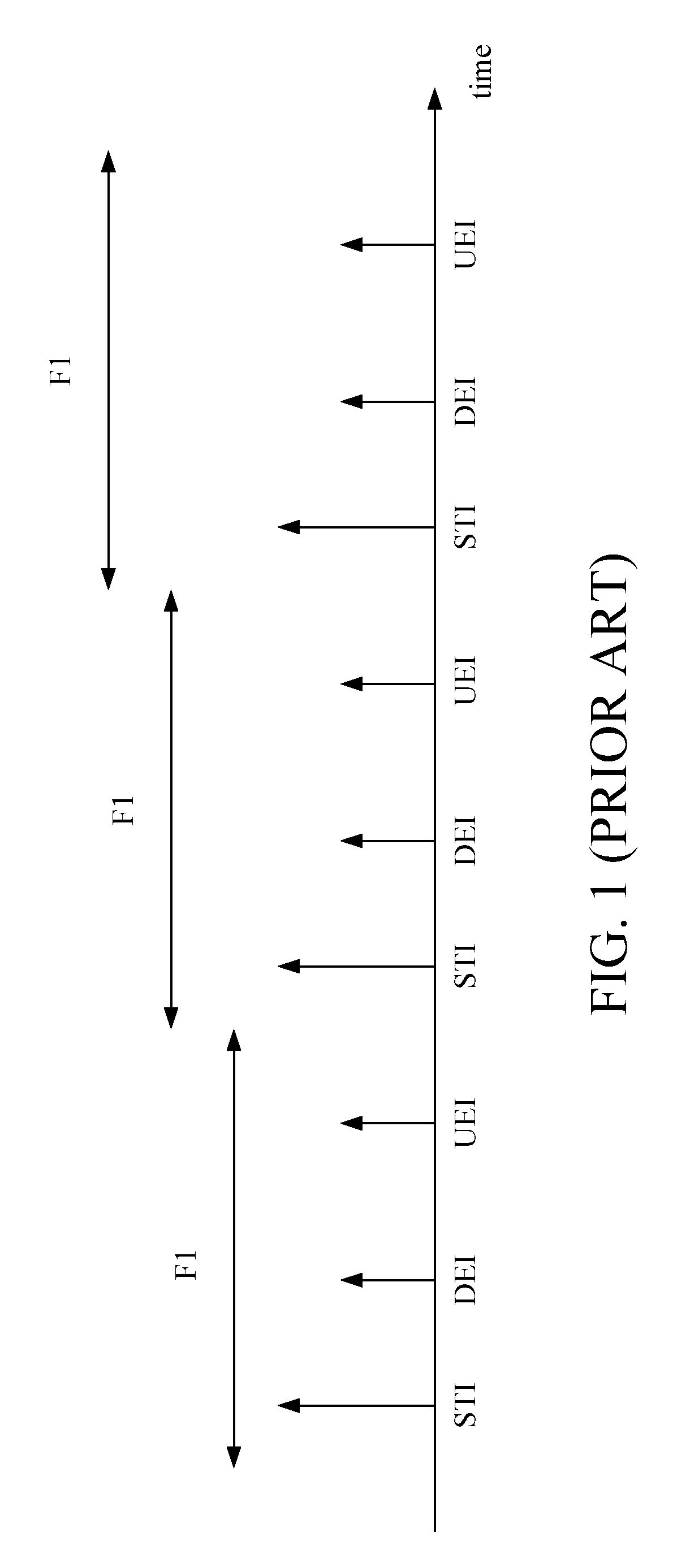

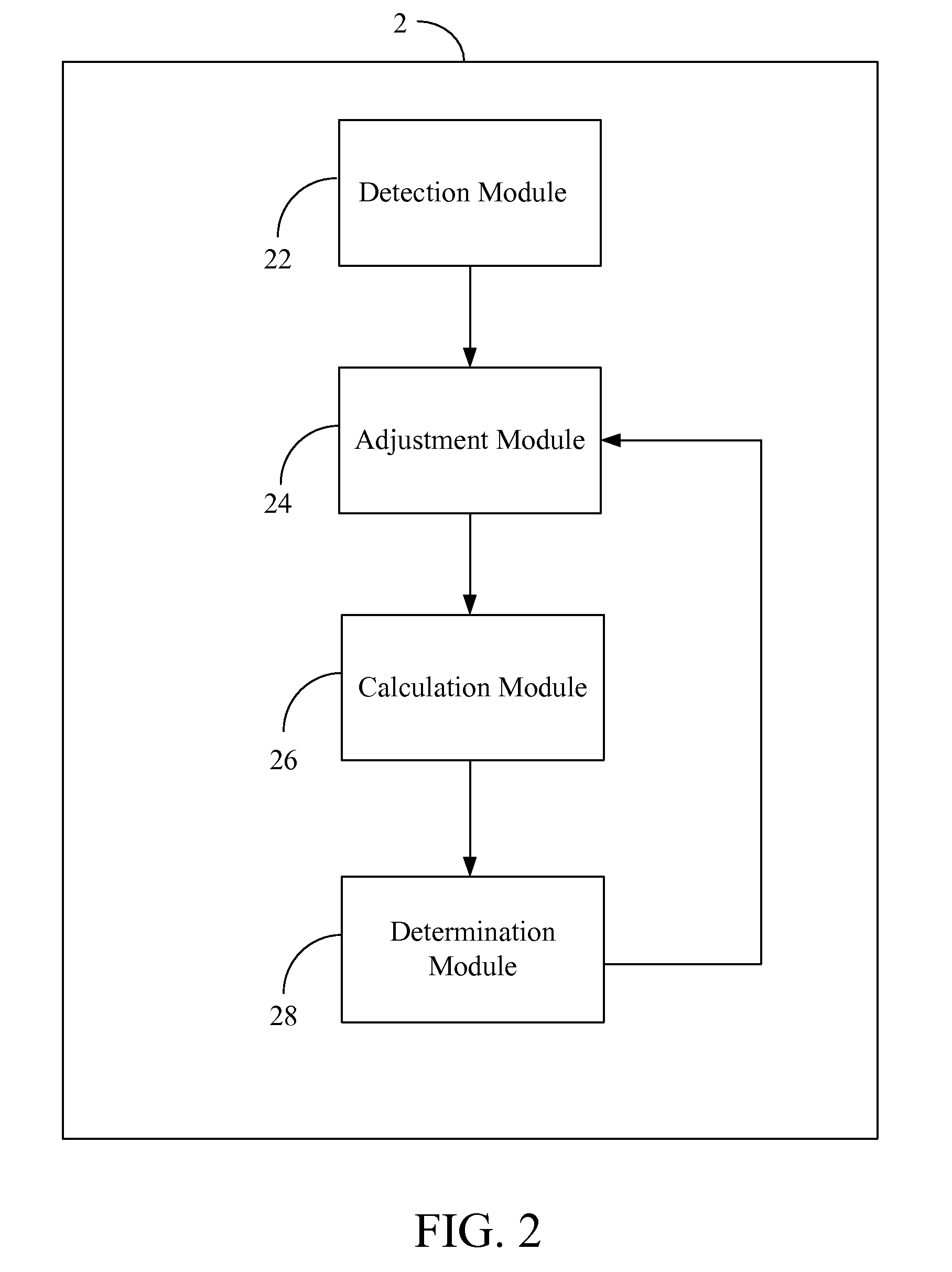

Method and Apparatus for Adjusting a System Timer of a Mobile Station

InactiveUS20100042866A1Improve performanceReduce in quantityGenerating/distributing signalsData conversionMobile stationTimer

A method and an apparatus for adjusting a system timer of a mobile station (MS) are disclosed, wherein a clock cycle time of the system timer is of a predetermined length. The method comprises the following steps: detecting a frame boundary of a frame from a base station (BS), the frame is with a frame length; adjusting an interrupt signal of the system timer from a predetermined time to a time related to the frame; and adjusting the clock cycle time from the predetermined length to the frame length. The modified system timer of the MS is synchronized to a frame timing of the BS.

Owner:MEDIATEK INC

Method for generating optimized constraint systems for retimable digital designs

ActiveUS20090083685A1Low costDesirable propertyComputer aided designSoftware simulation/interpretation/emulationLogic optimizationDigital electronics

Owner:CADENCE DESIGN SYST INC

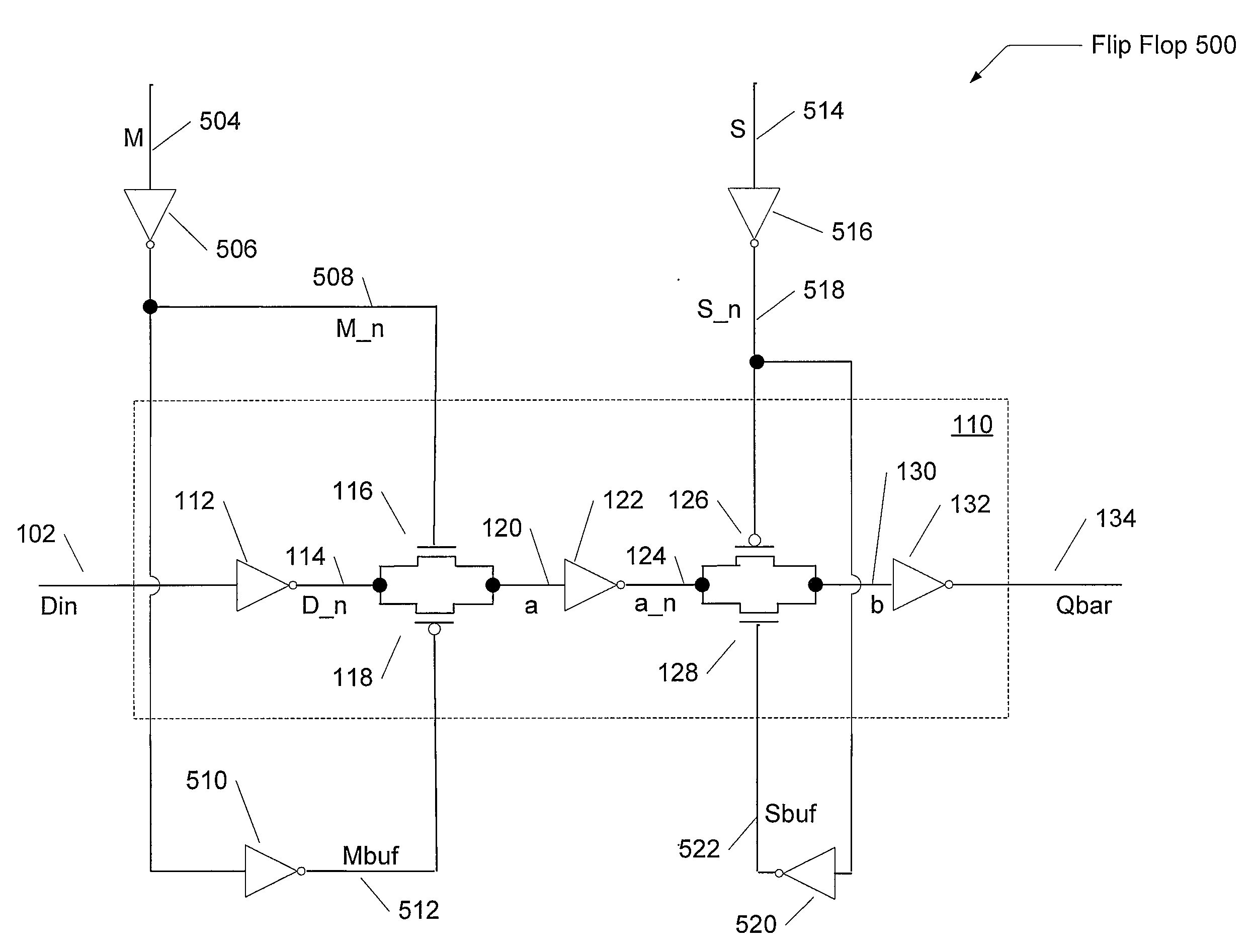

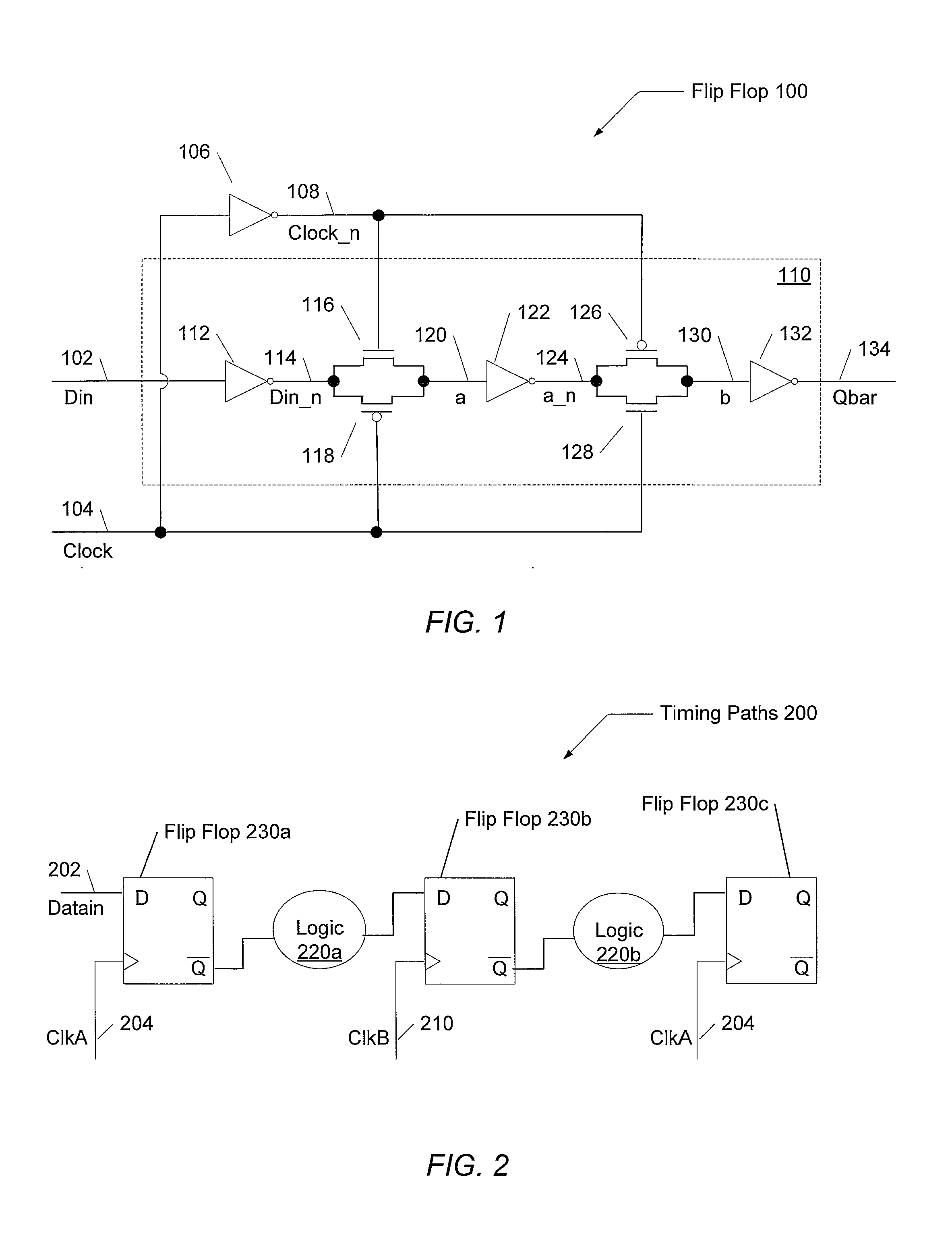

Programmable sample clock for empirical setup time selection

ActiveUS20090256593A1Electric pulse generatorLogic circuits using elementary logic circuit componentsControl signalSlave clock

A system and method for efficient improvement of timing analysis for faster processor designs with negligible impact on die-area. Rather than provide a single clock to flip-flop circuits on a semiconductor chip, split clocks are used. A flip-flop receives a master clock signal for a master latch and receives a separate slave clock signal for a slave latch. Master and slave clock gater circuits are coupled to a global clock distribution system and the local flip-flops. The master clock gater circuit receives a delay control signal used to select a delay, wherein the selected delay determines an additional amount of time the master clock signal transitions after the slave clock signal transitions. The use of the delayed master clock on the semiconductor chip may allow a timing path to have more computation time without increasing the clock cycle time. Further, the delay may be chosen to fix timing paths in post-silicon.

Owner:MEDIATEK INC

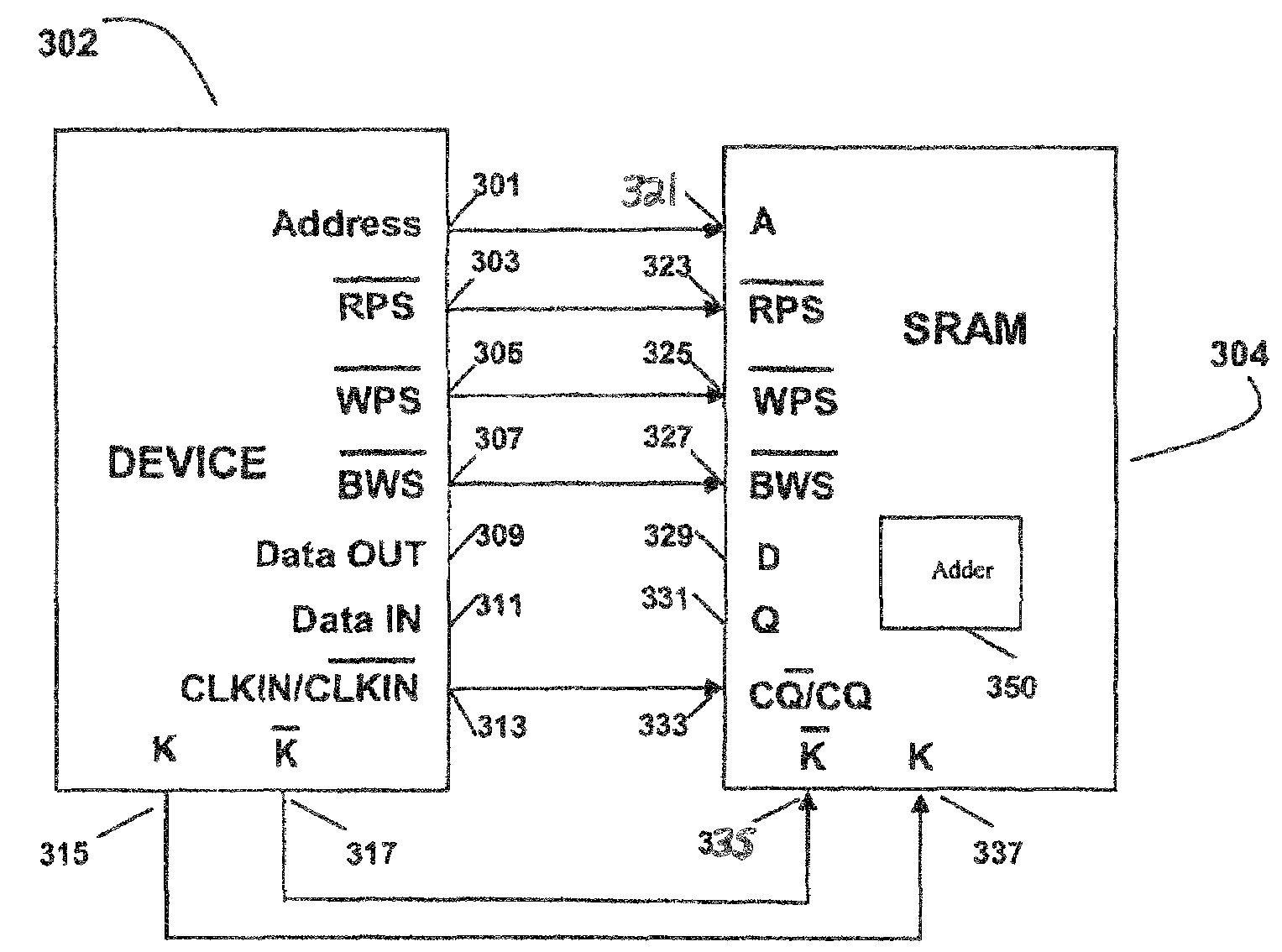

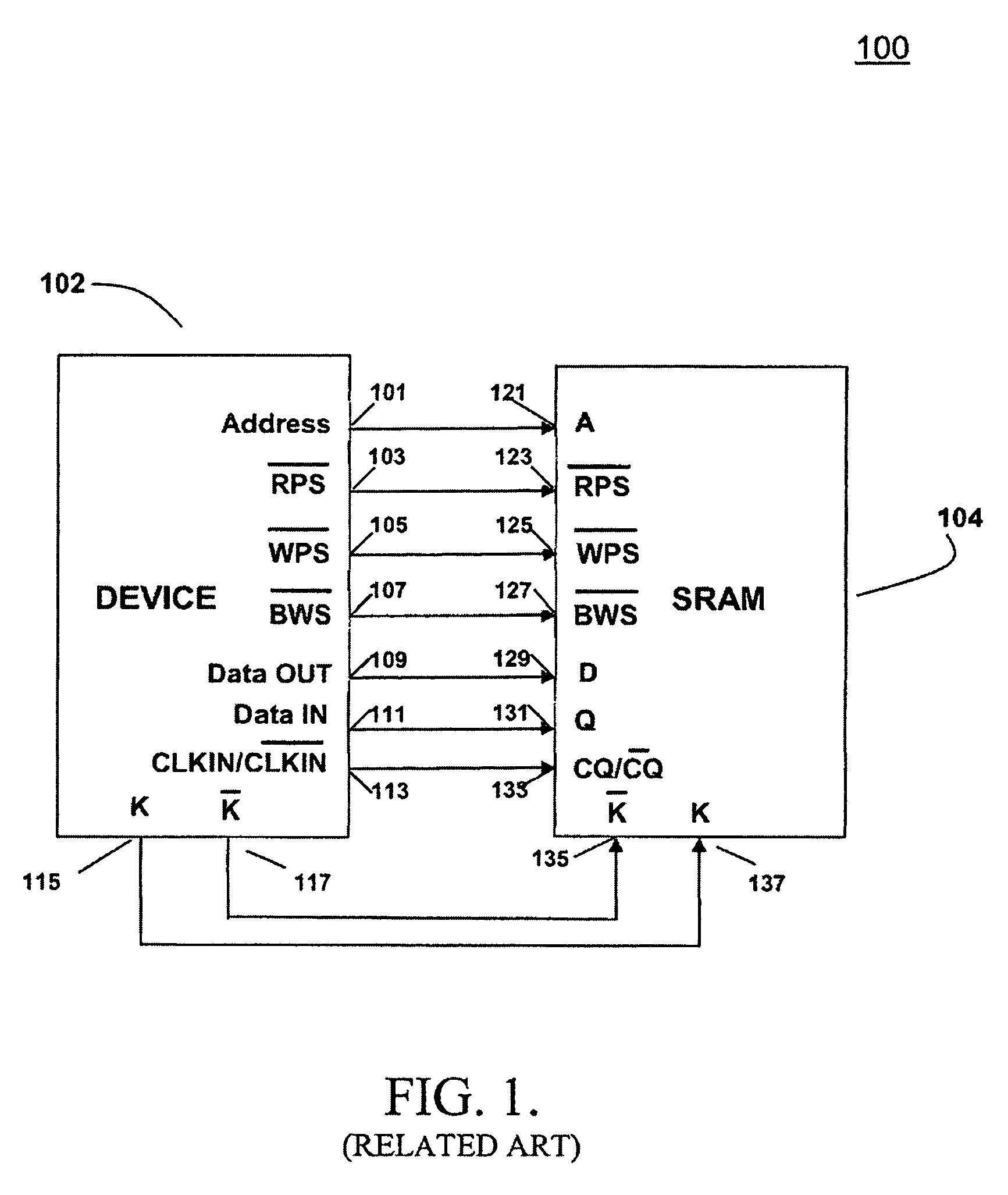

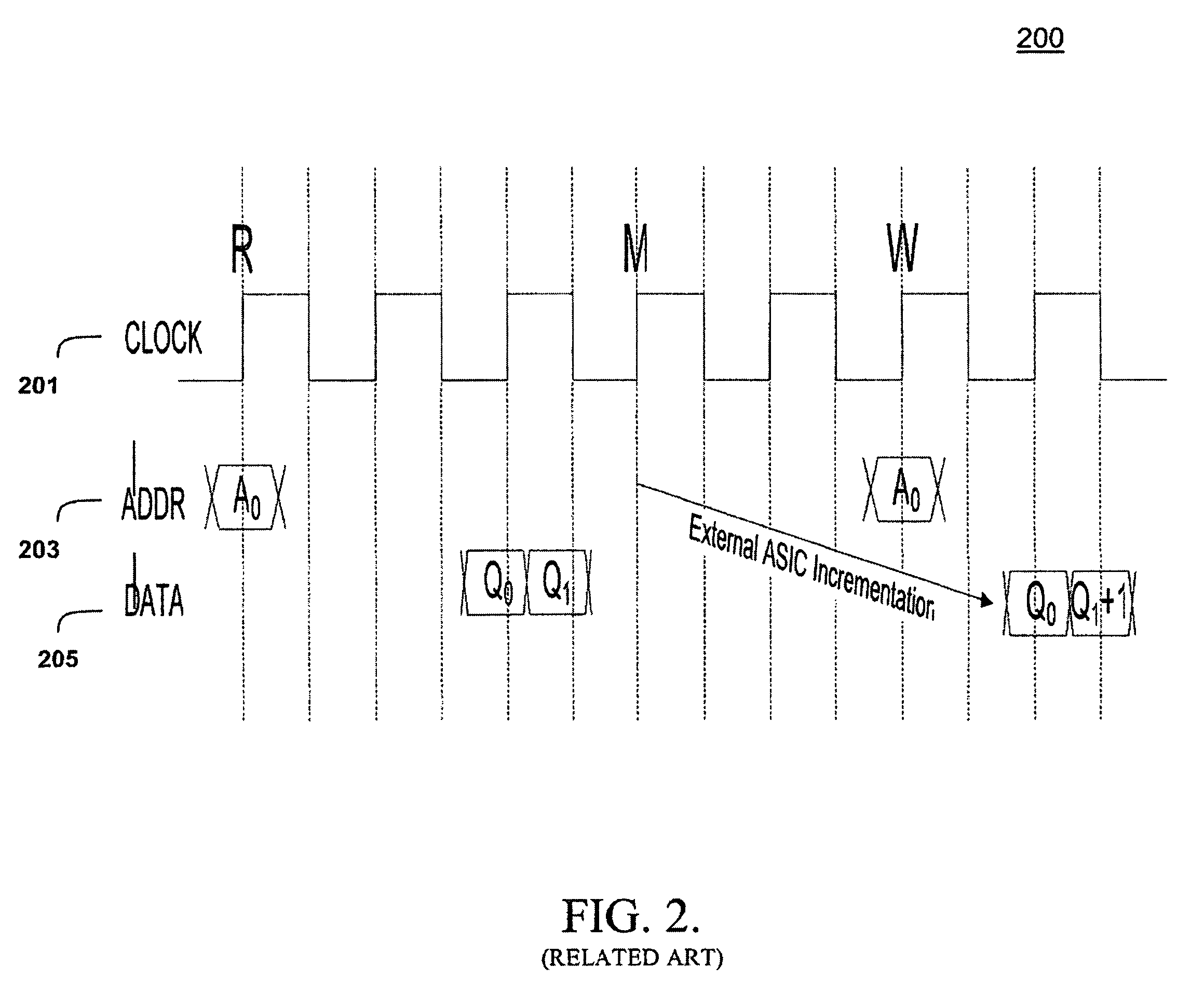

Area efficient and fast static random access memory circuit and method

Disclosed is an accumulation memory circuit for providing a fast read, modify, and write operation in a single clock cycle time. The memory circuit is configured to read data stored in the memory device at an address. The memory circuit includes a reconfigurable adder unit generating read, accumulate and write output in a single clock cycle. The memory circuit is further configured to minimize data overflow. A high speed accumulation method comprises resetting a memory circuit; reading from an address of the memory circuit; performing internal addition within the memory circuit and rewriting into the address of the memory circuit in a single clock cycle.

Owner:MONTEREY RES LLC

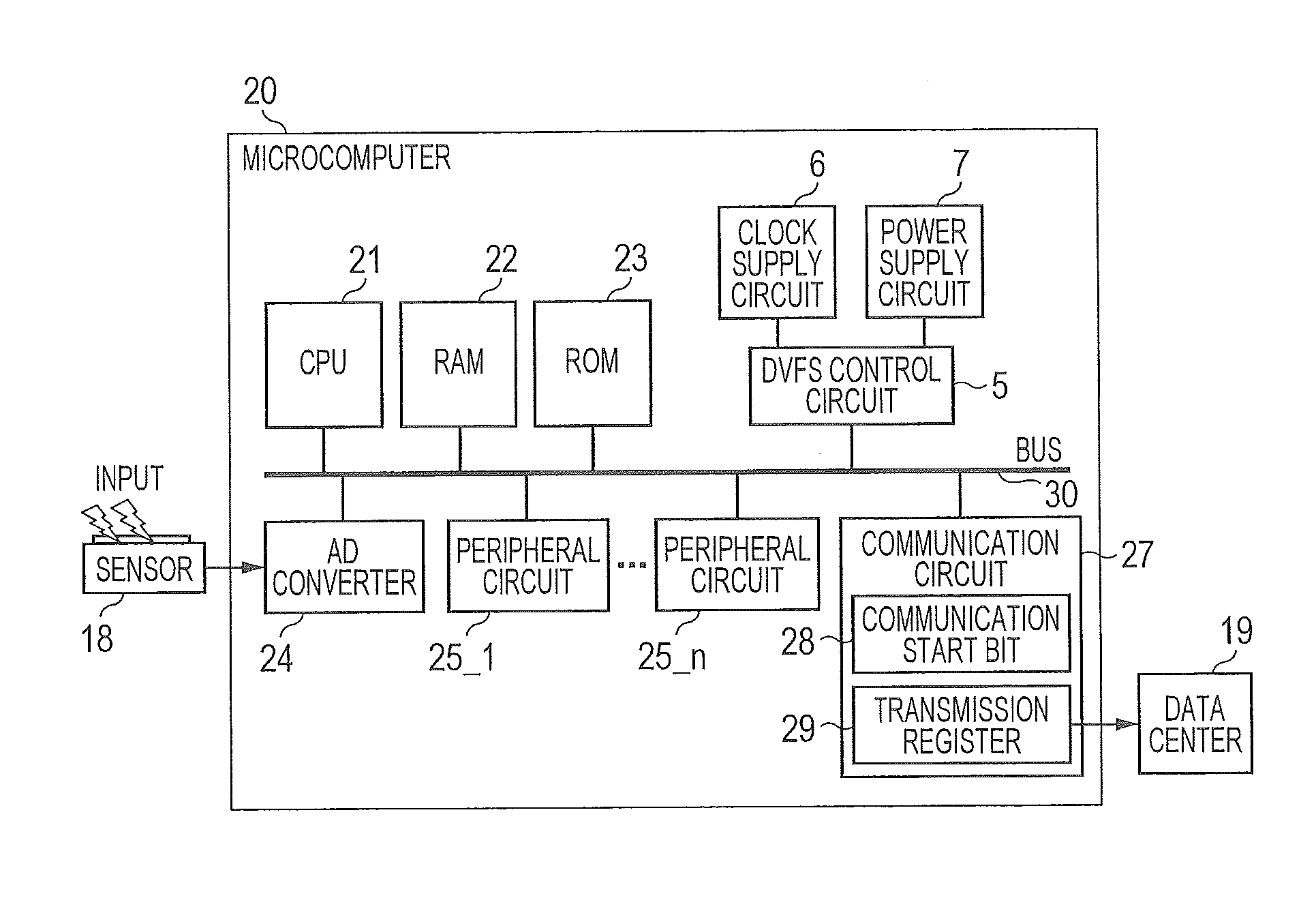

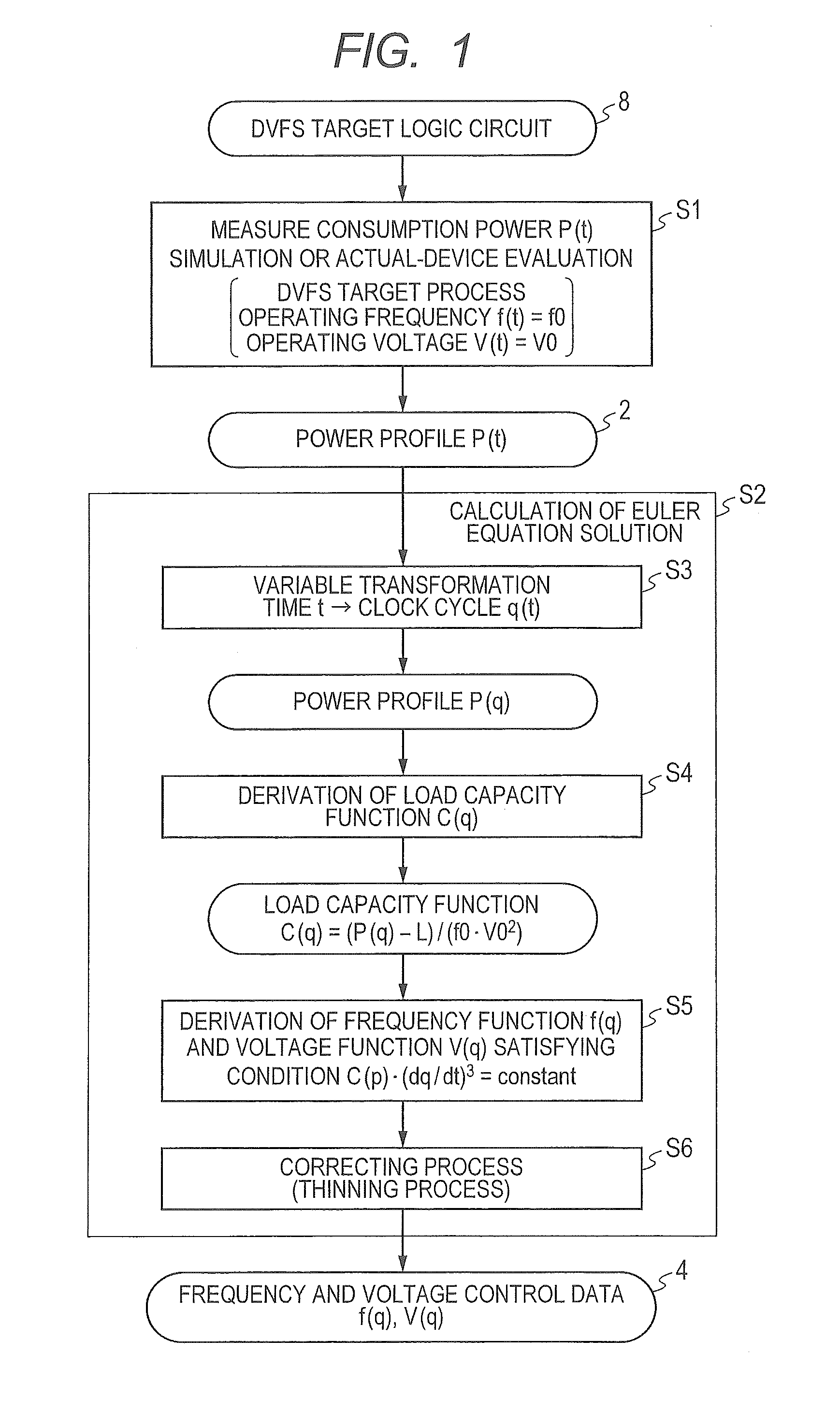

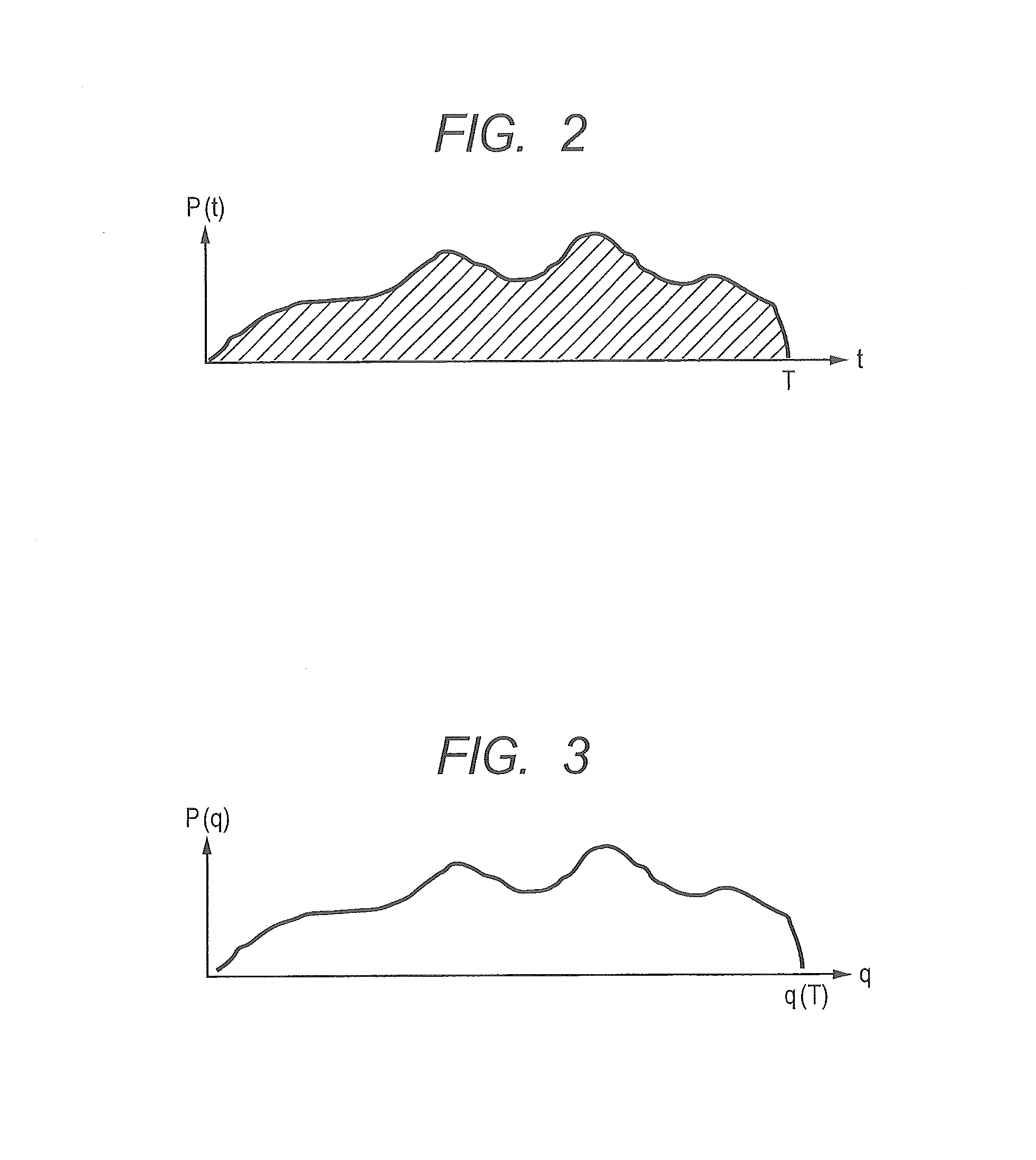

Method of Designing Semiconductor Device, Designing Assistance Program, Designing Apparatus, and Semiconductor Device

InactiveUS20150161307A1Reduce power consumptionDetecting faulty computer hardwareCAD circuit designEnergy minimizationComputer programming

The present invention provides a method of designing a semiconductor device capable of executing a DVFS control which minimizes consumption energy. A consumption power profile P(t) when a known operating voltage and a clock of a known frequency are given to a logic circuit as a DVFS target and a process as a DVFS target is executed is obtained. The obtained power profile is converted to a function related to a clock cycle q(t), and a load capacity of the target logic circuit is obtained as a function of the clock cycle q(t). An operating voltage and an operating frequency are calculated as functions (V(q), f(q)) for a clock cycle so as to satisfy a condition using, as a constant, a product (C(q)·(dq / dt){circle around ( )}3) of the load capacity function and cube of time differentiation of the clock cycle. The calculated functions of the operating voltage and the operating frequency are solutions of the Euler equation according to the calculus of variations, and consumption energy is minimized.

Owner:RENESAS ELECTRONICS CORP

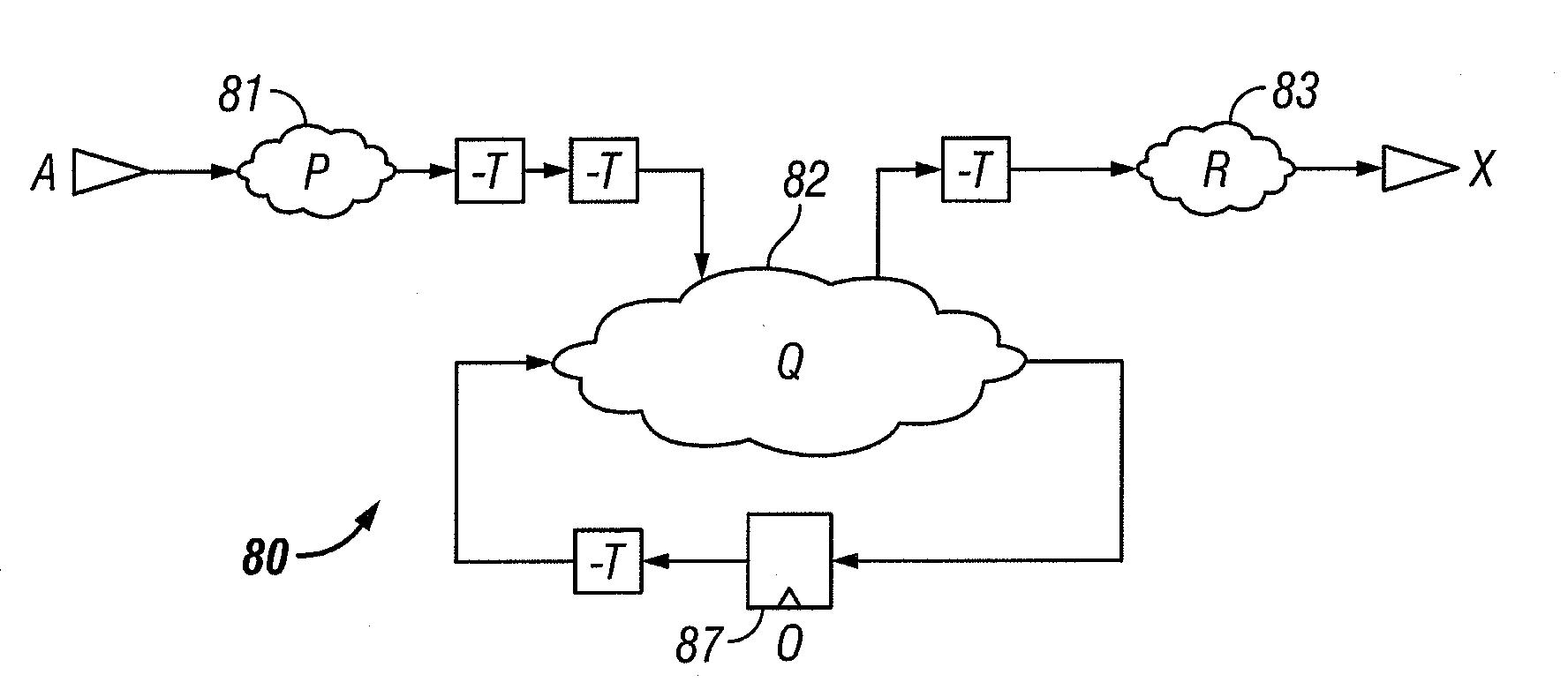

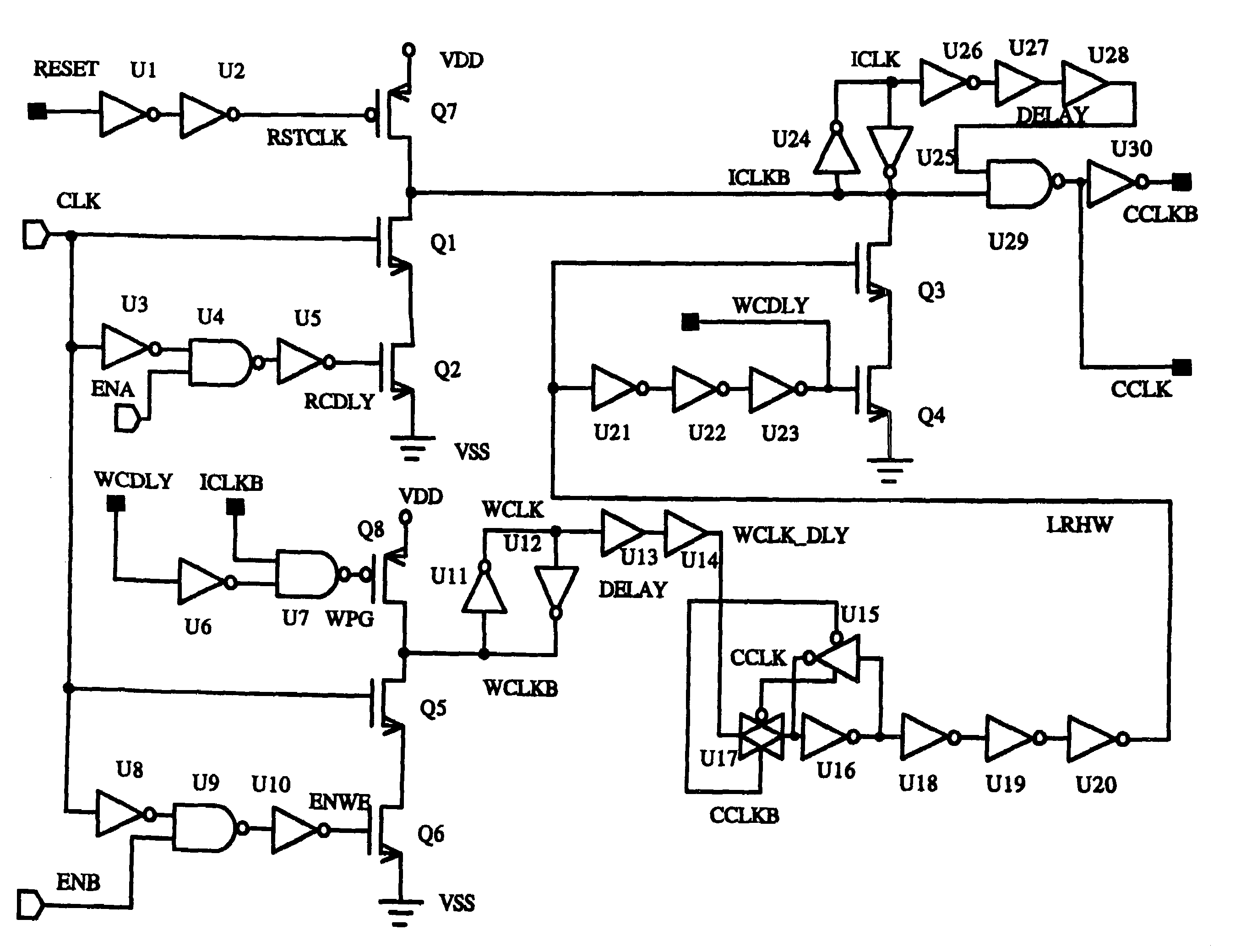

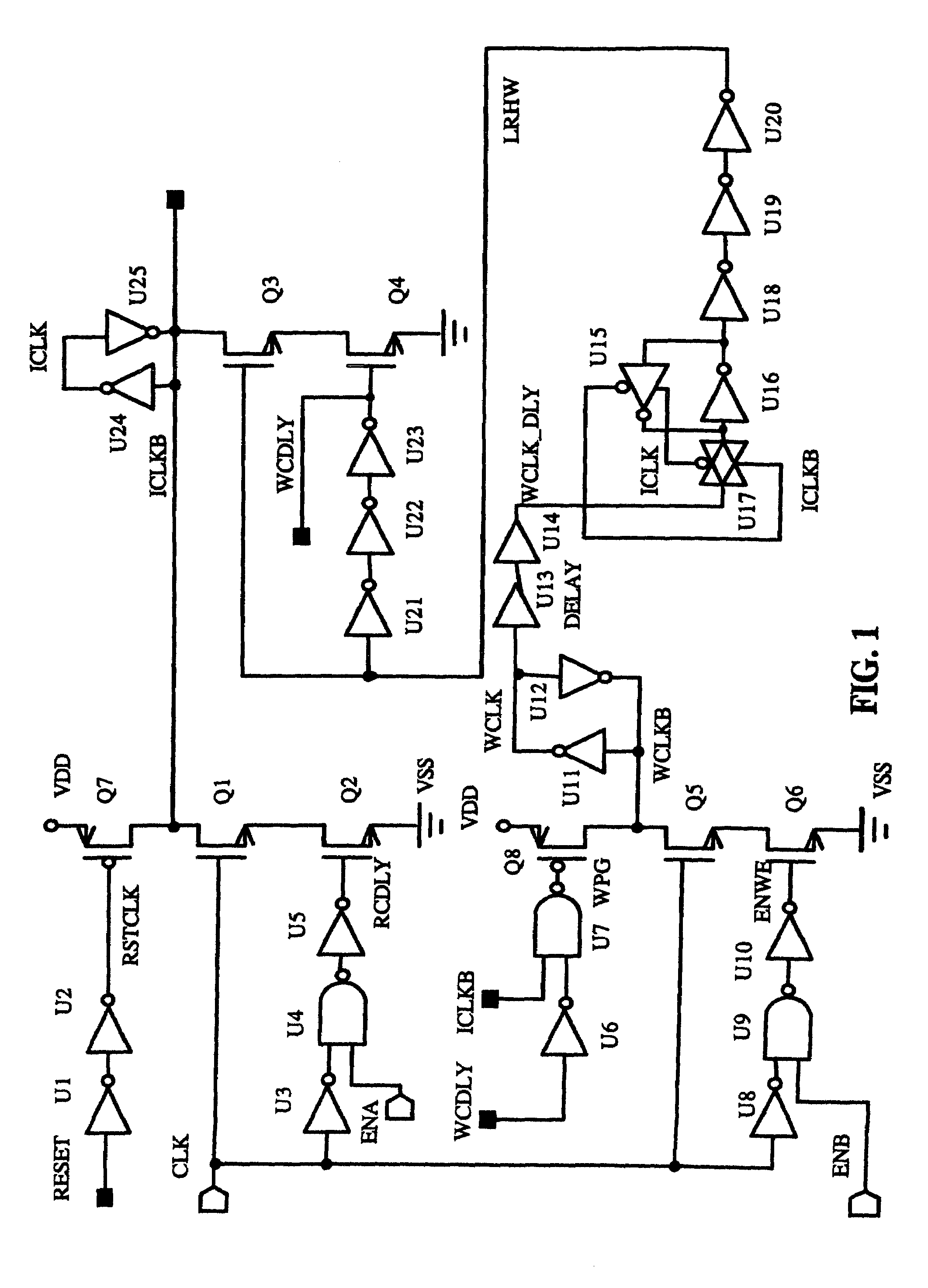

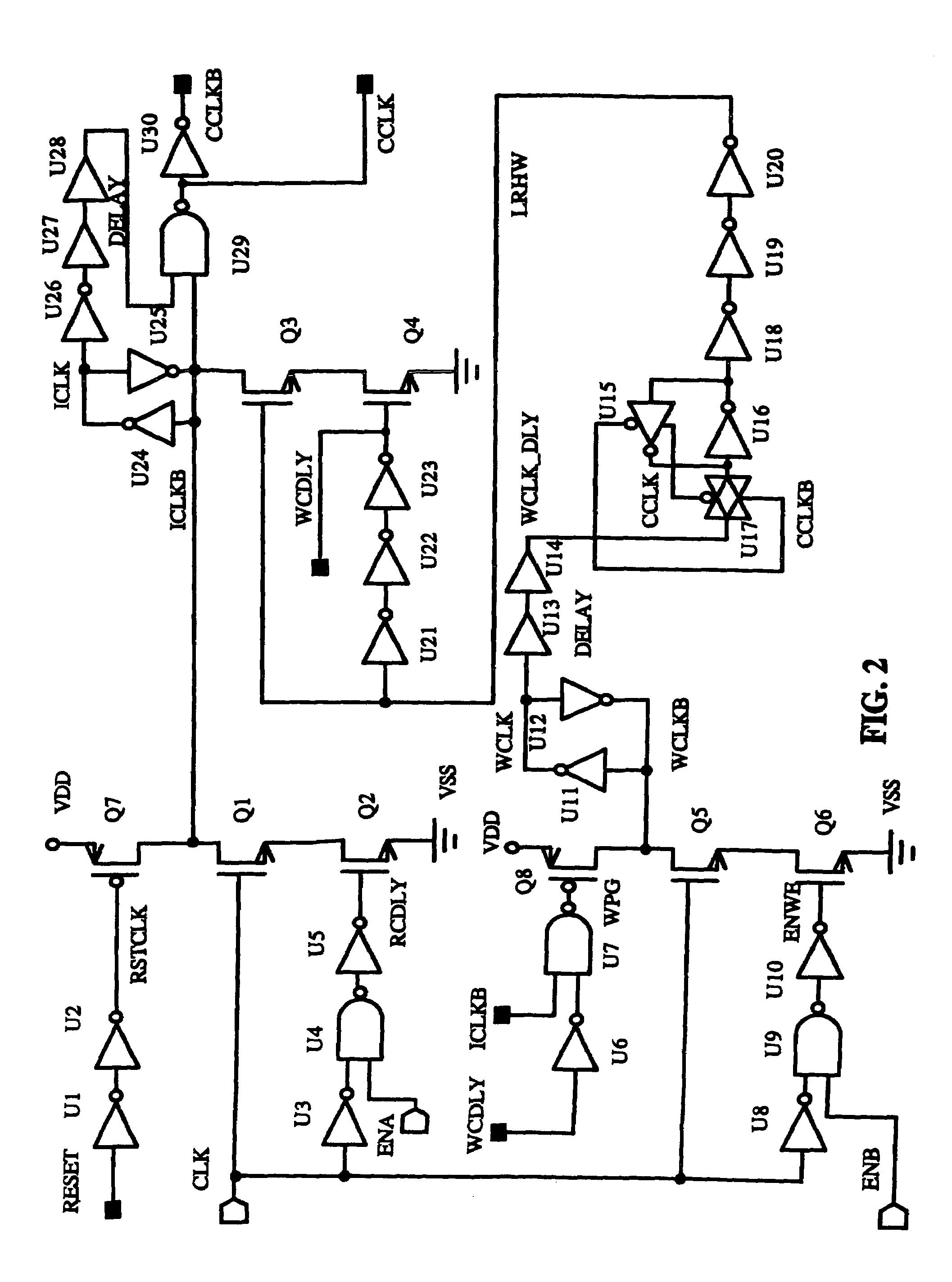

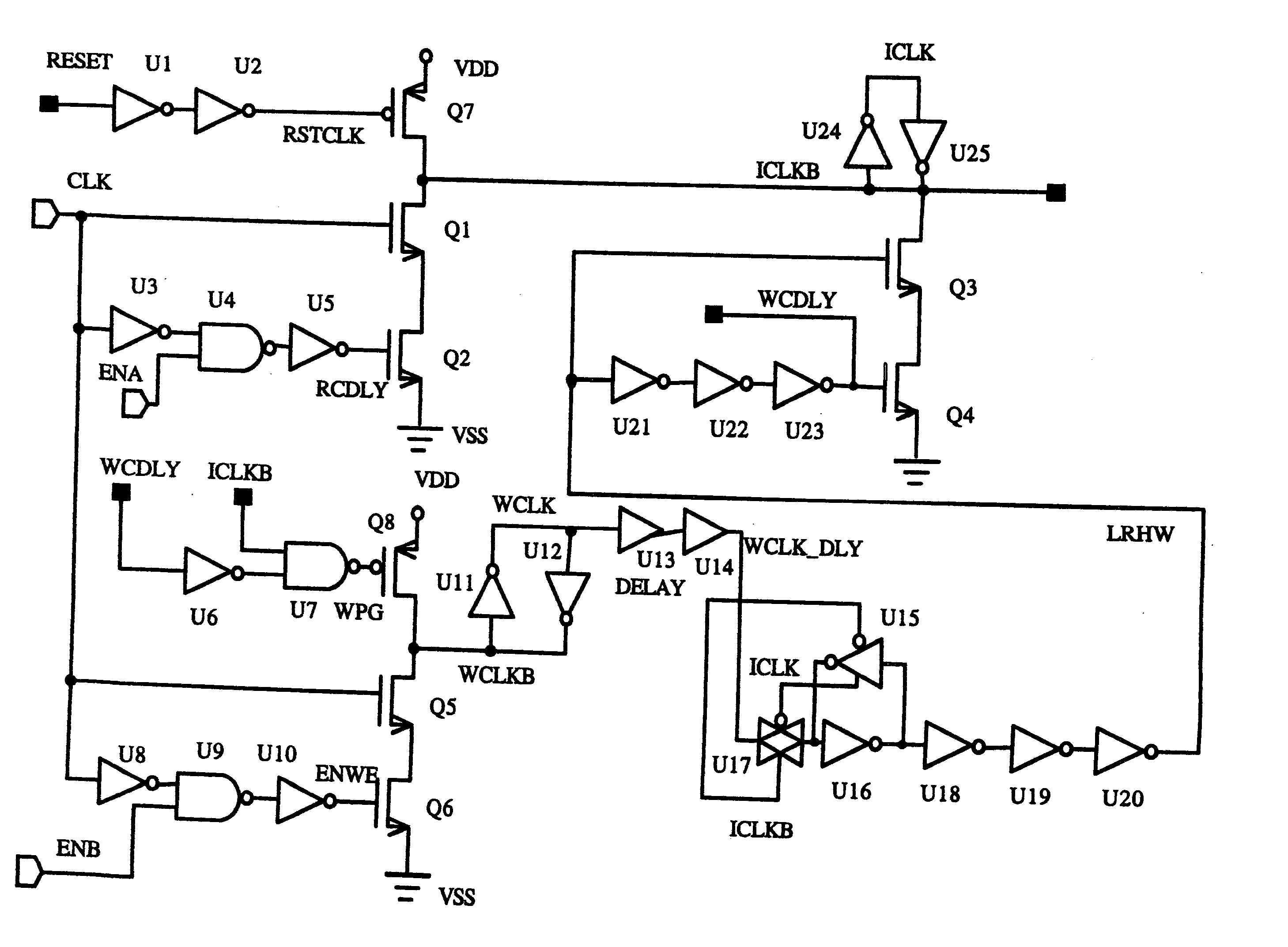

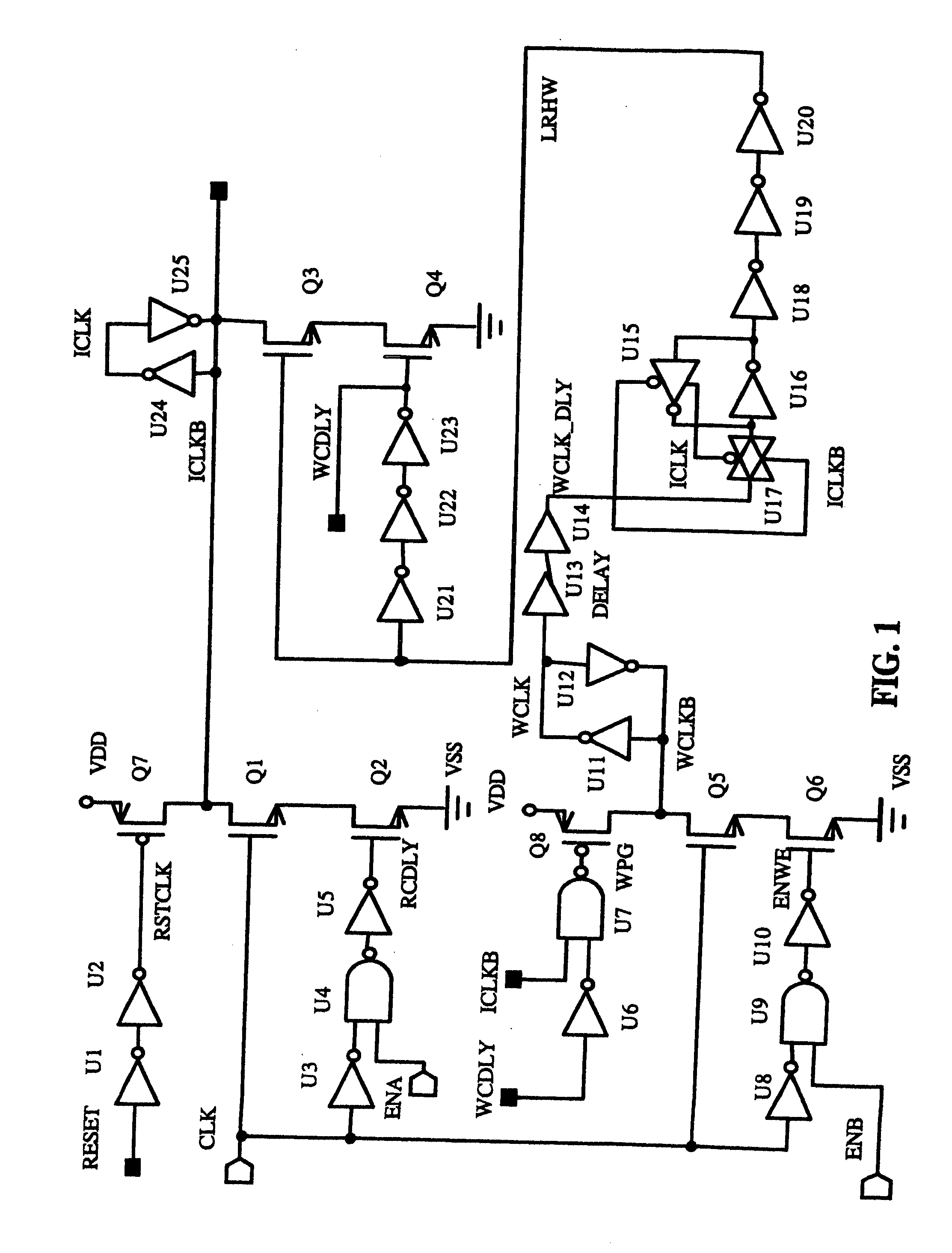

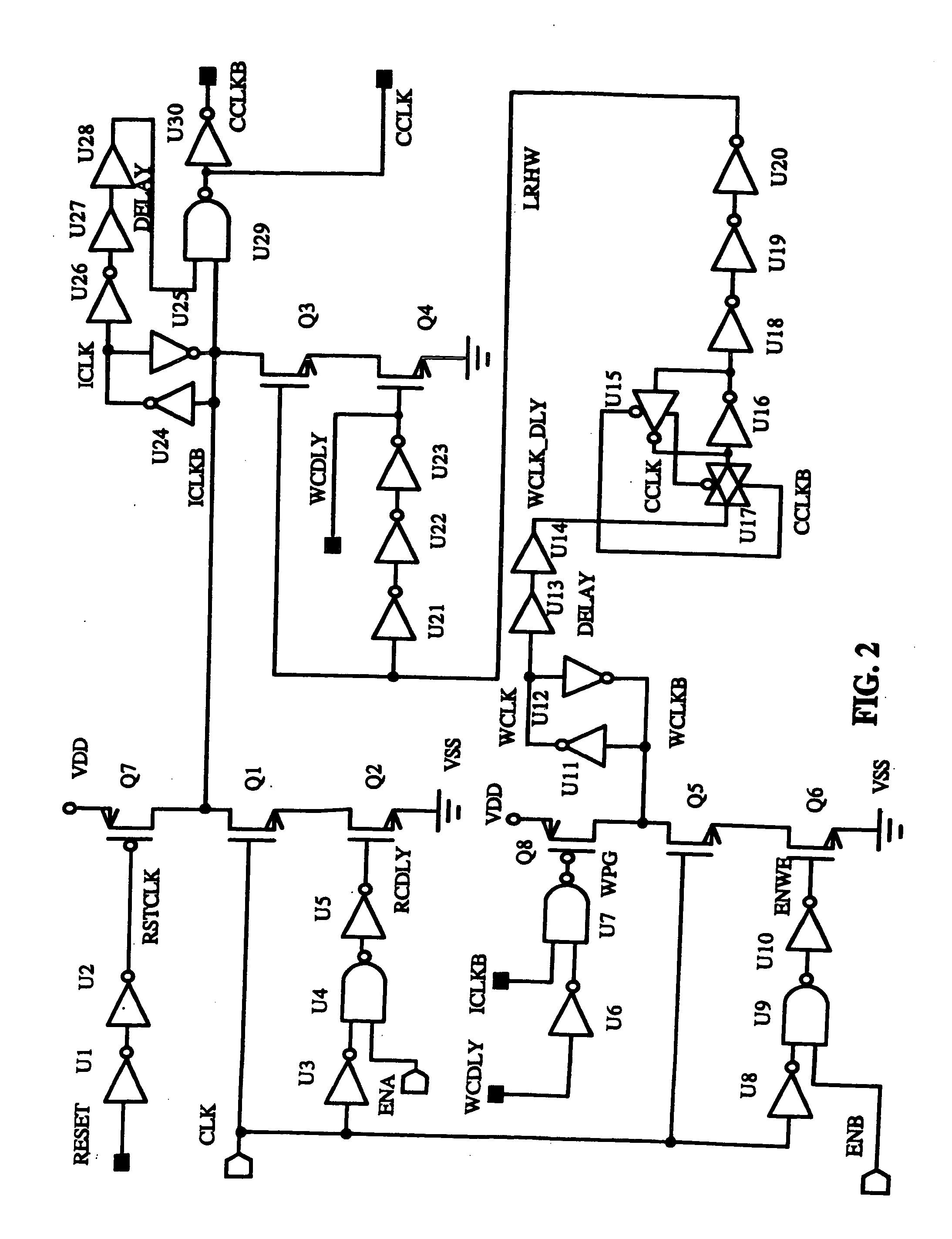

Clock generator for pseudo dual port memory

A clock generating circuit for a pseudo dual port memory incorporates feedback, delays, and latches to ensure that the write (read) operation clock pulse is sufficiently spaced in time from the read (write) operation clock. The clock generating circuit receives an external clock, a read enable signal, a write enable signal, and a reset signal as inputs. Advantages include minimization of the clock cycle time and operation unaffected by the duty ratio of an external clock. Delay circuitry may be added such that the generated clock signal has sufficient fan out and is sufficiently stable.

Owner:AVAGO TECH INT SALES PTE LTD

Clock circuit for semiconductor memories

Owner:POLARIS INNOVATIONS LTD

Method and apparatus for generating synchronization signals for synchronizing multiple chips in a system

InactiveUS7826579B2Reduce time uncertaintyPromote generationPulse automatic controlSynchronisation signal speed/phase controlPhase differenceCycle time

Owner:INT BUSINESS MASCH CORP

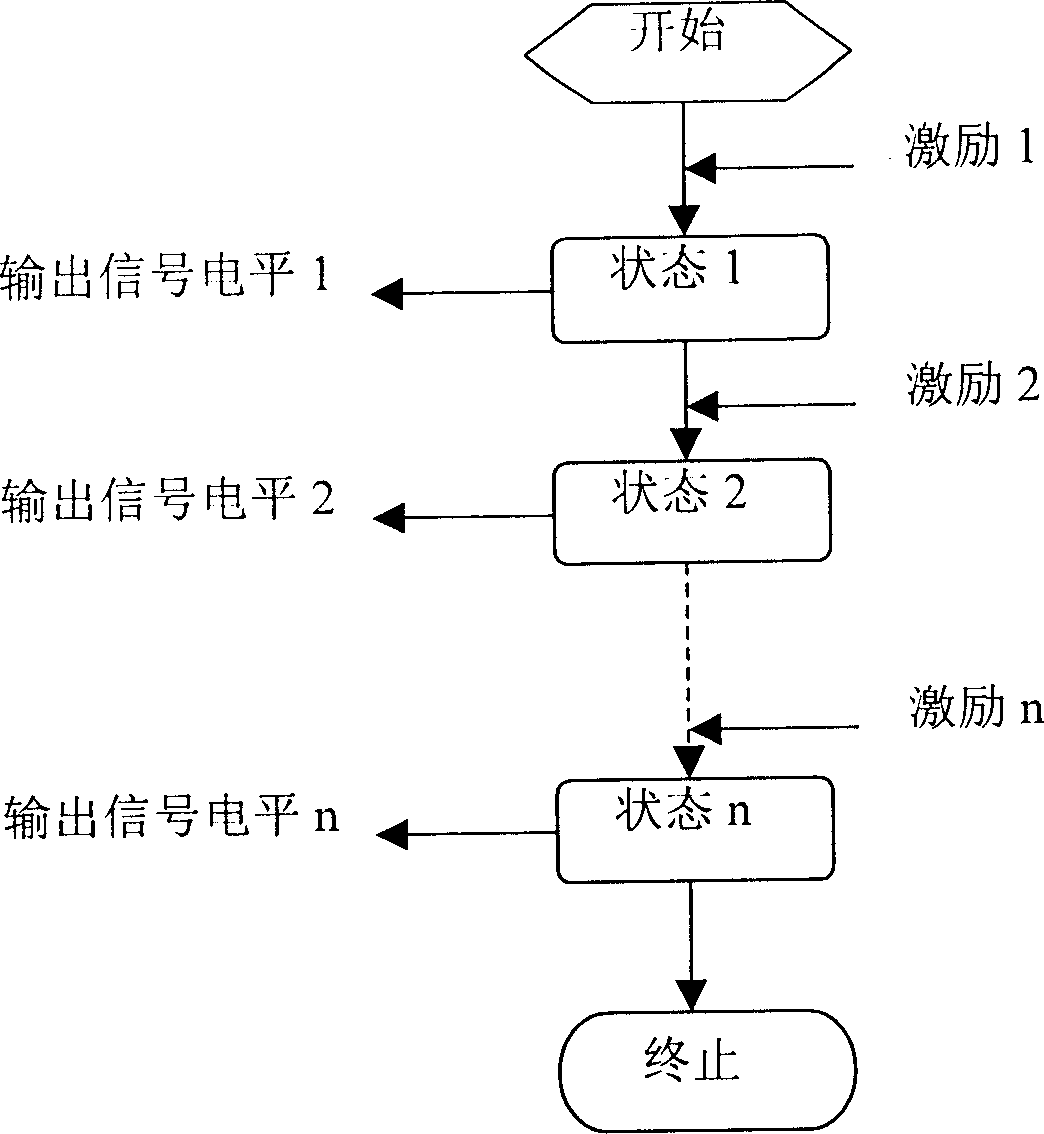

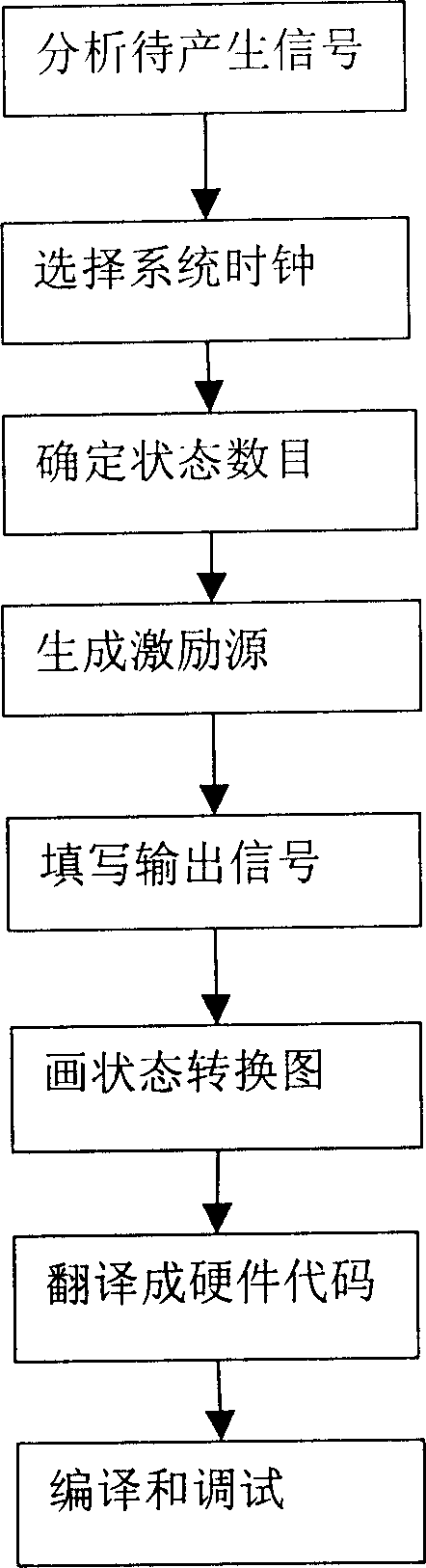

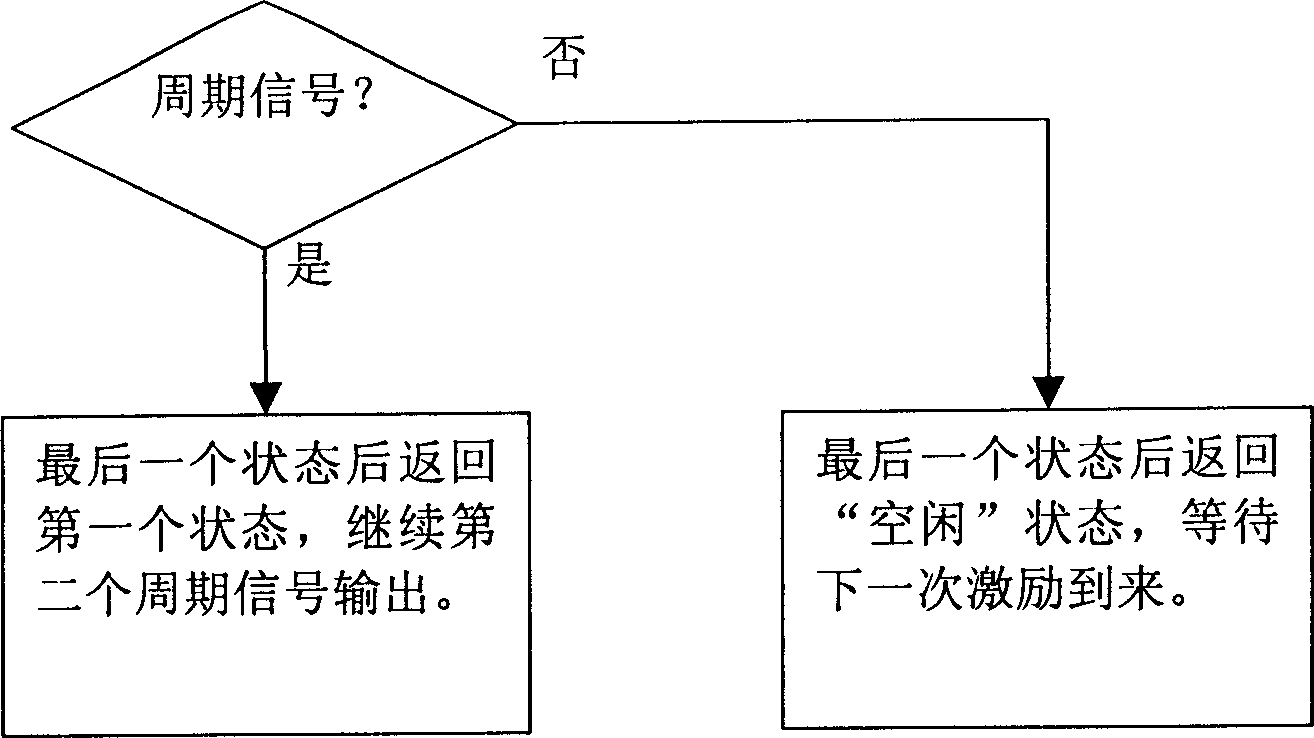

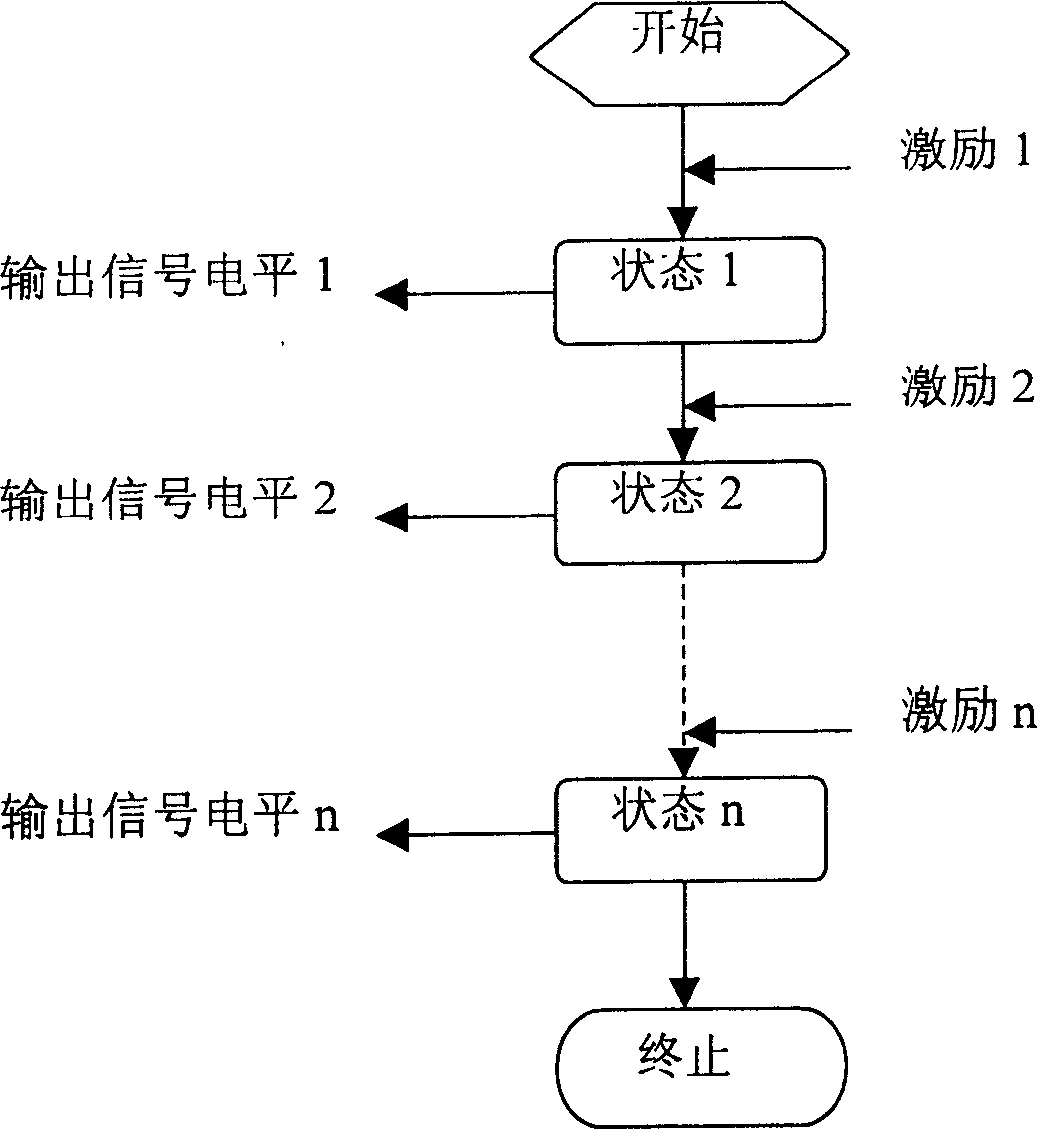

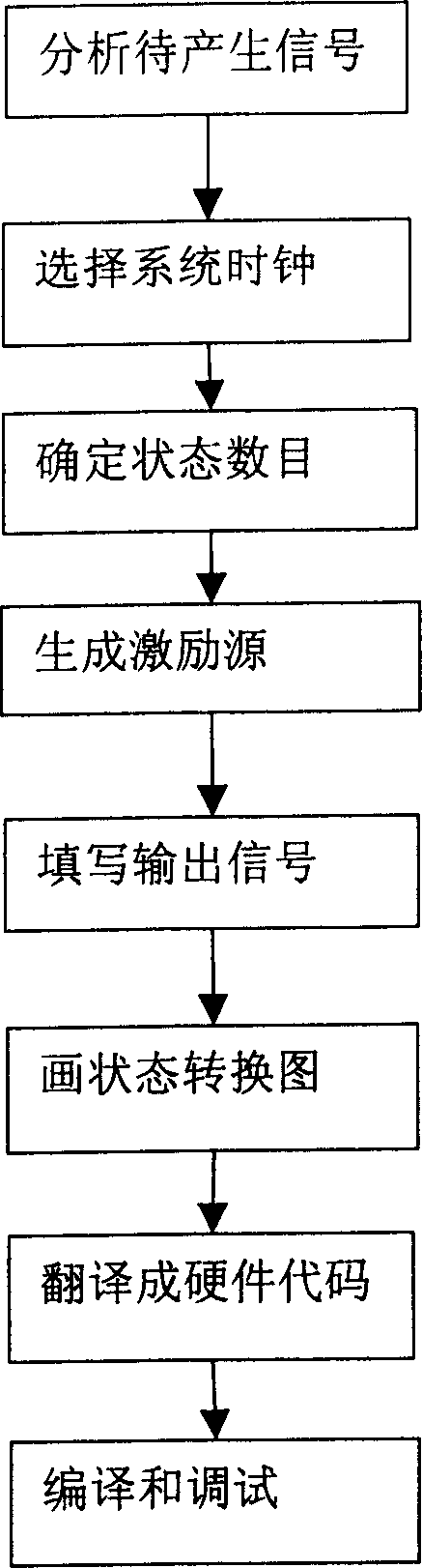

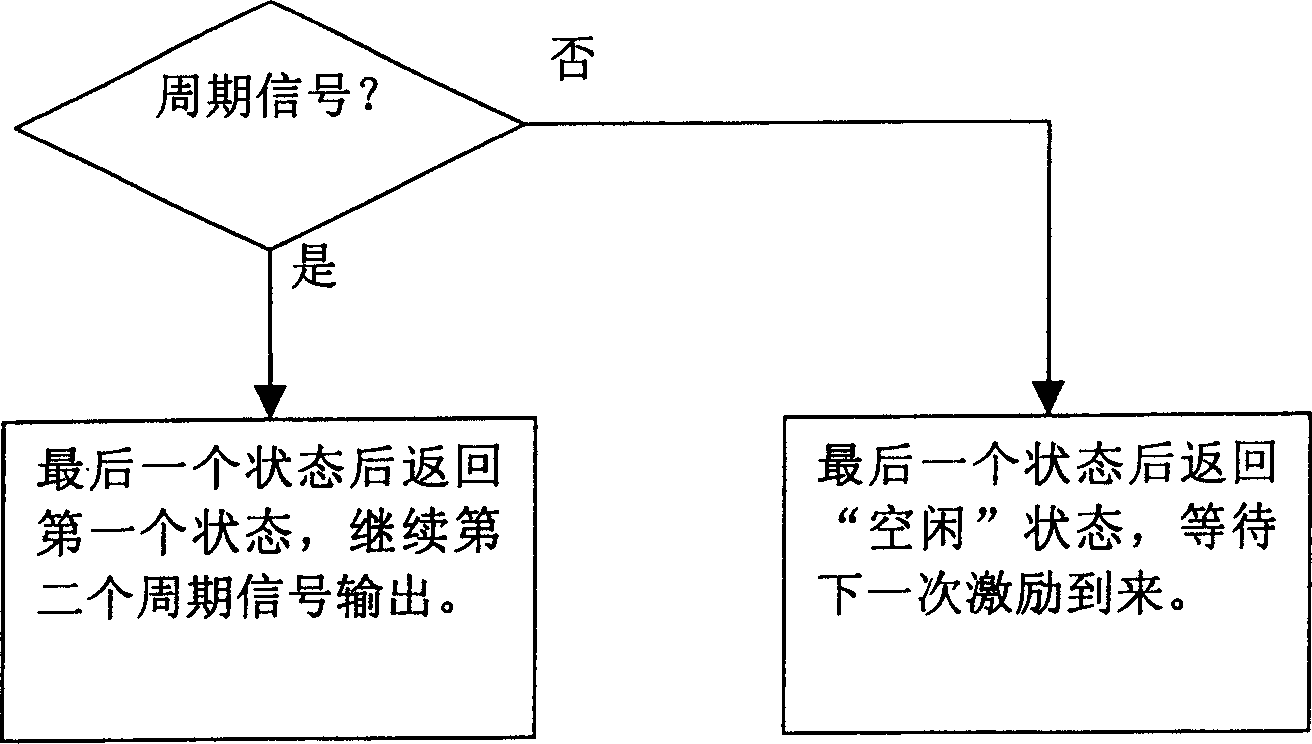

Multi channel digital signal generator

The generator comprises module for analyzing signal to be generated, module for selecting system clock, module for determining status number, and module for generating excitation source. With external condition being met, under driving of time clock, finite state machine completes state transition in sequence as well as outputs digital signal waveform in designated number. When external excitation condition is met, finite state machine enters a state in every other clock cycle time. Under different states, finite state machine outputs different signal levels. The invention provides a method of generating digital signal with multiple channels and arbitrary duty ratio for personnel of programming hardware. The functional modules can be integrated into users' programmable hardware design simply and seamlessly.

Owner:NO 30 INST OF CHINA ELECTRONIC TECH GRP CORP

Branch history with polymorphic indirect branch information

ActiveUS8782384B2Improve forecast accuracyImprove accuracyDigital computer detailsSpecific program execution arrangementsShift registerTarget array

A system and method for efficient improvement of branch prediction in a microprocessor with negligible impact on die-area, power consumption, and clock cycle period. It is determined if a program counter (PC) register contains a polymorphic indirect unconditional branch (PIUB) instruction. One determination may be searching a table with a portion or all of a PC of past PIUB instructions. If a hit occurs in this table, the global shift register (GSR) is updated by shifting a portion of the branch target address into the GSR, rather than updating the GSR with a taken / not-taken prediction bit. The stored value in the GSR is input into a hashing function along with the PC in order to index prediction tables such as a pattern history table (PHT), a branch target buffer (BTB), an indirect target array, or other. The updated value due to the PIUB instruction improves the accuracy of the prediction tables.

Owner:ADVANCED MICRO DEVICES INC

Clock generator for pseudo dual port memory

A clock generating circuit for a pseudo dual port memory incorporates feedback, delays, and latches to ensure that the write (read) operation clock pulse is sufficiently spaced in time from the read (write) operation clock. The clock generating circuit receives an external clock, a read enable signal, a write enable signal, and a reset signal as inputs. Advantages include minimization of the clock cycle time and operation unaffected by the duty ratio of an external clock. Delay circuitry may be added such that the generated clock signal has sufficient fan out and is sufficiently stable.

Owner:AVAGO TECH INT SALES PTE LTD

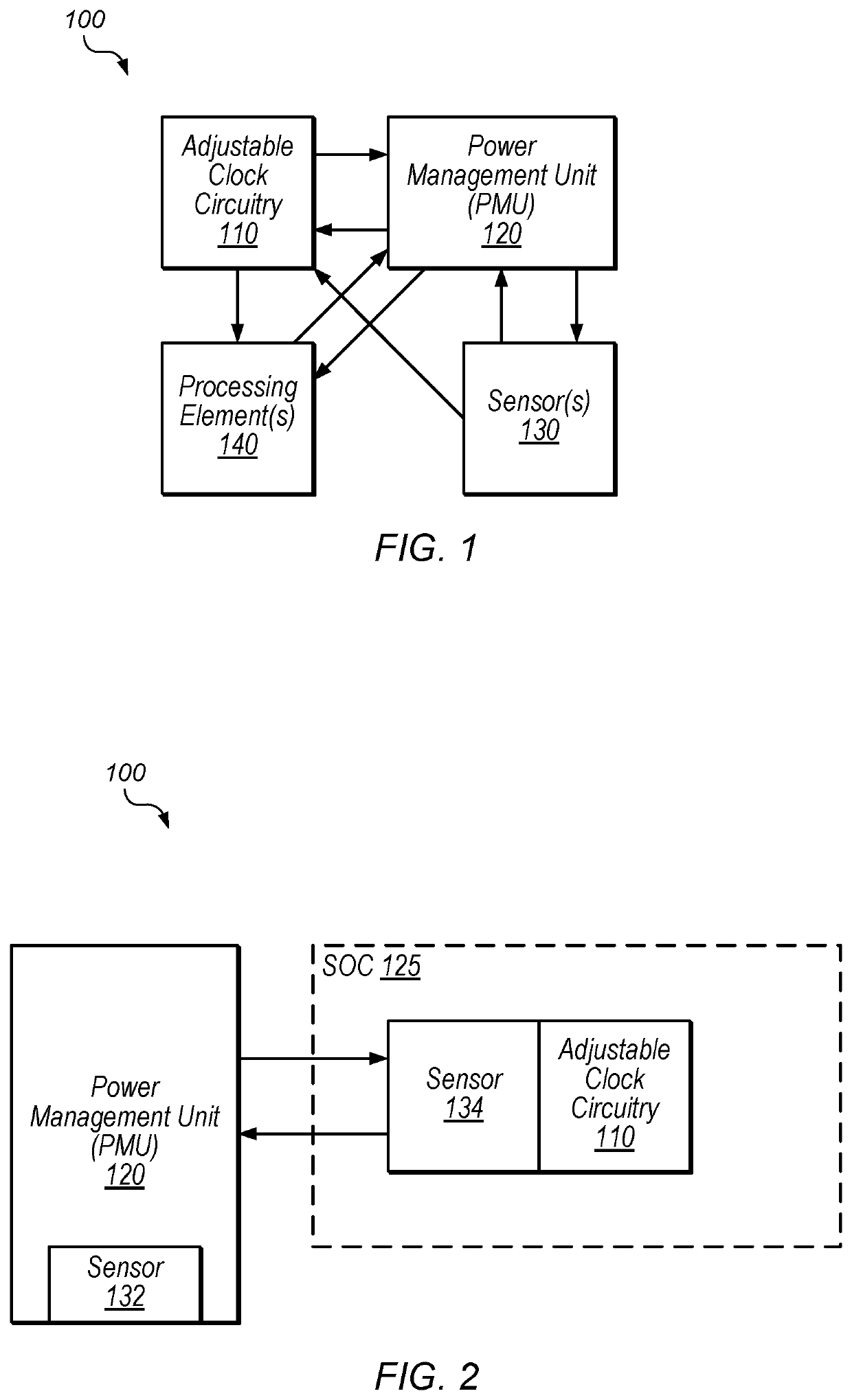

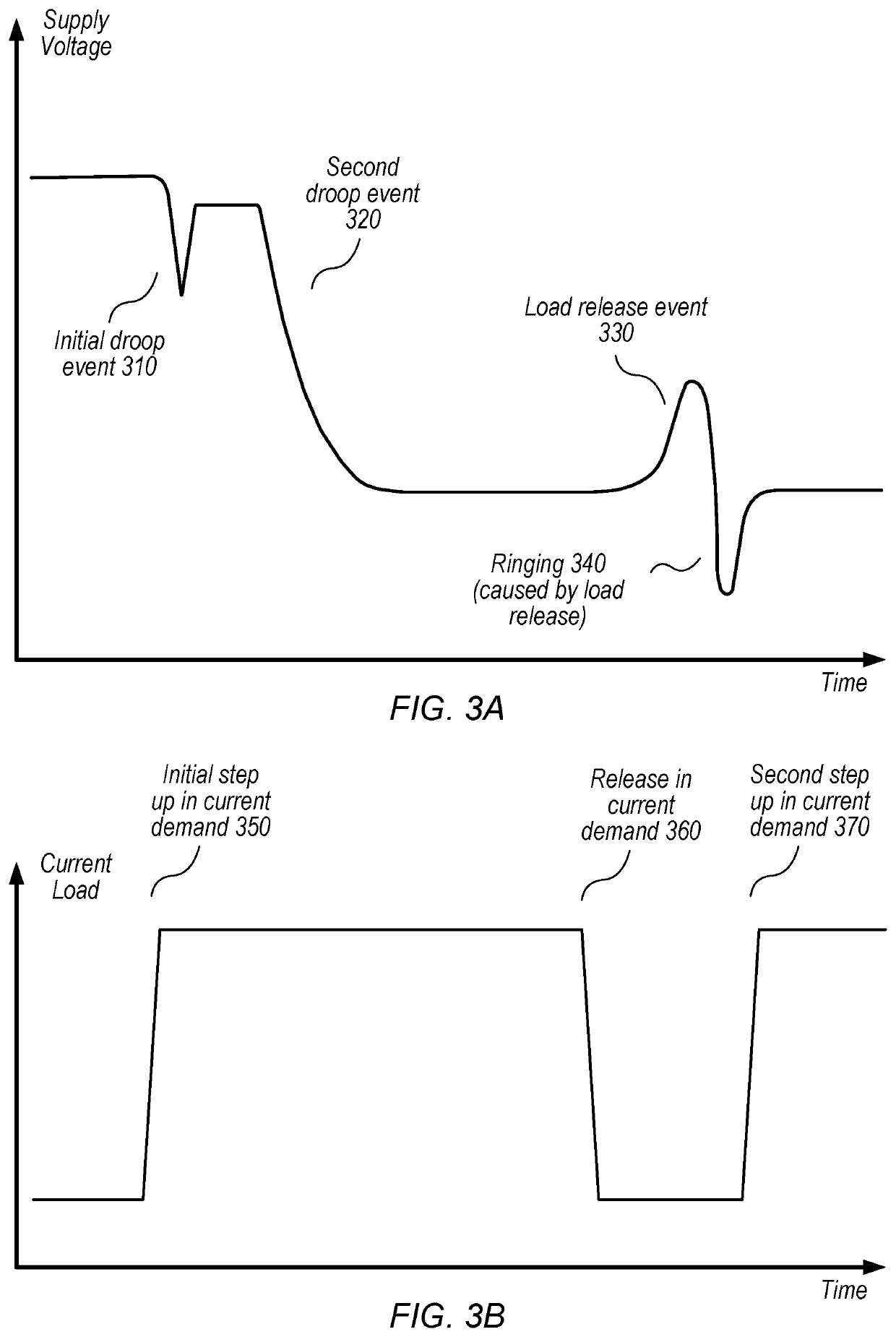

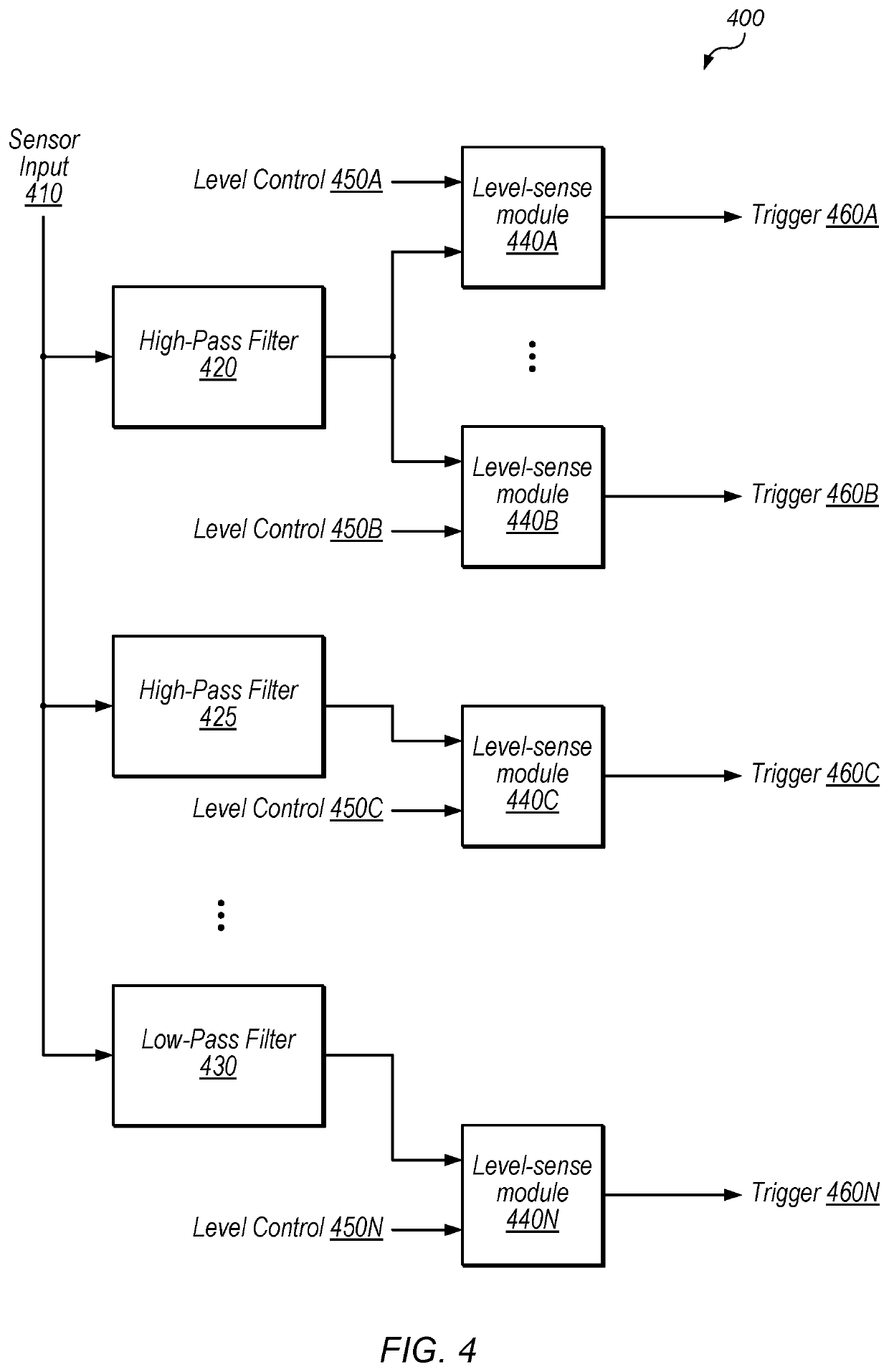

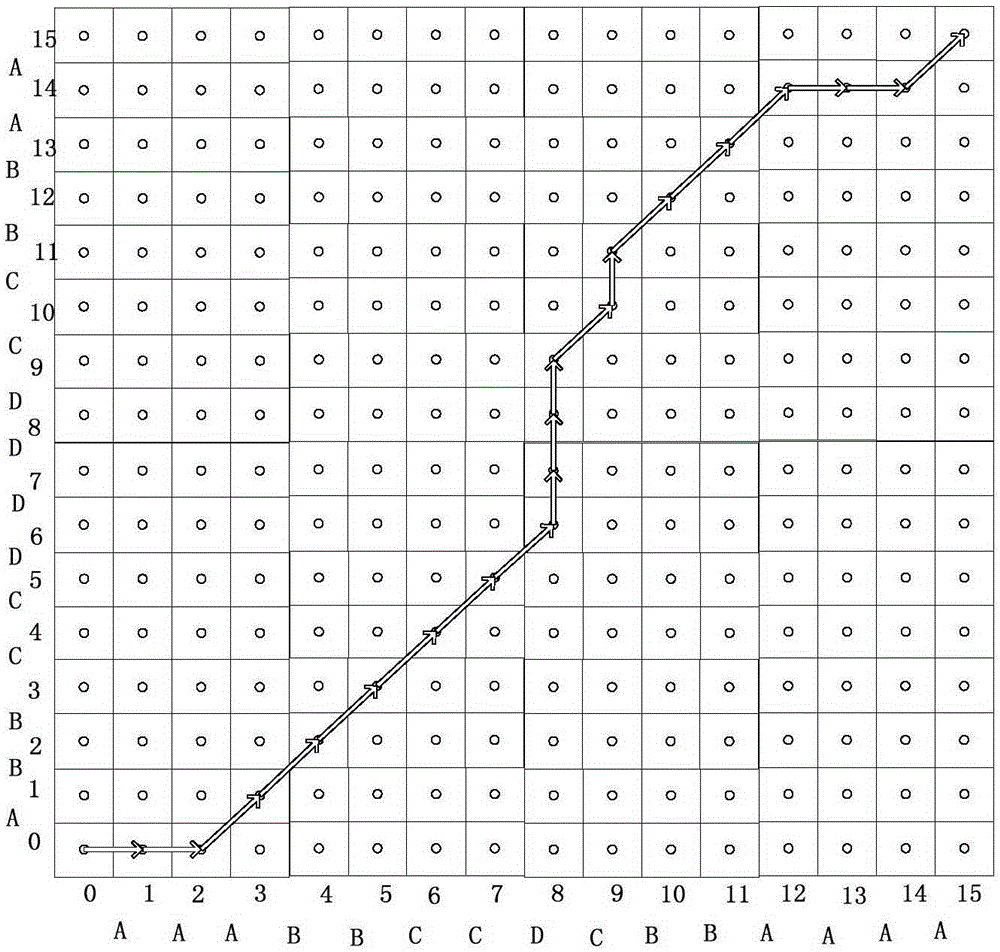

Detecting power supply noise events and initiating corrective action

ActiveUS10581440B2Extension of timePulse automatic controlGenerator stabilizationHemt circuitsControl circuit

Techniques are disclosed relating to detecting supply voltage events and performing corrective actions. In some embodiments, an apparatus includes sensor circuitry and control circuitry. In some embodiments, the sensor circuitry is configured to monitor supply voltage from a power supply and detect a load release event that includes an increase in the supply voltage that meets one or more pre-determined threshold parameters. In some embodiments, the control circuitry is configured to increase clock cycle time for operations performed by circuitry powered by the supply voltage during a time interval, wherein the time interval corresponds to ringing of the supply voltage that reduces the supply voltage and results from the load release event. In some embodiments, the disclosed techniques may reduce transients in supply voltage (which may avoid equipment damage and computing errors) and may allow for reduced voltage margins (which may reduce overall power consumption).

Owner:APPLE INC

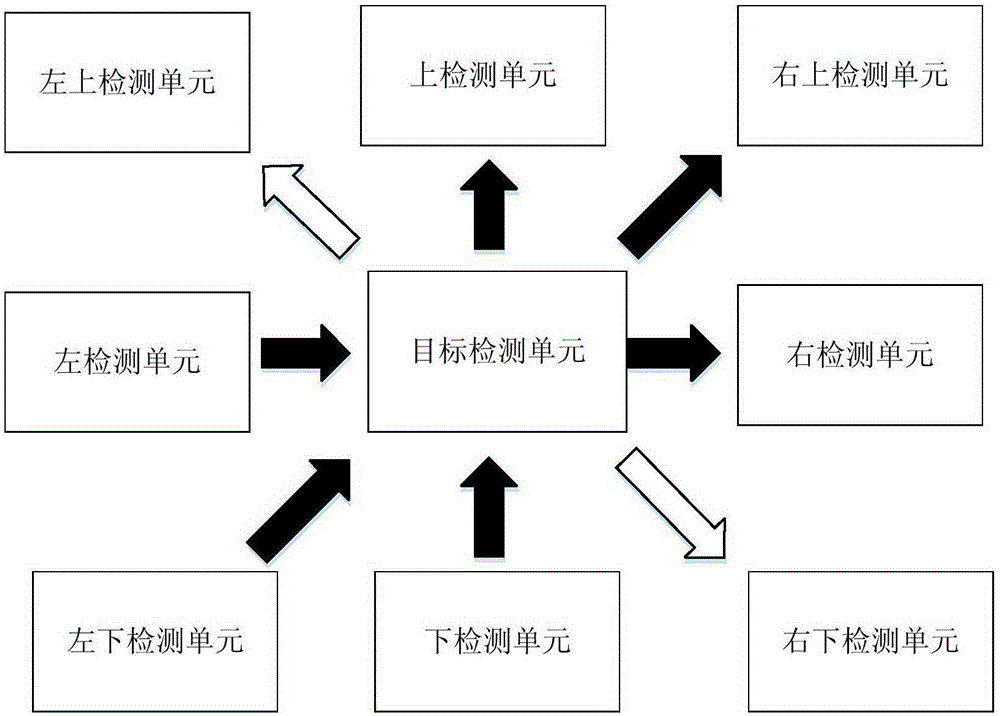

Similarity detection device

The embodiment of the invention provides a similarity detection device. Time delays are carried out by counters of detection units; different sequence operations have different delayed clock periods; the detection units output high level by output circuits corresponding to the sequence operations when the count values of the counters reach the delayed clock periods; since all the sequence operations have different delayed clock periods, time, for inputting a signal, of each detection unit is also different from that of the other detection units; when one input of each detection unit becomes the high level, the delay from an initial detection unit to the detection unit is minimum; the delayed clock period of each detection unit can be obtained by an input end which is recorded by a path module and firstly becomes the high level, so that the similarity of two sequences is obtained by the delayed clock periods of all the detection units. According to the device provided by the invention, the similarity of the two sequences are represented by the clock periods, thereby avoiding the problem of overflowing as the weight is too large due to weight accumulation in the prior art.

Owner:HONOR DEVICE CO LTD

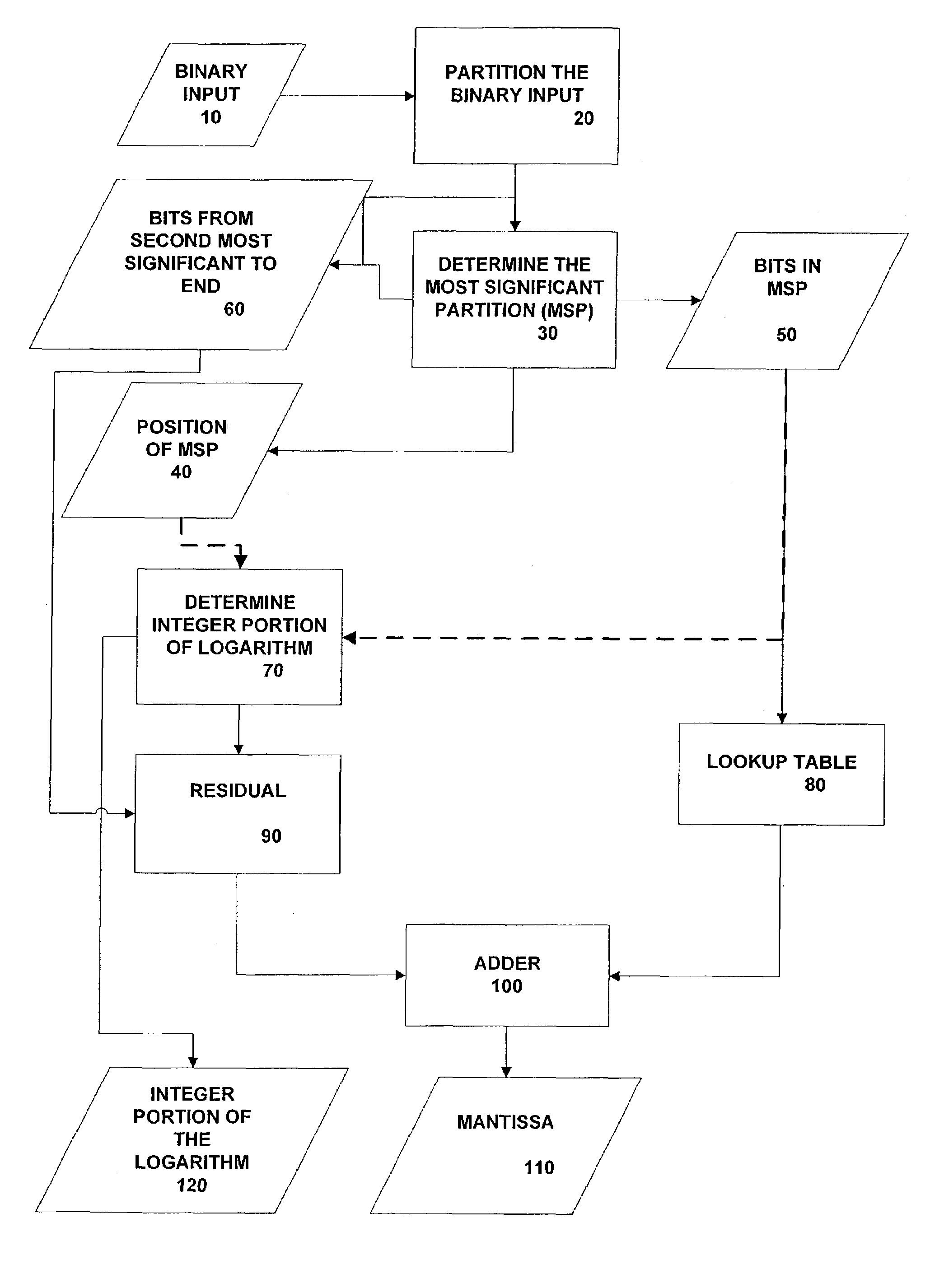

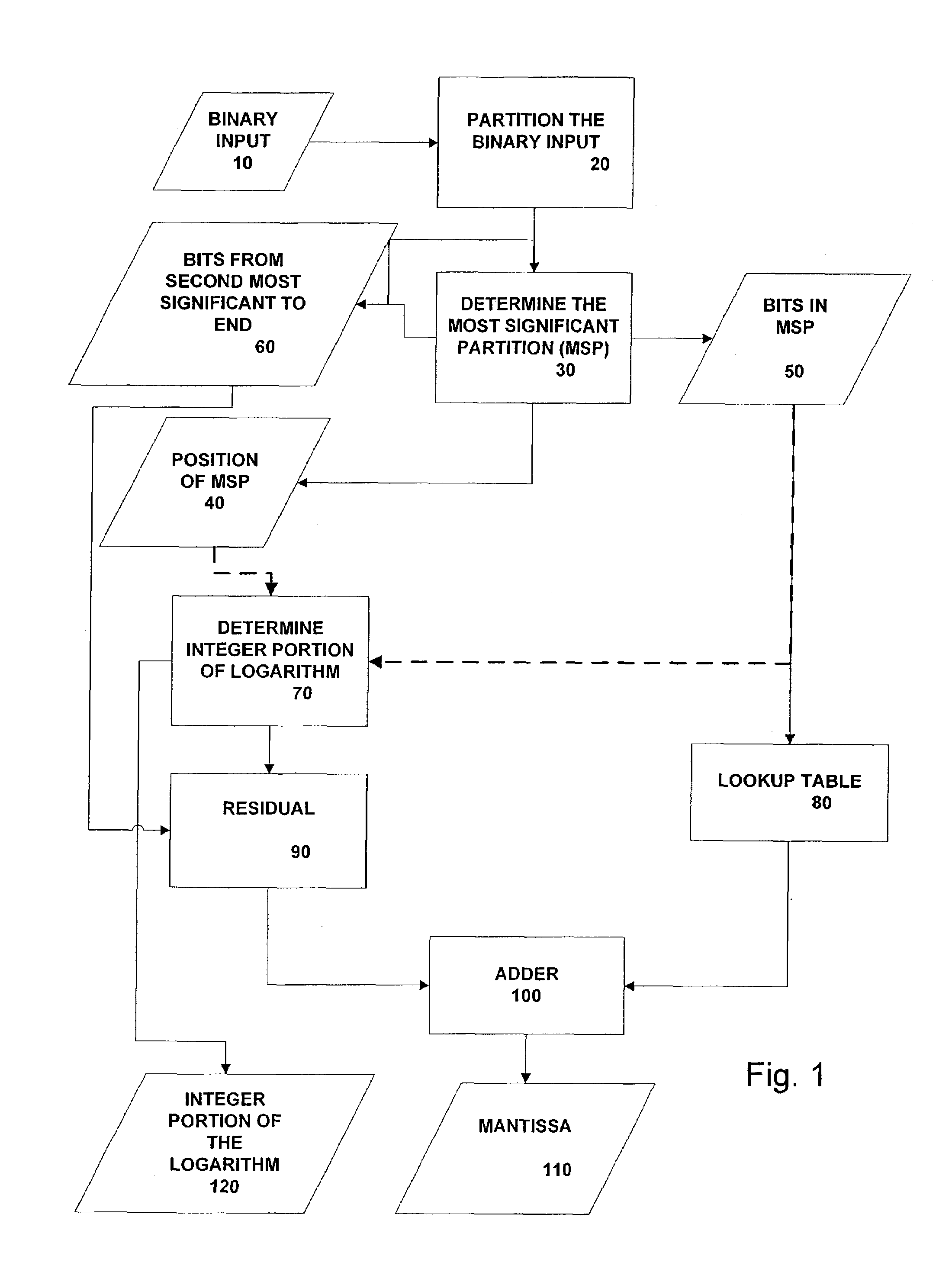

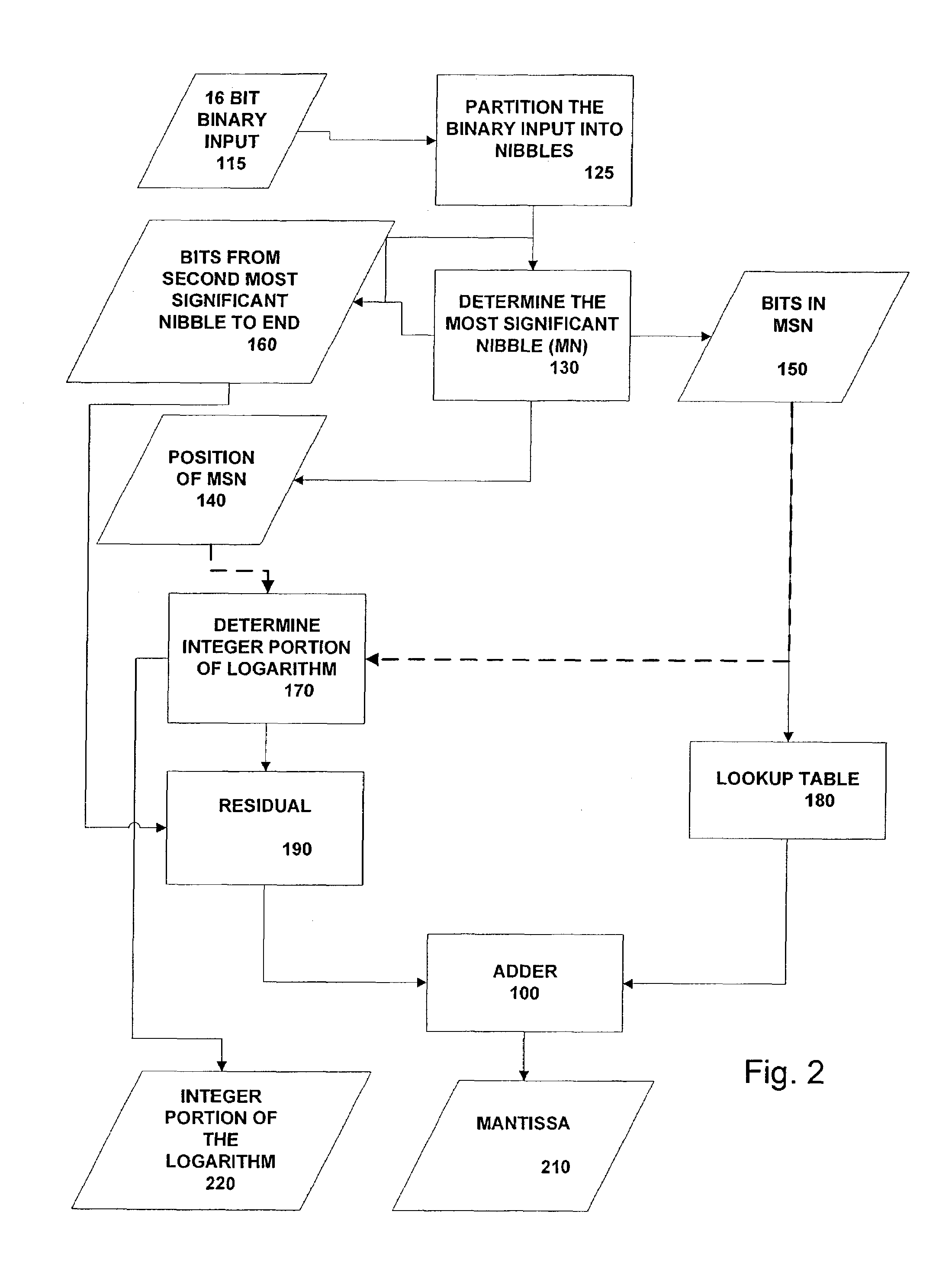

Circuits and methods for implementing approximations to logarithms

InactiveUS7266576B2Calculation is simple and fastDigital function generatorsComputation using denominational number representationProcessor registerLookup table

A method for approximating a base 2 logarithm of a binary input and the circuit to implement the method are disclosed. The circuit comprises means for determining the integer portion of the logarithm, a lookup table module, a residual function module, an adder module and a register. This circuit performs the approximation in one system clock cycle time.

Owner:LOCKHEED MARTIN CORP

Multi channel digital signal generator

The generator comprises module for analyzing signal to be generated, module for selecting system clock, module for determining status number, and module for generating excitation source. With external condition being met, under driving of time clock, finite state machine completes state transition in sequence as well as outputs digital signal waveform in designated number. When external excitation condition is met, finite state machine enters a state in every other clock cycle time. Under different states, finite state machine outputs different signal levels. The invention provides a method of generating digital signal with multiple channels and arbitrary duty ratio for personnel of programming hardware. The functional modules can be integrated into users' programmable hardware design simply and seamlessly.

Owner:NO 30 INST OF CHINA ELECTRONIC TECH GRP CORP

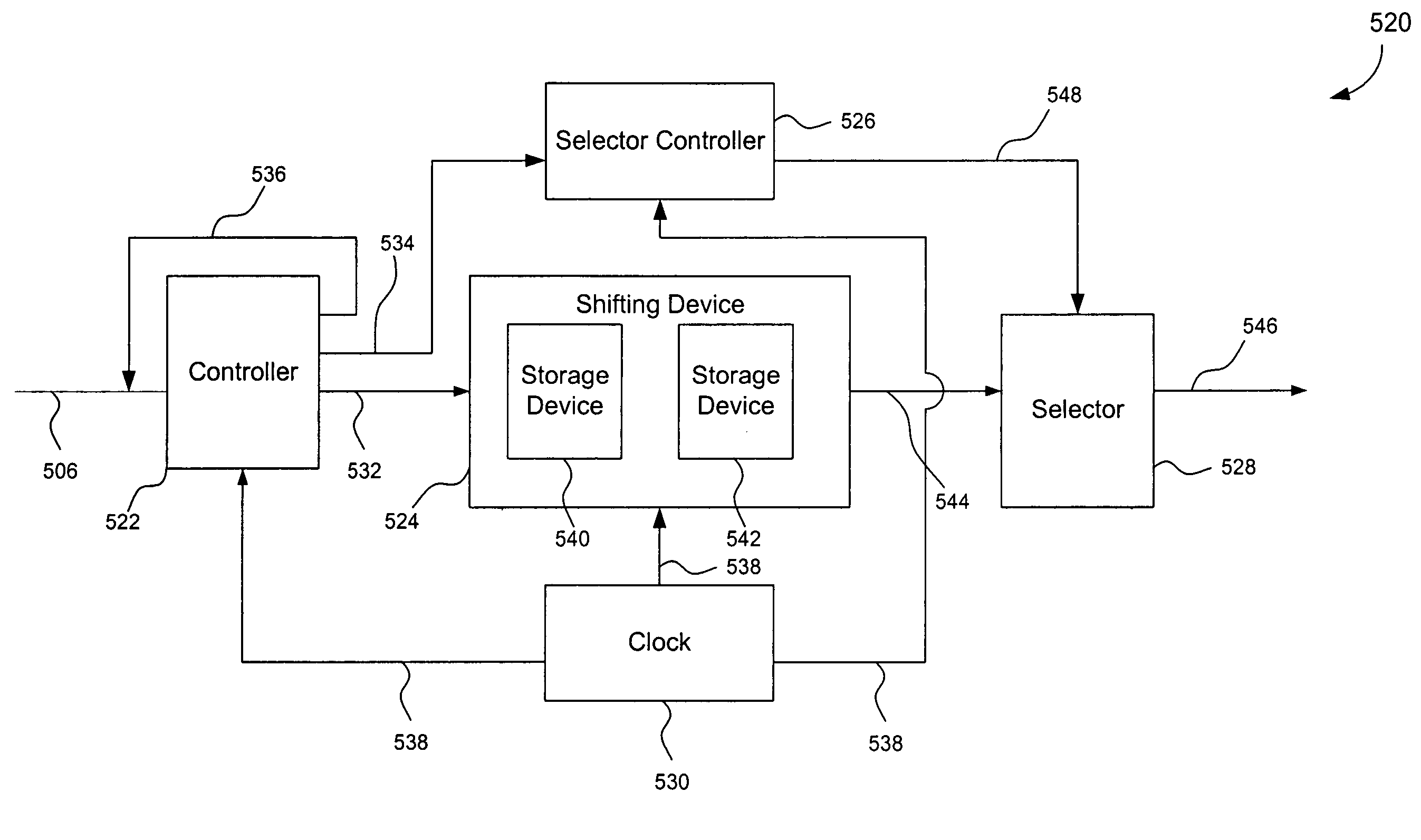

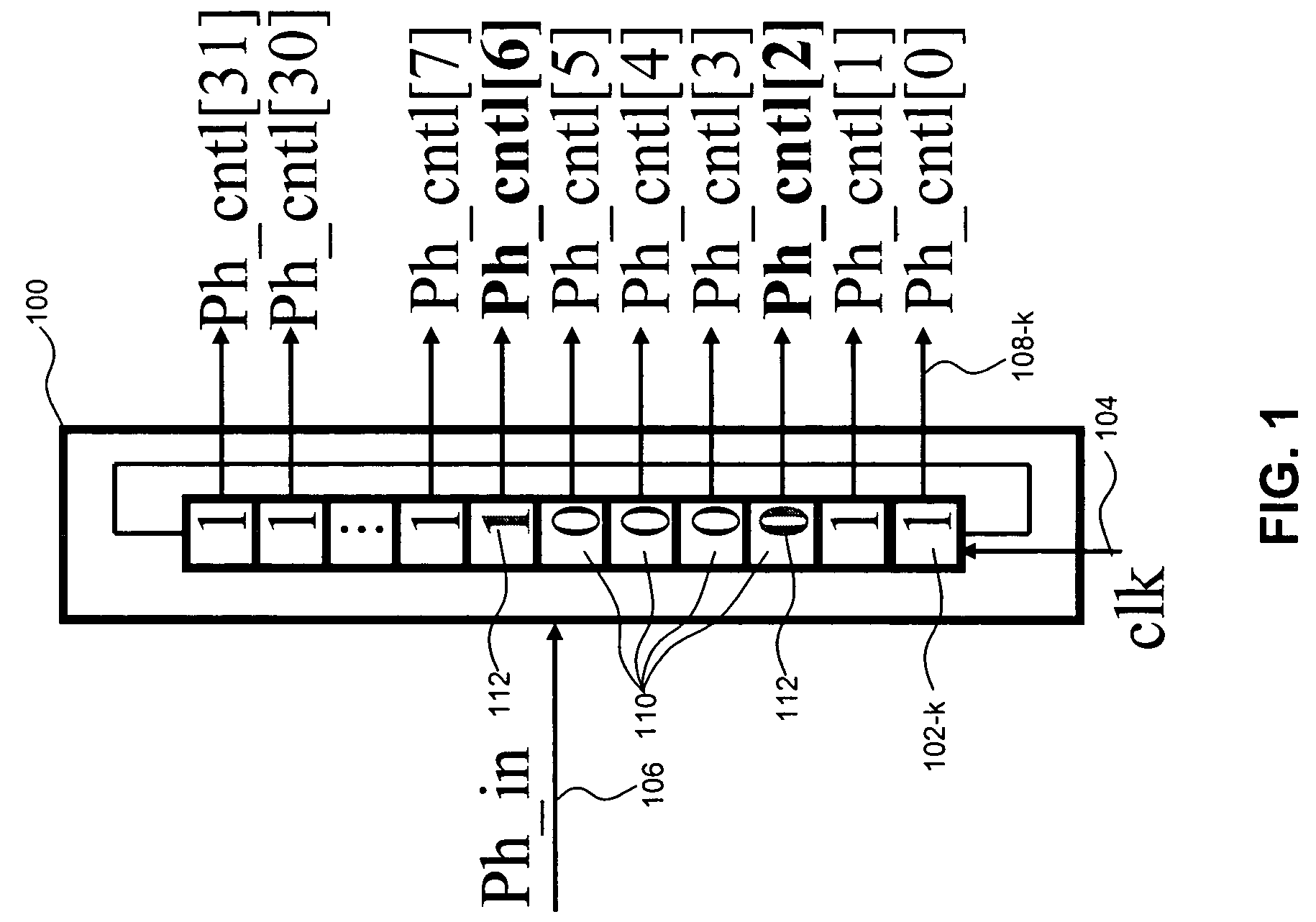

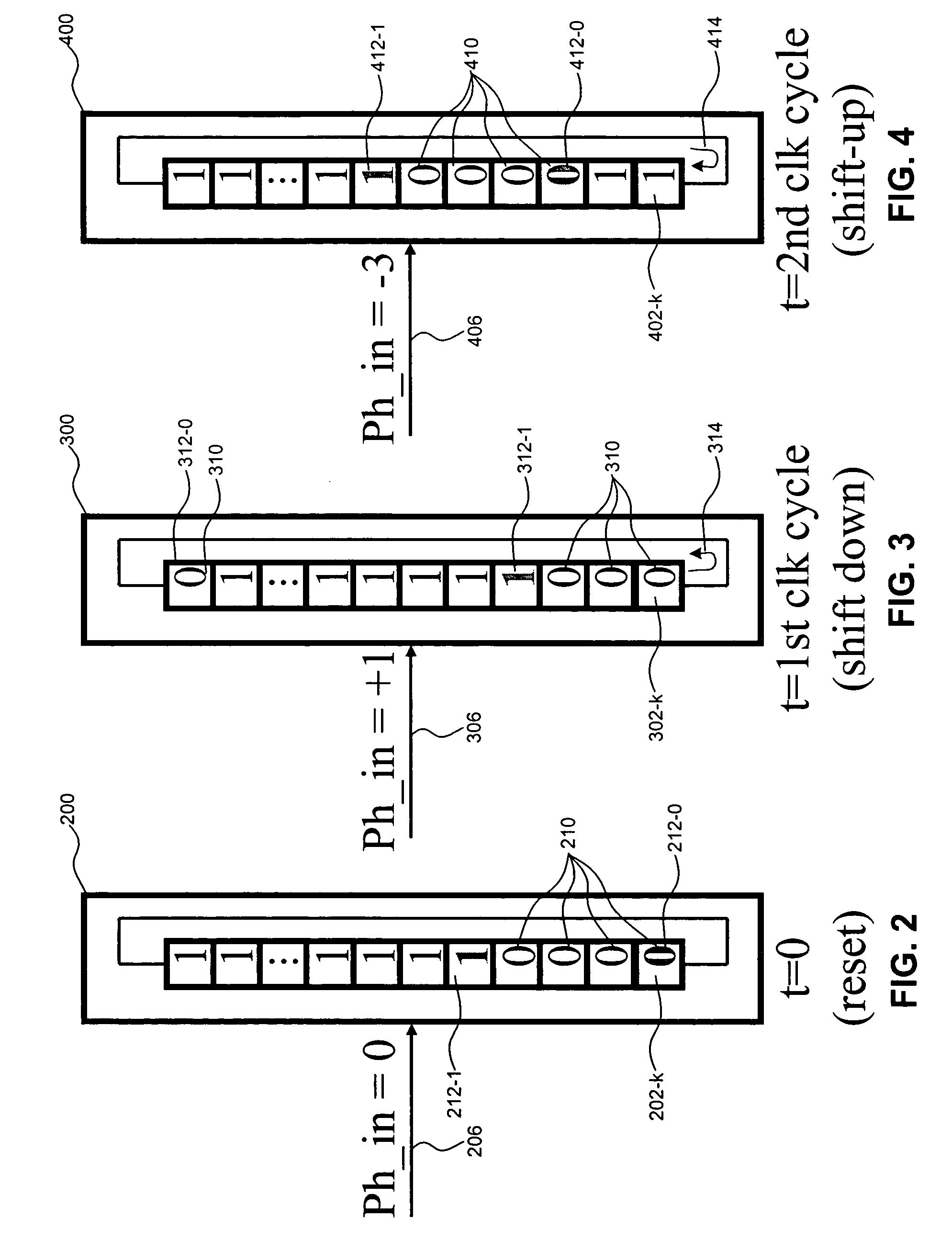

System for shifting data bits multiple times per clock cycle

A system and method are used to allow for phase rotator control signals to be produced that rotate bits in the signals more than one step per clock cycle. This can be done through the following operation. First and second data signals that include a plurality of data bits are stored. Rotation of data bits in the first data signal and subsequently data bits in the second data signal is controlled based on a phase control signal during each clock cycle. The first and second controlled data signals are interleaved to form first and second interleaved data signals. One of the first and second interleaved data signals is selected based on a portion of the phase control signal during a second half of the clock cycle. Finally, the selected data signal is transmitted as the phase control signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

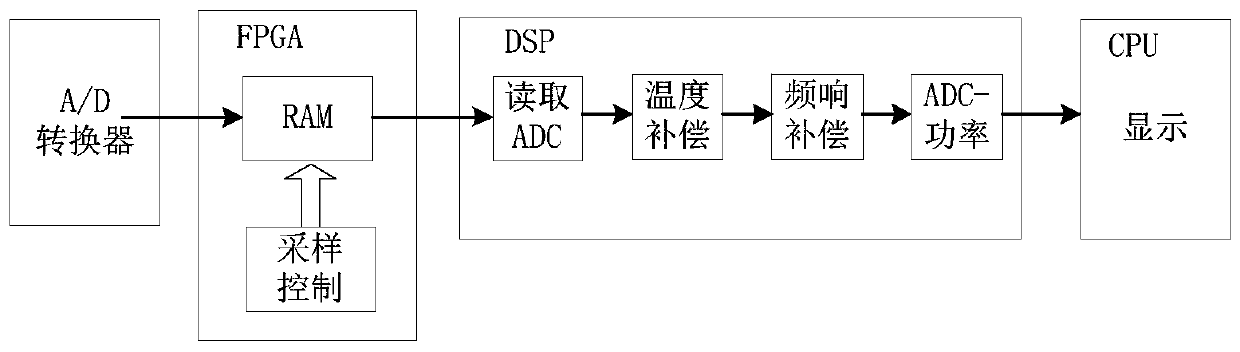

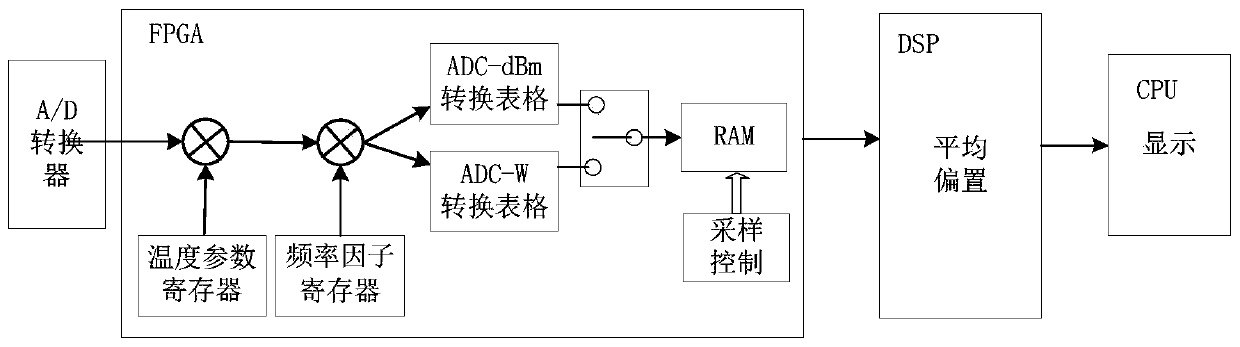

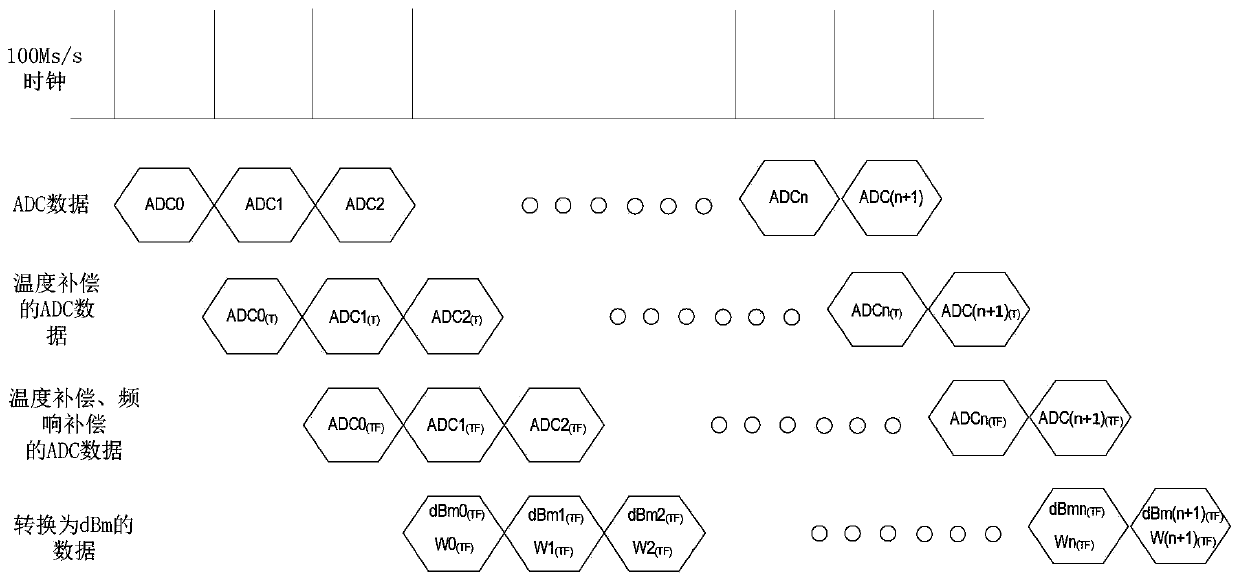

A method to increase the speed of peak power measurement

ActiveCN109030934BReduce processing timeElectric devicesPower measurement by digital techniqueConvertersGate array

The invention provides a method for improving peak power measurement speed, which comprises a peak power meter. The peak power meter comprises an A / D converter; the A / D converter is connected with a field programmable gate array; the field programmable gate array is internally provided with a temperature parameter register, a frequency factor register and a random access memory; the temperature register is connected with the frequency factor register; the frequency factor register is respectively connected with a first memory and a second memory; and both the first memory and the second memoryare respectively connected with a random access memory through a single-pole double-throw switch. According to the method for improving peak power measurement speed in the invention, the ADC is converted into power data with only a delay of 4 clock periods, and the time delay is 40ns. One sampling period mainly comprises sampling time of 1000 data points, reading time of a digital signal processor, simple calculation time of the digital signal processor, the reading time of a central processing unit, etc.; the total time is less than 1 ms; the efficiency is improved by more than 40 times compared with the existing method.

Owner:CHINA ELECTRONIS TECH INSTR CO LTD

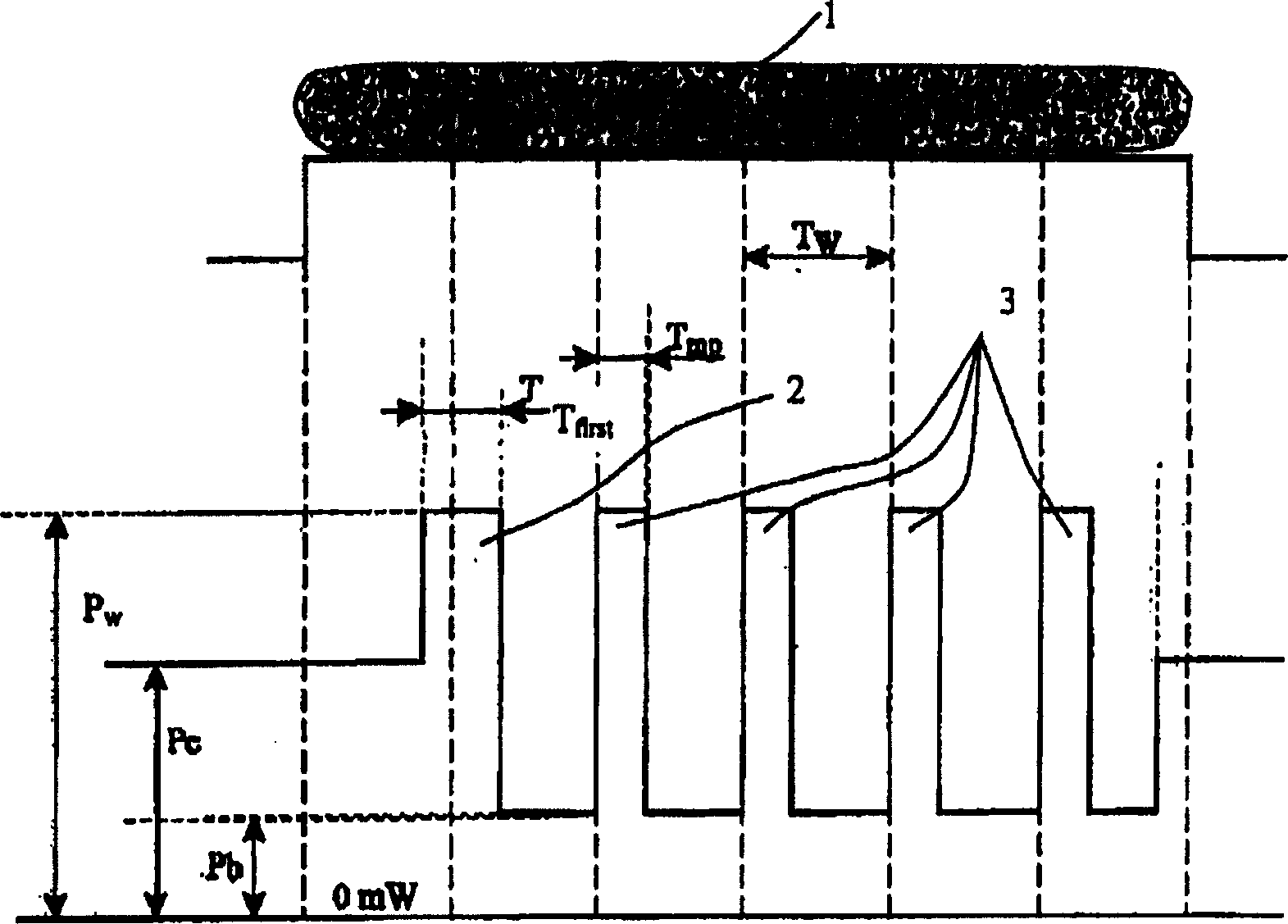

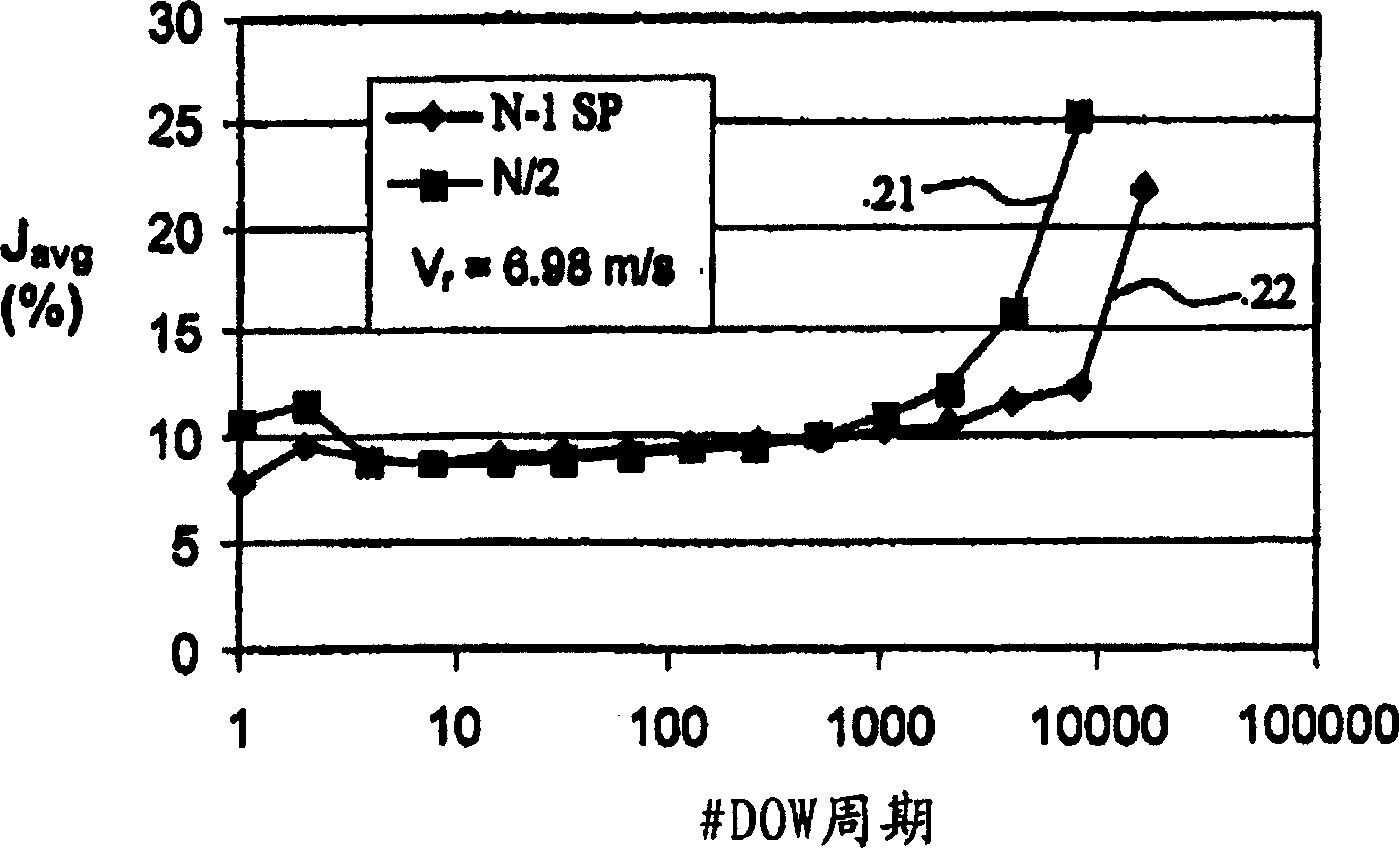

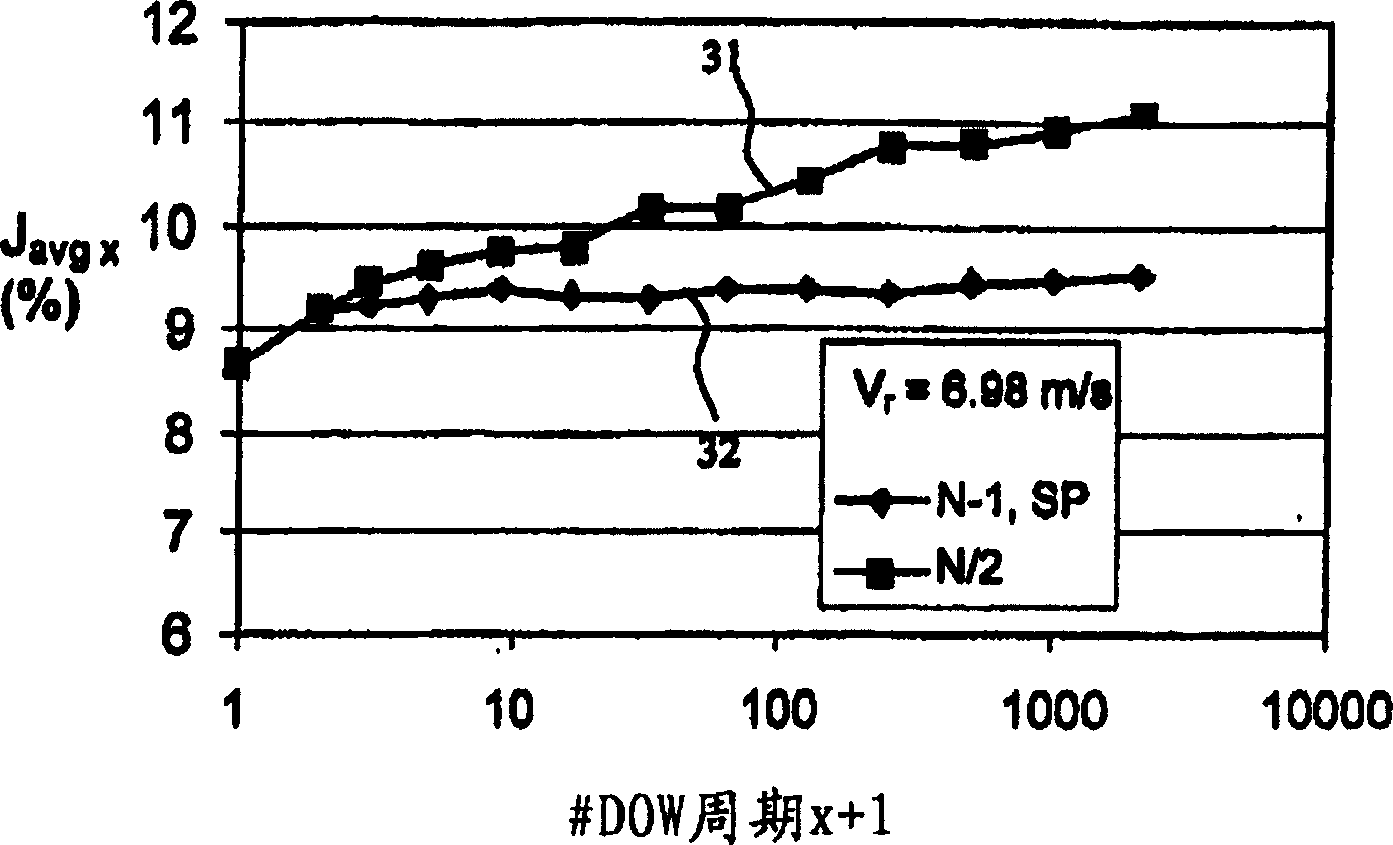

Method and device for recording marks in recording layer of an optical storage medium

The invention relates to a method and a recording device for recording marks (1) on a phase change type storage medium. Usually, an nT mark (1) is recorded by a sequence of n-1 or less write pulses. In slow cooling stacks, this will result in low quality markings. The invention proposes to increase the cooling period between multiple pulses (3) in the write pulse train by applying multiple pulses (3) with pulse duration Tmp<4ns and duty cycle Tmp / Tw, Where Tw is the reference clock cycle time and Tw<40ns. In this way, marks of very good quality are obtained even after a huge number of direct overwrite (DOW) cycles and over a wide range of recording power and recording speed (1).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV