Method for manufacturing inlaid structure

A manufacturing method and a technology of a mosaic structure, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., to achieve the effect of saving process steps and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0031] Figure 6 It is a flow chart of the first embodiment of the manufacturing method of the damascene structure of the present invention.

[0032] Such as Figure 6 As shown, firstly, a semiconductor substrate is provided, and a metal wire layer is formed in the semiconductor substrate ( S100 ). The semiconductor substrate can be polycrystalline silicon, monocrystalline silicon, amorphous silicon, silicon-on-insulator (SOI), gallium arsenide, silicon-germanium compound, etc., and the metal wire layer material can be copper, aluminum, titanium, nitride One or a combination of titanium and tungsten, the metal wire layer in this embodiment is copper.

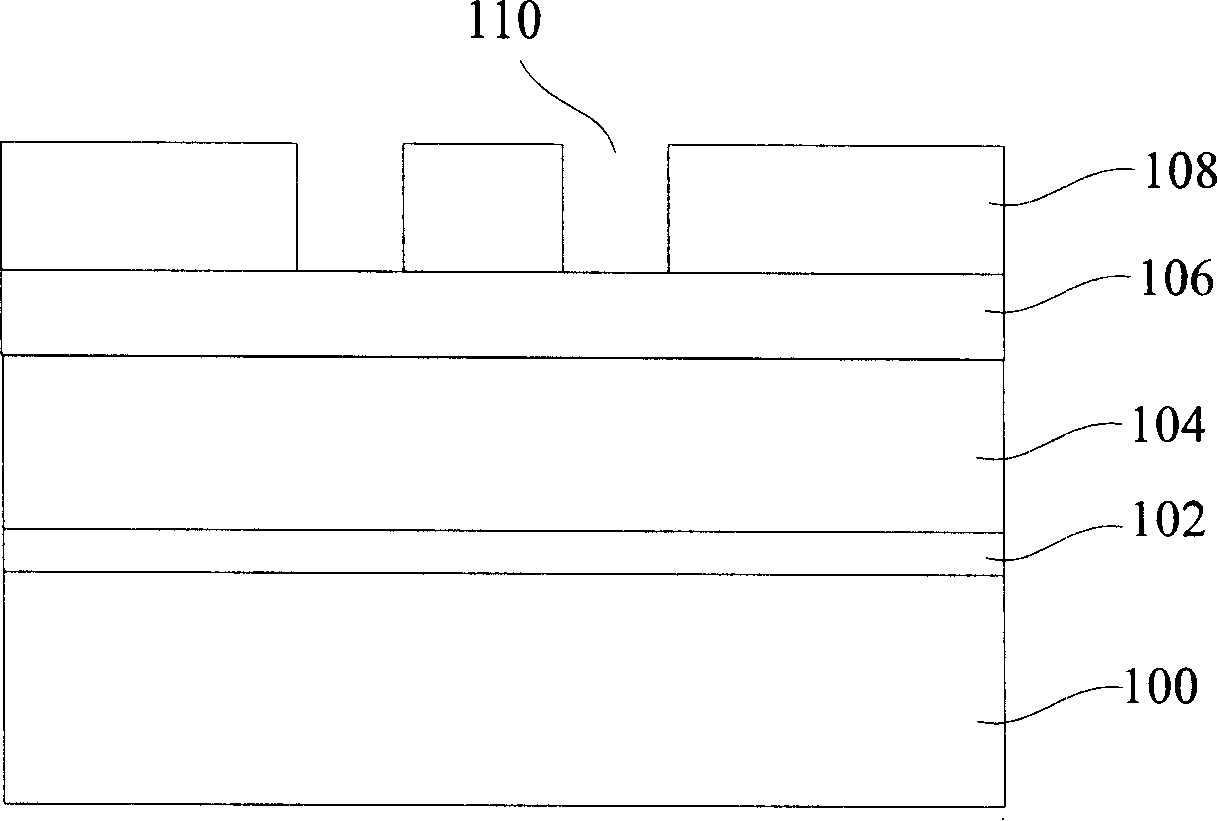

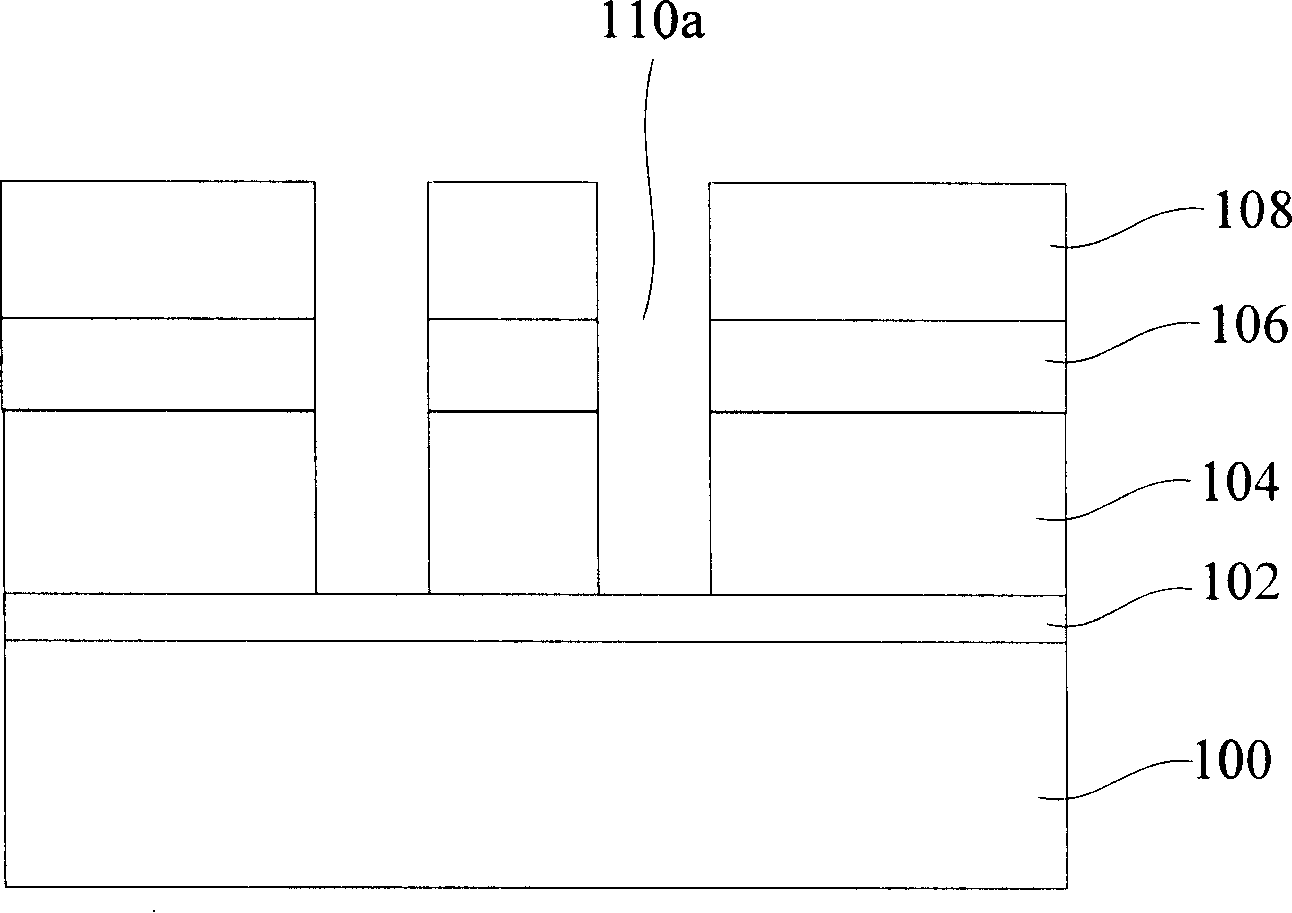

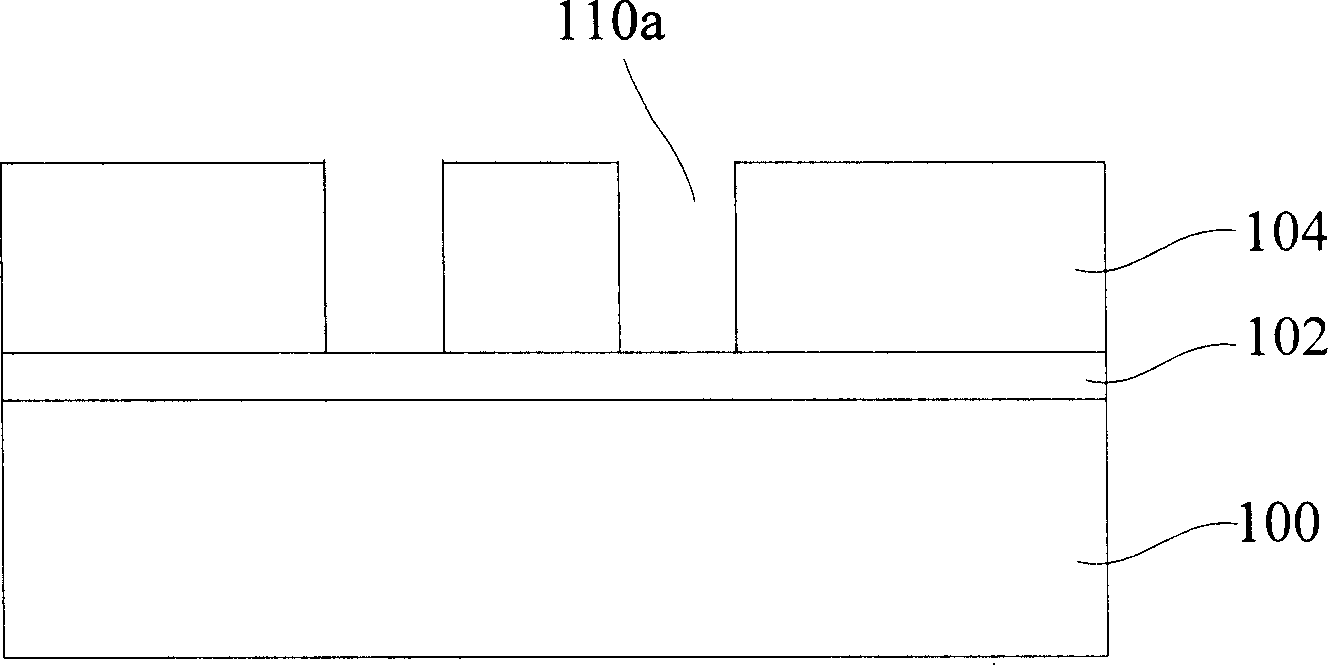

[0033] An etching stop layer is formed on the semiconductor substrate, a dielectr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More