Circuit design standard and implementation method for 3-D solid structure phase change memory chip

A phase-change memory, three-dimensional technology, applied in static memory, read-only memory, digital memory information, etc., can solve problems that are not conducive to low voltage and low power consumption of chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] For further clarifying substantive characteristics of the present invention and remarkable progress, describe the present invention by embodiment below:

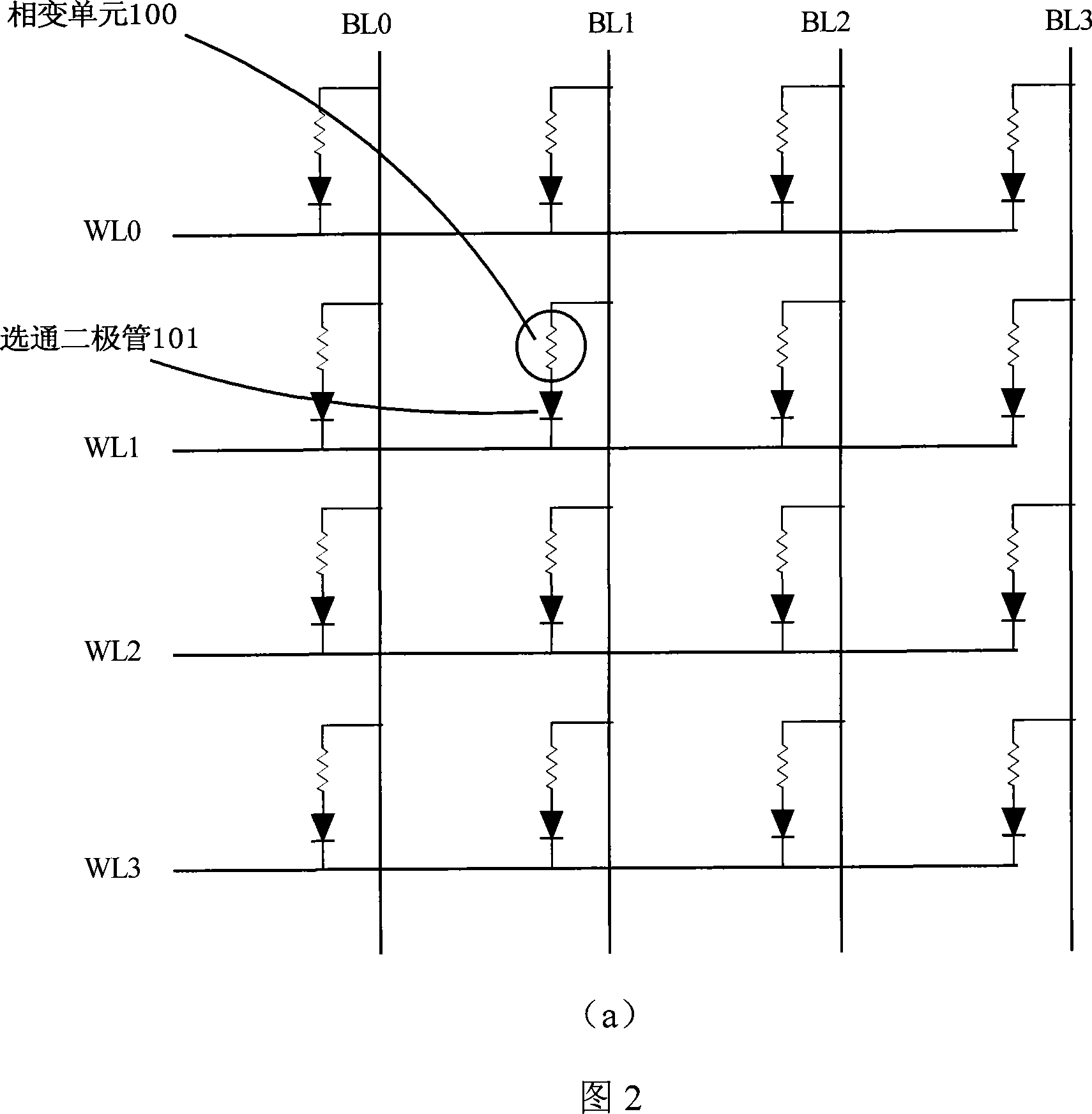

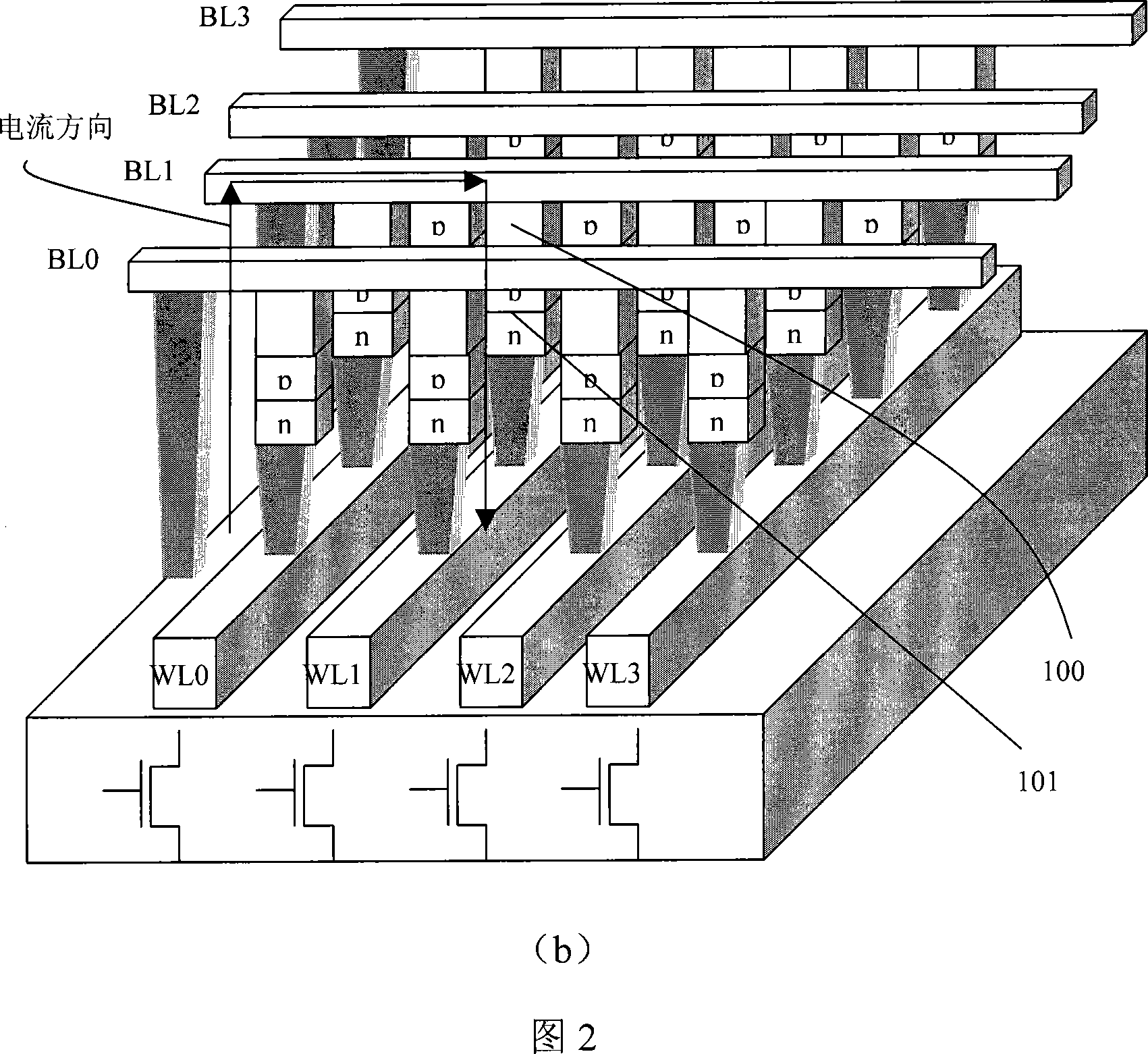

[0028]Fig. 2a is a pattern of a 4×4 array of a phase-change memory 1R1D (a diode D is connected to a phase-change memory unit R). It should be understood that the present invention is not limited thereto. 100 in the figure is a phase-change memory unit, and 101 is a gate diode. When the read / write operation is not performed on 100 , the bit line BL1 and the word line WL1 maintain a potential that can ensure that the gate diode 101 is turned off. For example, WL1 may be logic “1” and BL1 may be logic “0”; or BL1 may be in a floating state; or BL1 may be an intermediate level value. When 100 is to be read and written, WL1 is reduced to logic "0", BL1 inputs current or a certain voltage value is given, so that 101 is turned on, ensuring that a certain current value flows through the phase-change memory unit. When a cu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More