Semiconductor encapsulation construction

A semiconductor and structure technology, applied in the field of semiconductor packaging structure, can solve the problems of substrate redesign, inconvenience, spilled glue contaminating external pads, etc., and achieves the effect of avoiding glue spillage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 3 Embodiment

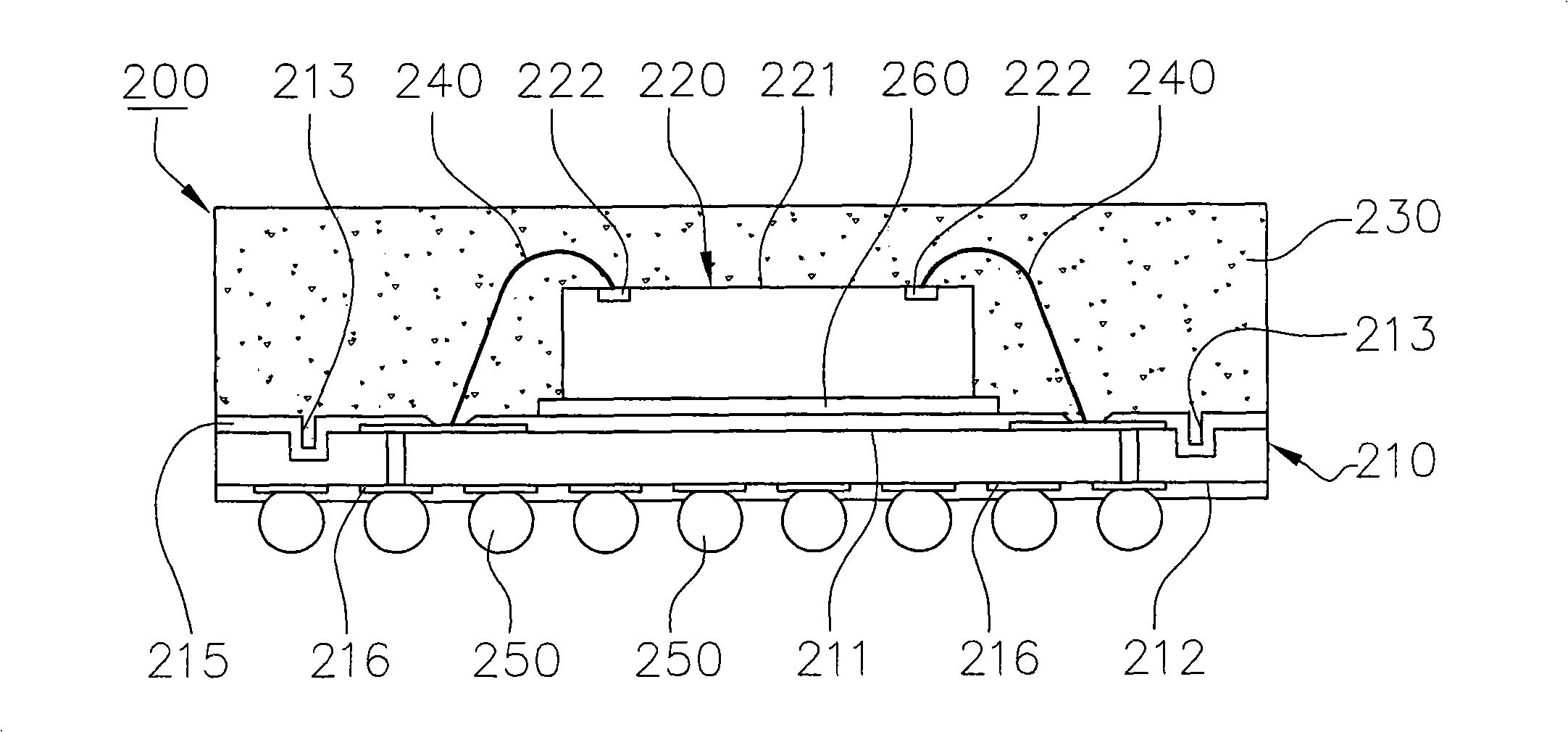

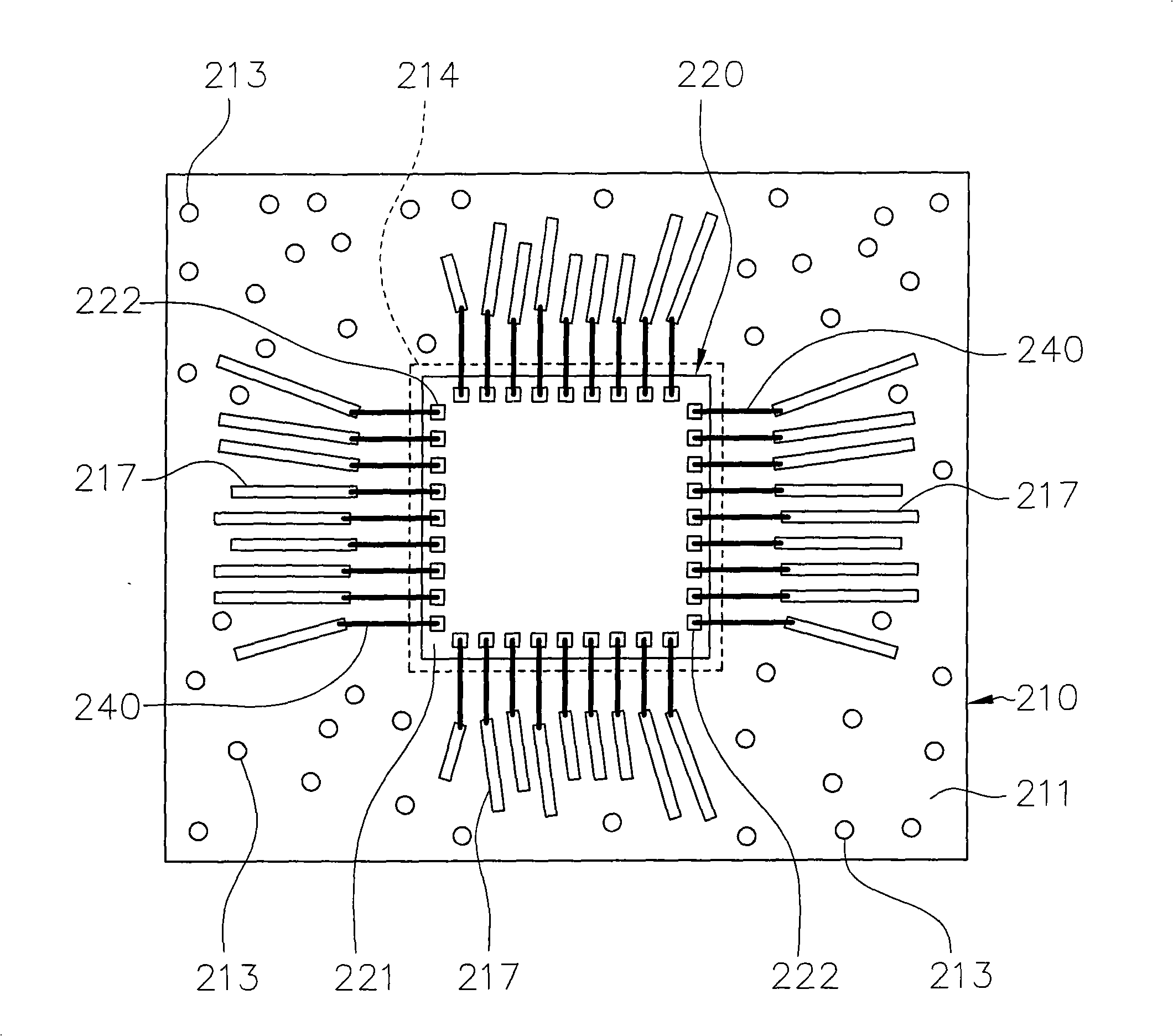

[0080] see Figure 6 Shown is a schematic cross-sectional view of another semiconductor package structure according to the third embodiment of the present invention. Another semiconductor package structure is disclosed in the third embodiment of the present invention. The semiconductor package structure 400 mainly includes a substrate 410 , a chip 420 and an encapsulant 430 .

[0081] The above-mentioned substrate 410 has an upper surface 411 and a plurality of pits 413 formed on the upper surface 411. The upper surface 411 defines a wafer setting area (not shown in the figure), and the pits 413 are located in the The circuit blank area outside the wafer placement area does not penetrate the substrate 410 . The substrate 410 may further include a solder resist layer 414 formed on the upper surface 411 of the substrate 410 and having a plurality of slots 415 to partially expose the upper surface 411 . In this embodiment, the recesses 413 are blind holes that can be located i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More