Semiconductor test management system

A test management and semiconductor technology, applied in the direction of single semiconductor device testing, electronic circuit testing, measuring electricity, etc., can solve the problems of error-prone test efficiency, many steps, complicated procedures, etc., so as to improve the detection accuracy and simplify the detection procedure. , the effect of improving the detection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The semiconductor test management system of the present invention will be further described in detail below in conjunction with the accompanying drawings.

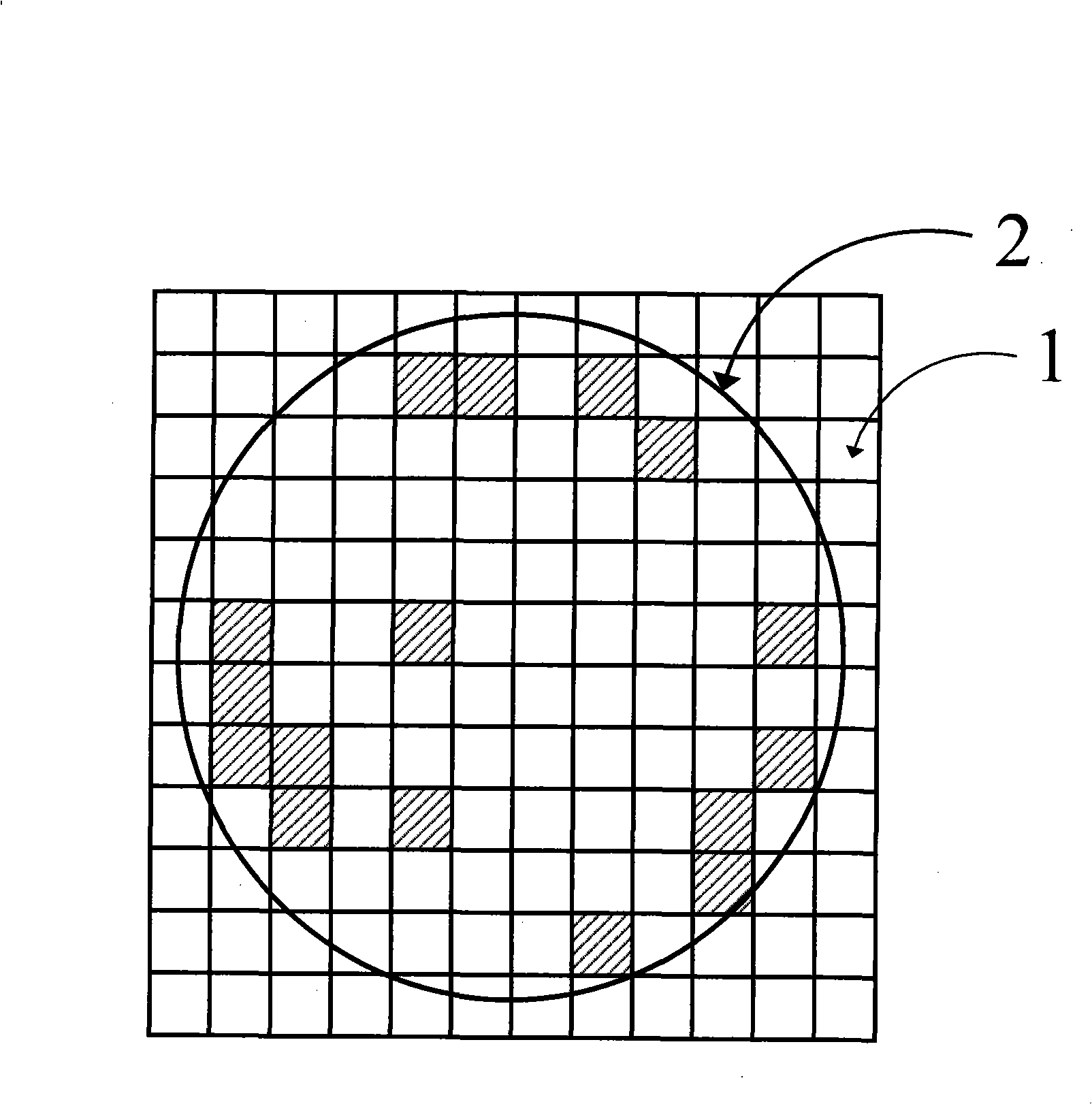

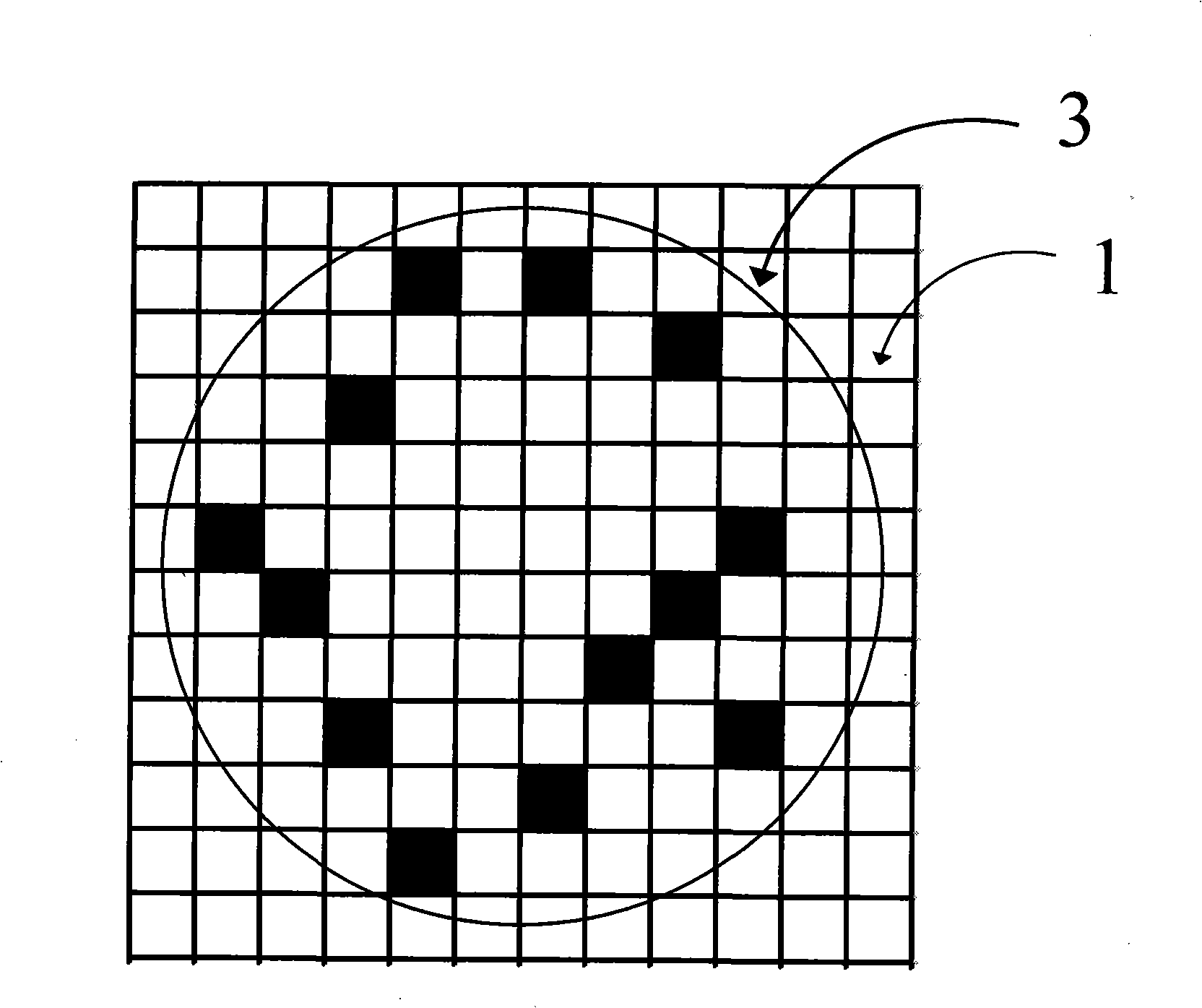

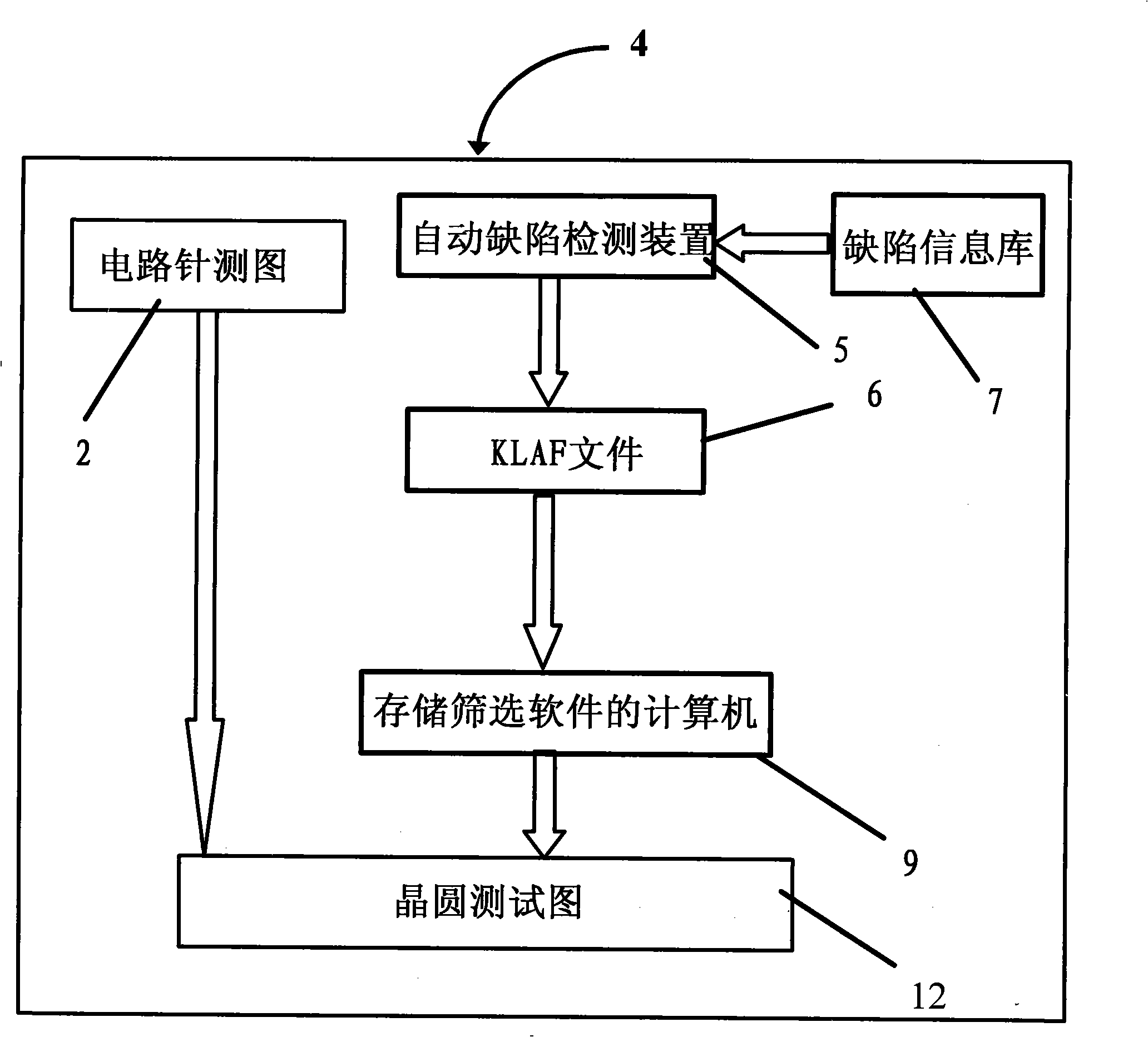

[0023] like Figure 4 As shown, the semiconductor test management system 4 of the present invention includes: a circuit needle test figure 2 , the circuit pin test figure 2 It is a diagram of the results of the wafer probe card using the probe to detect the electrical characteristics of each die on the wafer. Among them, the unqualified die will be tested on the circuit needle. figure 2 Superscript on the mark, such as figure 1 As shown, the shaded area is a disqualified grain, and the unqualified grain marked with the mark will be eliminated, so as not to increase the manufacturing cost; an automatic defect detection device 5 (Auto Inspection Tool, AVI tool), wherein the automatic detection device 5 is The defect detection device produced by Cametak can scan and detect all the defects of the wafer at one time a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More