Capacitor embedded semi-conductor package substrate construction and preparation thereof

A technology for packaging substrates and capacitor components, which is used in the manufacture of semiconductor/solid-state devices, assembling printed circuits with electrical components, and electrical components. Precise, material-saving effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

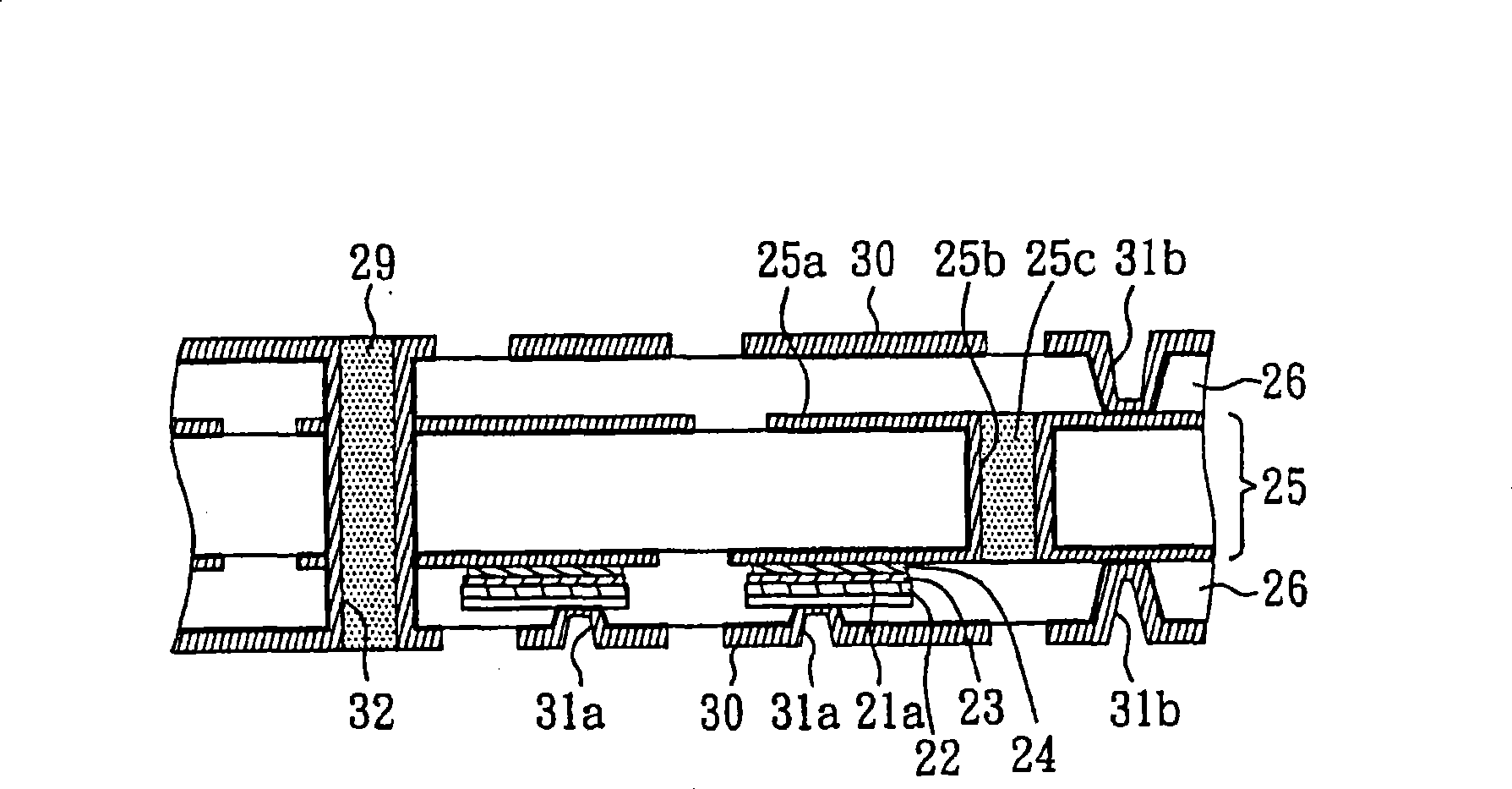

[0047] Please refer to figure 2 , is a cross-sectional view of the capacitive element embedded in the semiconductor package substrate structure of the present invention. like figure 2 As shown, an inner circuit board 25 , a dielectric layer 26 , and an outer circuit layer 30 are included. There is an inner layer circuit layer 25a in the inner layer circuit board 25, and the inner layer circuit layer 25a is a copper layer, and the inner layer circuit board 25 may also include an inner plating via hole 25b, the inner plating via hole 25b further includes an insulating resin 25c, and the material of the inner wall is copper, so as to be connected to the inner circuit layer 25a on both sides of the inner circuit board 25 . The dielectric layer 26 is disposed on both sides of the inner circuit board 25, and the materials used may be ABF (Ajinomoto Build-up Film), BCB (Benzocyclo-buthene), LCP (Liquid Crystal Polymer), PI (Poly-imide ), PPE (Poly (phenylene ether)), PTFE (Poly ...

Embodiment 2

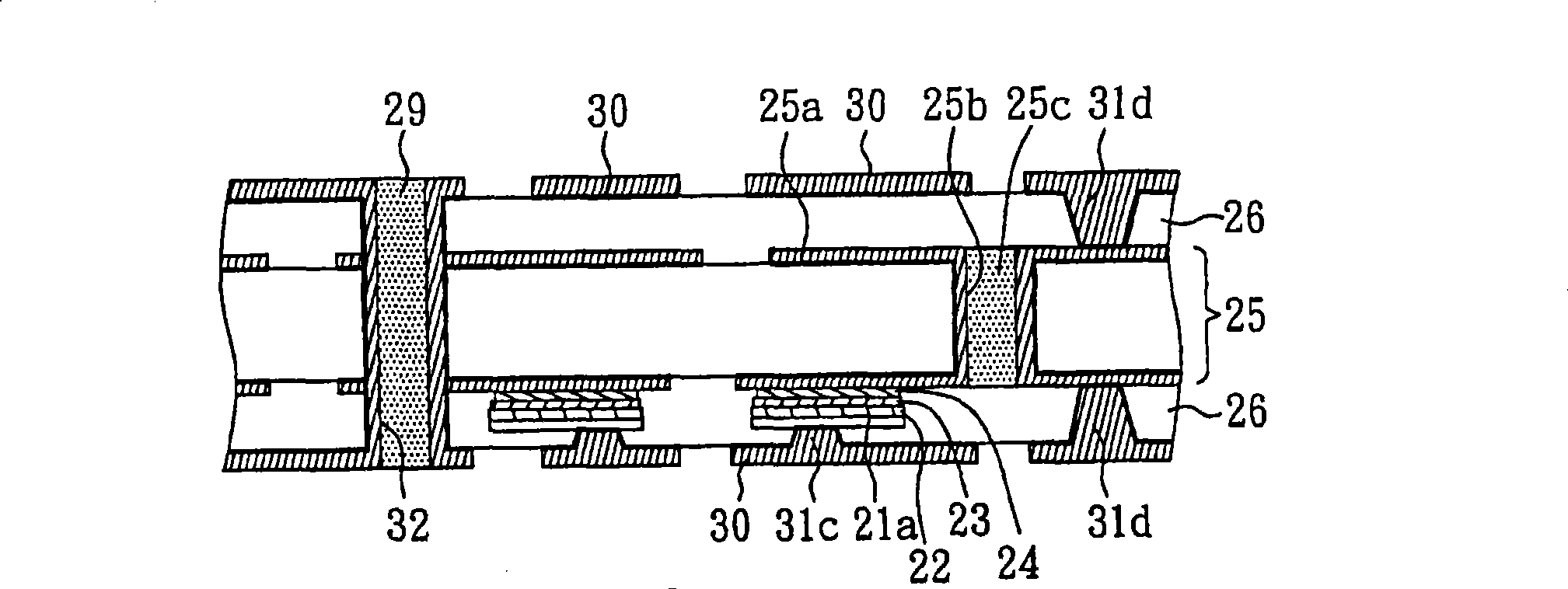

[0050] Please refer to image 3 , is a cross-sectional view of the capacitive element embedded in the semiconductor package substrate structure of the present invention. like image 3 As shown, its structure is substantially the same as that of Embodiment 2, but the difference is that the first conductive blind hole 31c and the second conductive blind hole 31d of this embodiment are filled with material, that is, filled with copper metal.

Embodiment 3

[0052] The materials used in this embodiment can be the same as those in Embodiment 1. This embodiment mainly lies in the production method, please refer to Figures 4A to 4H ', is a cross-sectional view of a method of manufacturing a semiconductor package substrate with an embedded selective capacitive element.

[0053] like Figure 4A As shown, firstly, a metal carrier 21 is provided, the material used in the metal carrier 21 can be a copper plate, and a plurality of capacitive materials 22 are selectively formed on its surface by coating or printing, and then these capacitive materials 22 An electrode layer 23 is formed on the surface in the same way, and a capacitor element can be formed after high-temperature sintering.

[0054] Next, if Figure 4B As shown, a fusible metal adhesive layer 24 is formed on the electrode layer 23 by screen printing. Another example Figure 4C As shown, the capacitive element is soldered back to the inner circuit layer 25 a of the inner ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More