Semiconductor device and manufacturing method of the same

By arranging a high-concentration n-type impurity region on the semiconductor substrate of J-FET as part of the current path, the problems of IDSS deviation and increased noise in J-FET are solved, and the uniformity of the current path and performance improvement are achieved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

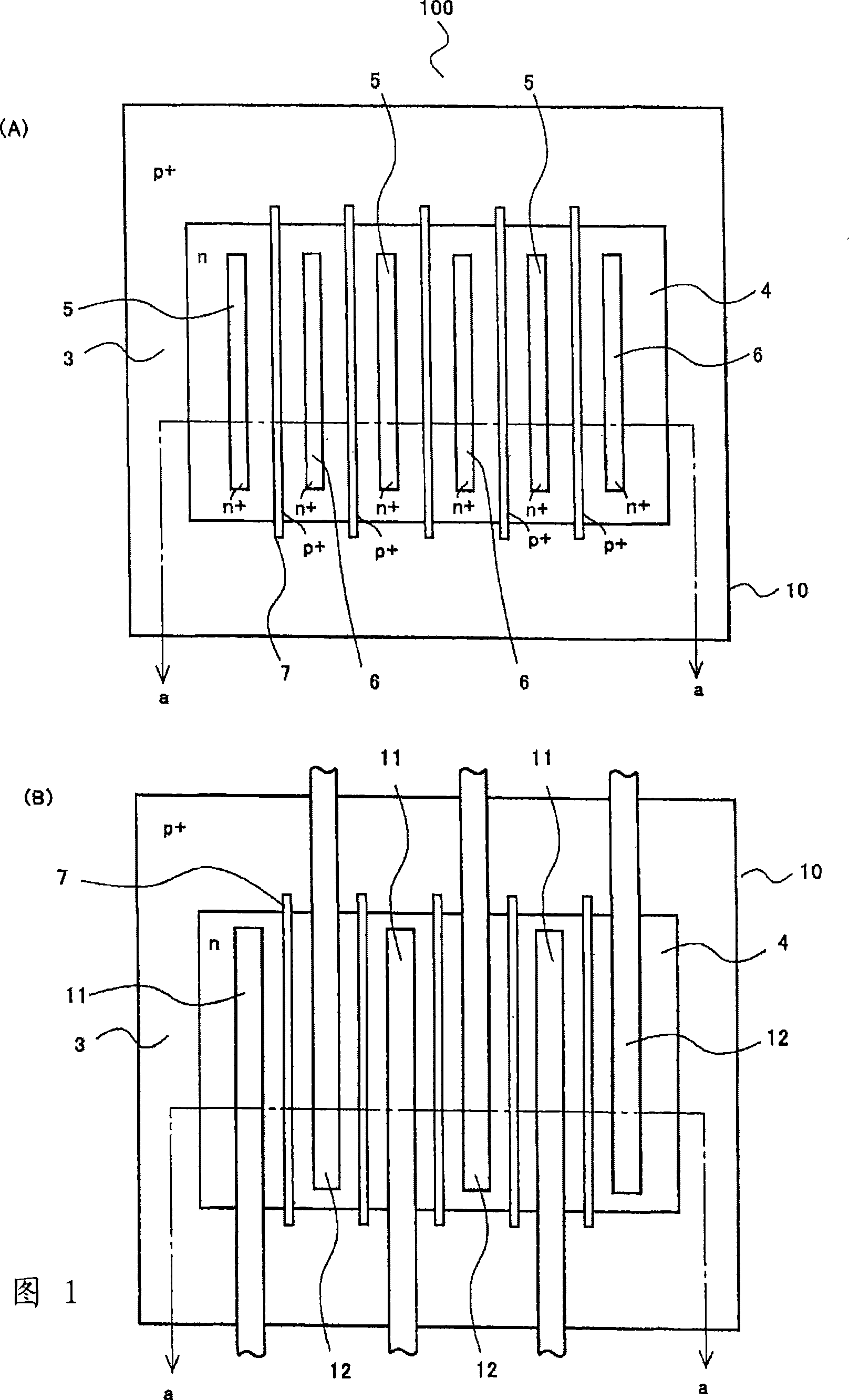

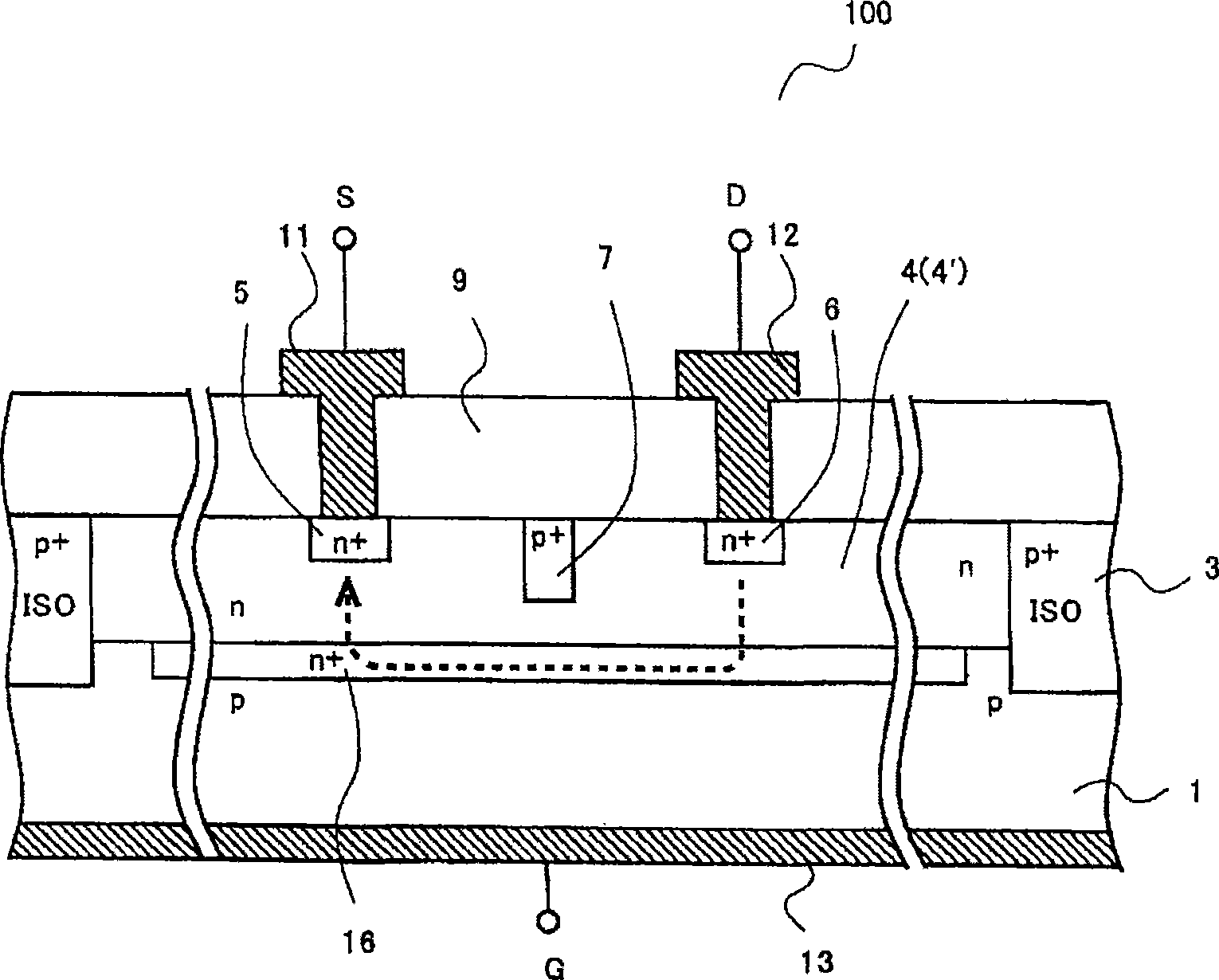

[0044] The following takes the junction field effect transistor (J-FET) as an example and refers to Figure 1 to Figure 9 Examples of the present invention will be described.

[0045] 1 is a plan view showing a part of J-FET 100, FIG. 1(A) is a view omitting electrode layers, and FIG. 1(B) is a view with electrode layers arranged.

[0046] The J-FET 100 of this embodiment is constituted to include: a conductivity type semiconductor substrate 1 , a channel region 4 , a gate region 7 , a source region 5 , a drain region 6 and a reverse conductivity type (n-type) impurity region 16 .

[0047]Referring to FIG. 1(A), it shows that a J-FET 100 is provided with a channel region 4 divided by a separation region 3 on a p-type semiconductor substrate 1 that constitutes a chip and becomes a back gate region, but the channel region 4 may also be is multiple.

[0048] The separation region 3 is a high-concentration p-type impurity region, as shown in the sectional view ( figure 2 ), wh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More