Chamber lining

A chamber and lining technology, applied in the field of microelectronics, can solve the problems of inability to effectively protect the pumping chamber, limit the uniformity of the flow field on the surface of the silicon wafer, and narrow the protection range, so as to improve the processing/processing quality, Large protection range and the effect of avoiding pollution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to enable those skilled in the art to better understand the technical solution of the present invention, the lining of the chamber provided by the present invention will be described in detail below with reference to the accompanying drawings.

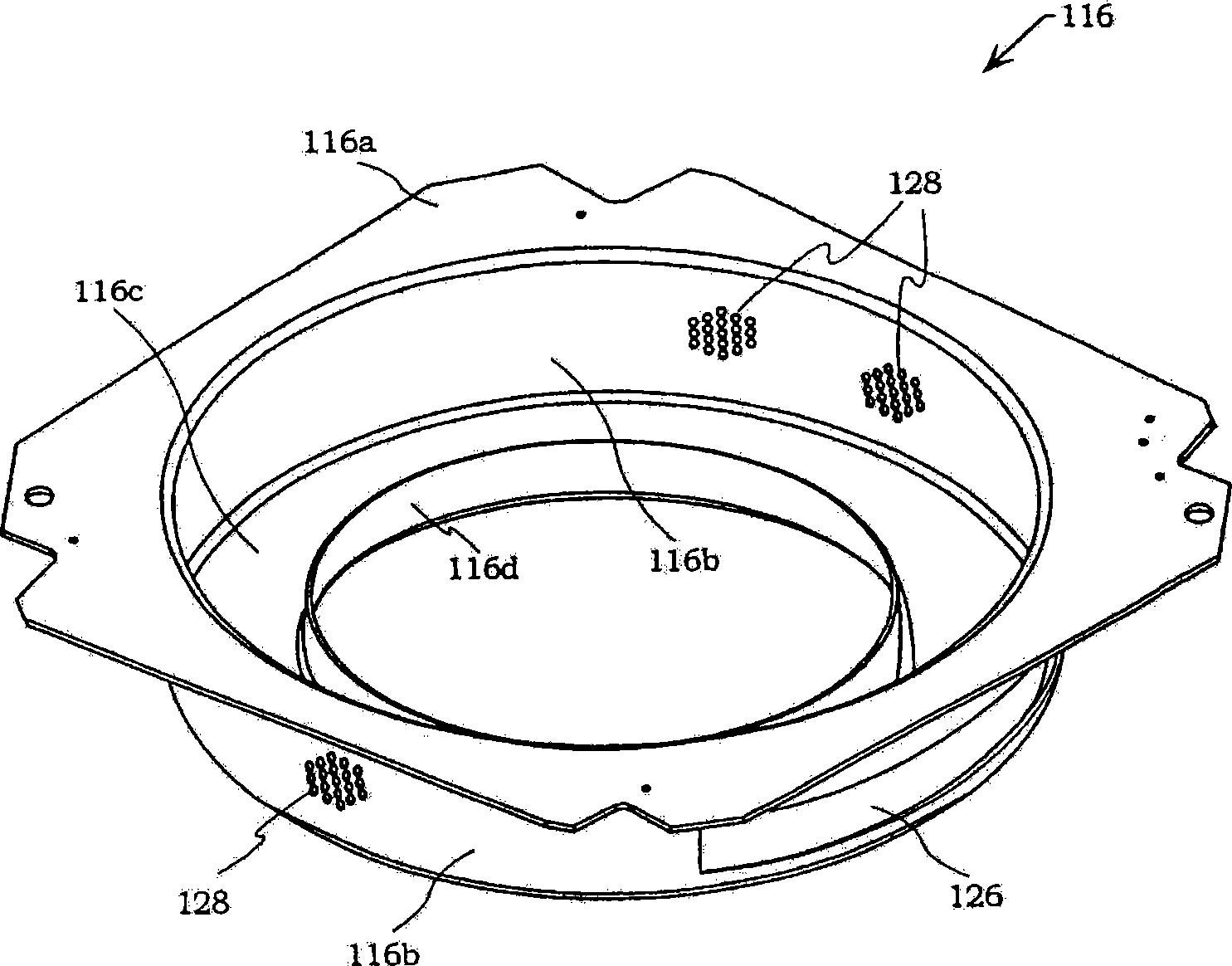

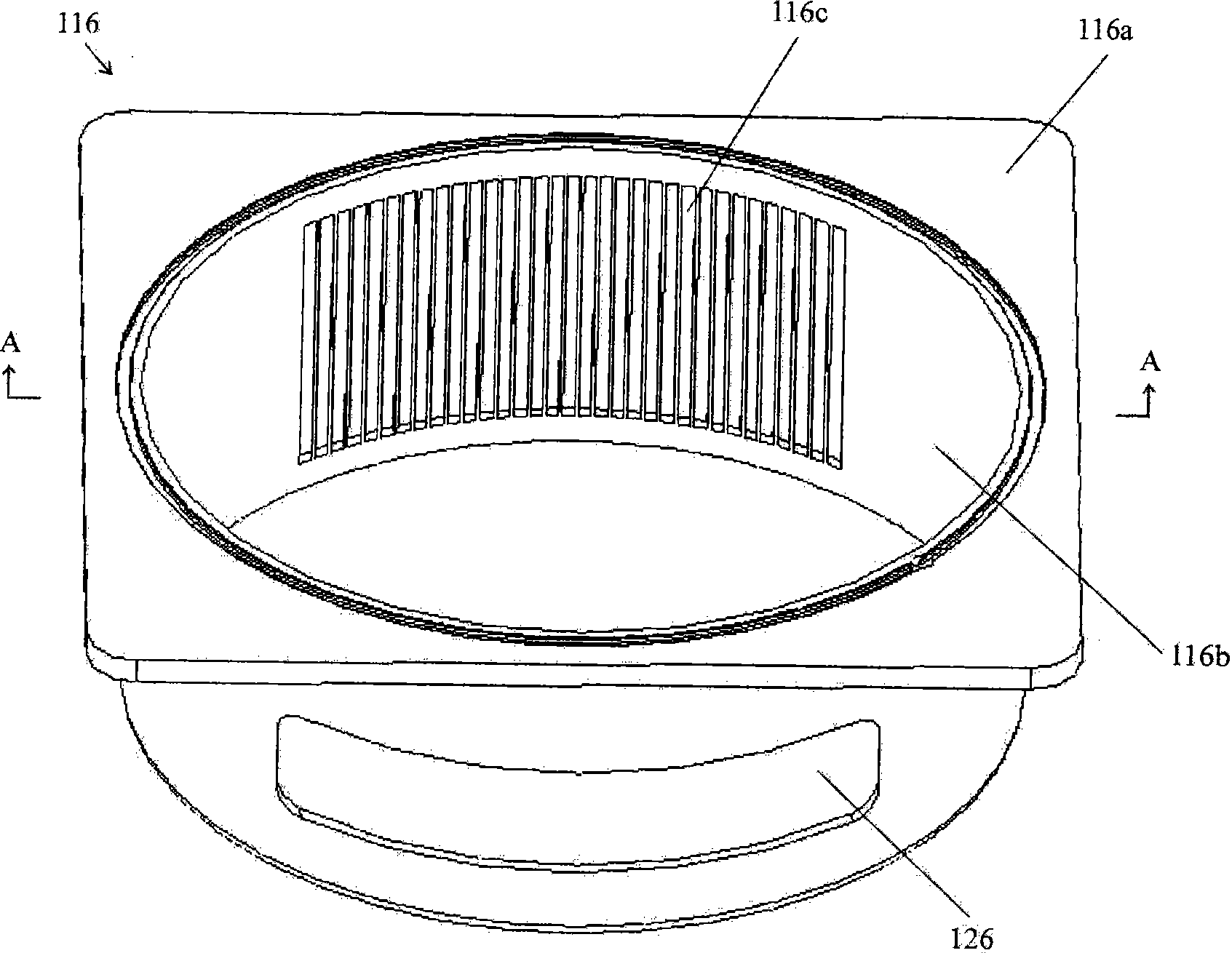

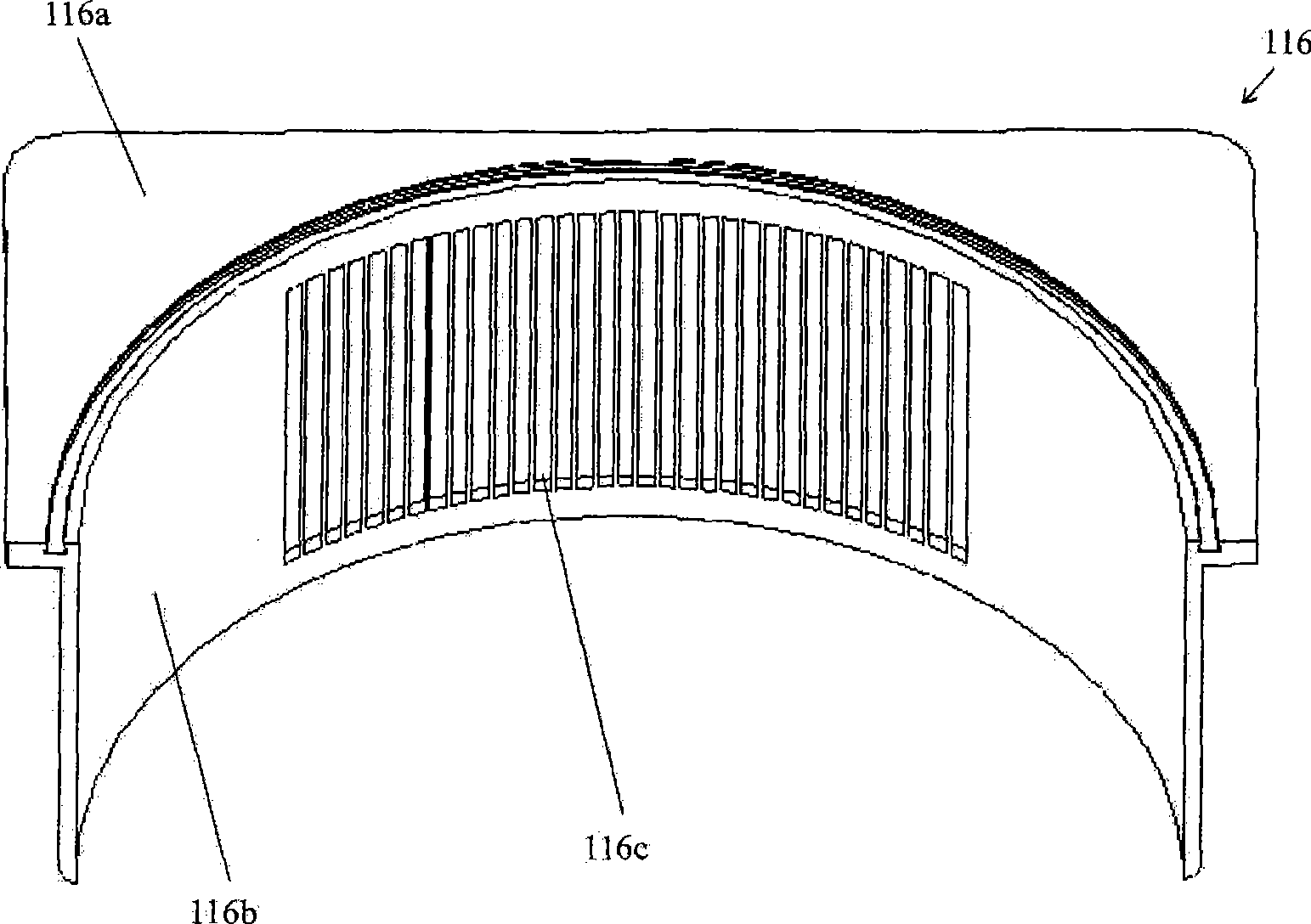

[0031] Please also see figure 2 and image 3 The liner 116 of the chamber provided by the first embodiment of the present invention includes a cylindrical outer wall 116b, an outer flange 116a extending outward from the upper edge of the outer wall 116b, a film delivery port 126 provided on the outer wall 116b, and A shielding hole 116c is opened at a position opposite to the film transfer port 126 on the outer wall 116b.

[0032] Wherein, the wafer transfer opening 126 is used as an entrance / exit for semiconductor devices such as wafers to enter / exit the processing chamber, and is arranged at a lower position on the outer side wall 116b.

[0033] The outer flange 116a is generally perpendicular to the outer sidewall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More