Time-delay reset control circuit and method

A delay reset and control circuit technology, applied in data reset device, hardware monitoring, data processing power supply, etc., can solve problems such as weak anti-interference ability, important data destruction in electric energy meter, CPU reset, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

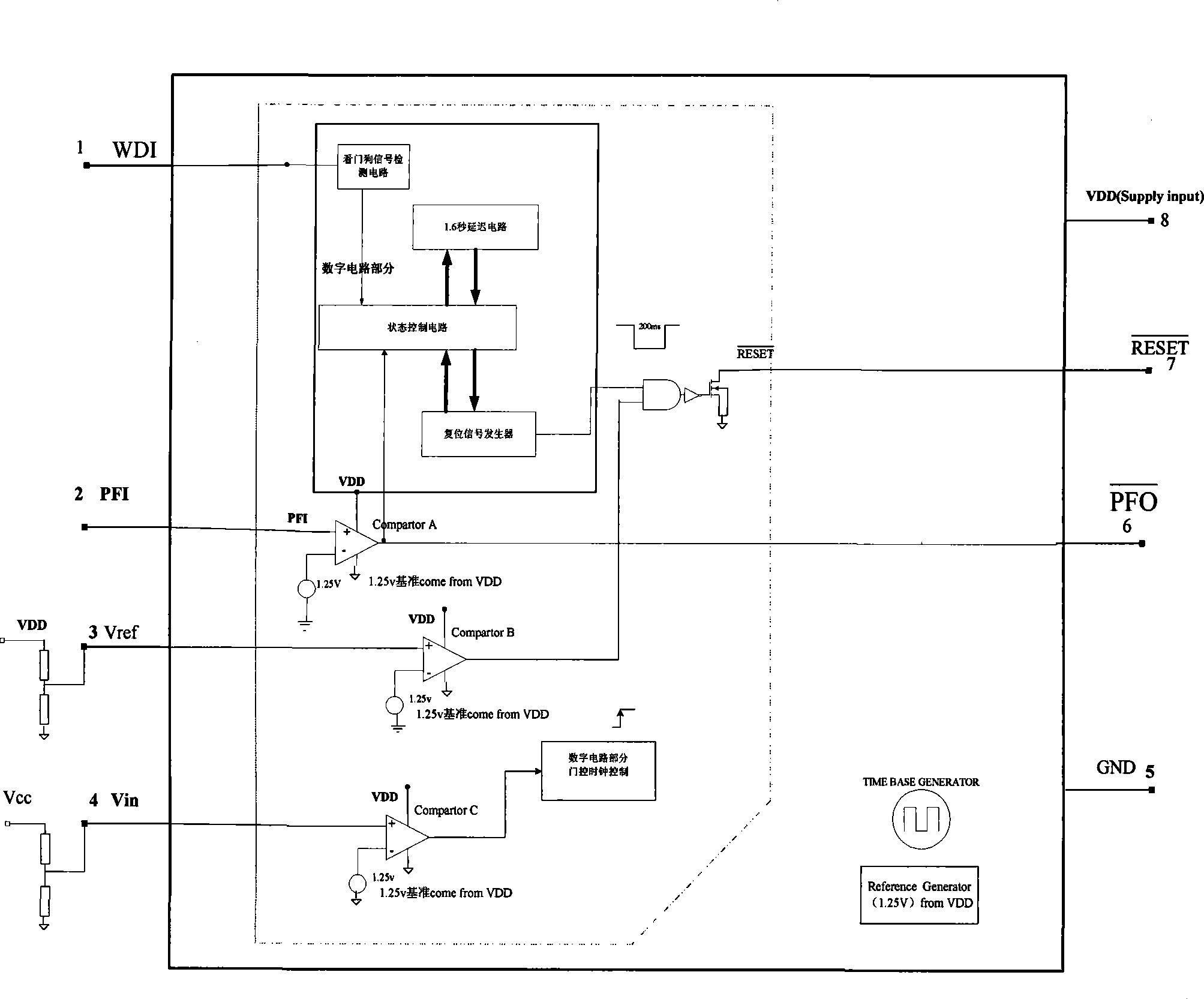

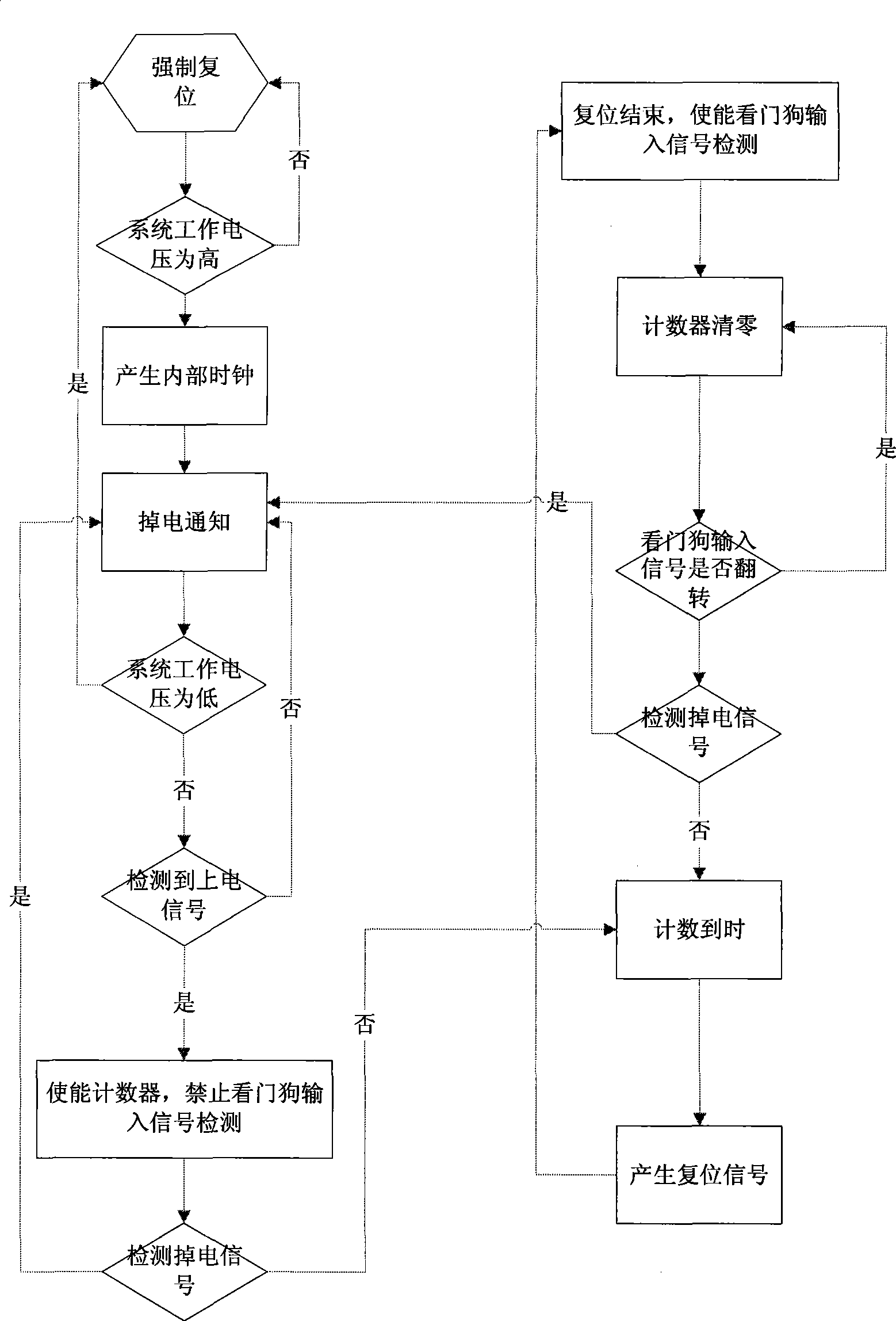

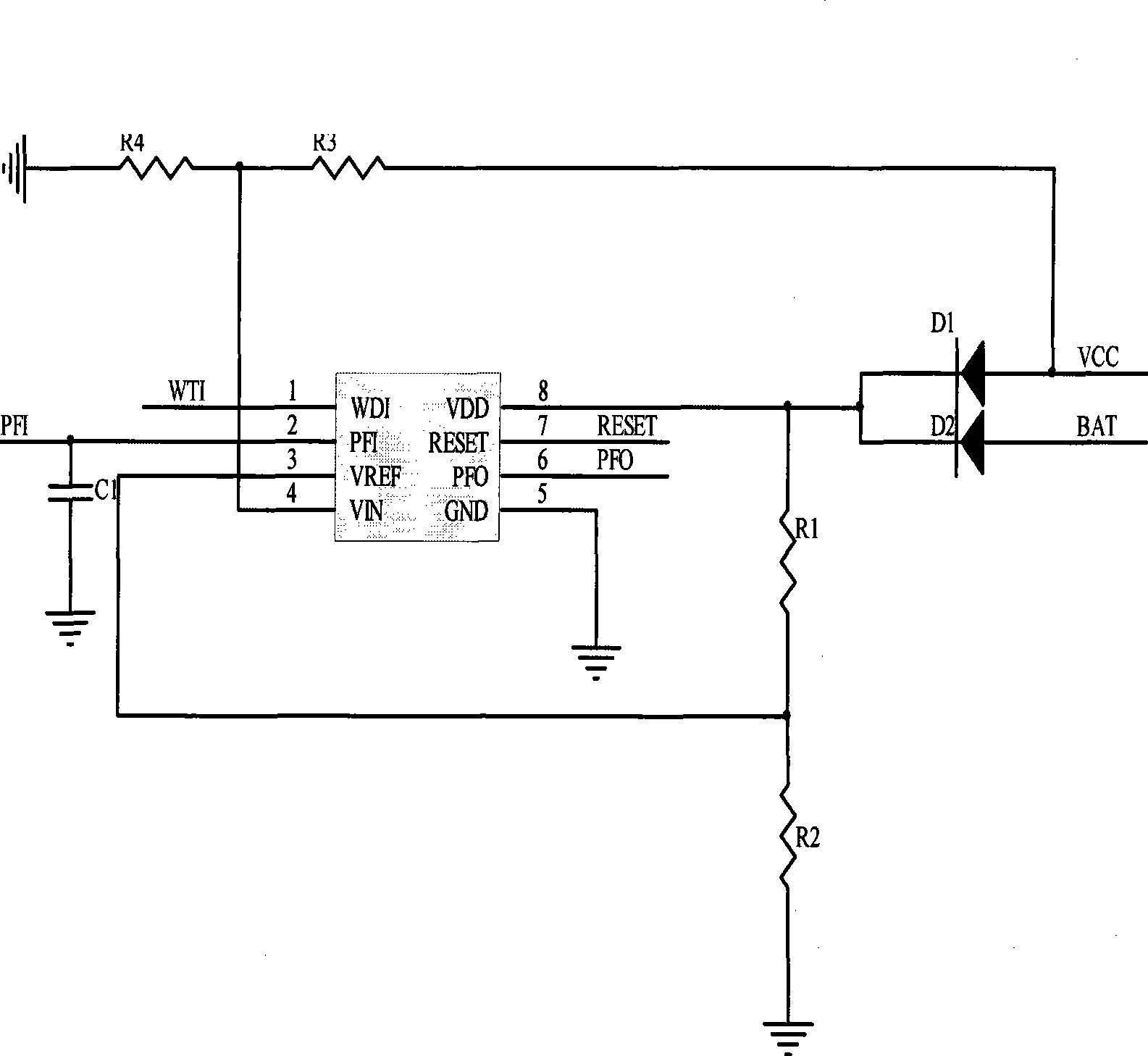

[0029] Such as figure 1 As shown, the delay reset control circuit disclosed in this embodiment is characterized in that it includes: a clock signal generation circuit, a watchdog signal detection circuit, a state control circuit, a timing delay circuit, a reset control circuit, a comparator A, a comparator B. AND gate, comparator C and gate control circuit.

[0030] The clock signal generation circuit oscillates to generate a pulse signal, which is input to the counter of the given timing delay circuit. The input terminal of the watchdog signal detection circuit is connected to the CPU, and the output is connected to the state control circuit, which is used to detect the watchdog input signal WDI, and after processing, send the feeding dog signal (the signal after detecting the inversion of the watchdog input signal) to the state Co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More