Amplifier

A technology of amplifiers and operational amplifiers, applied in differential amplifiers, DC-coupled DC amplifiers, improved amplifiers to reduce temperature/power supply voltage changes, etc., can solve problems such as affecting the use of equipment, burning speakers or earphones, and unpleasant audiences, etc., to achieve Good isolation, low power consumption and cost, good sound effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

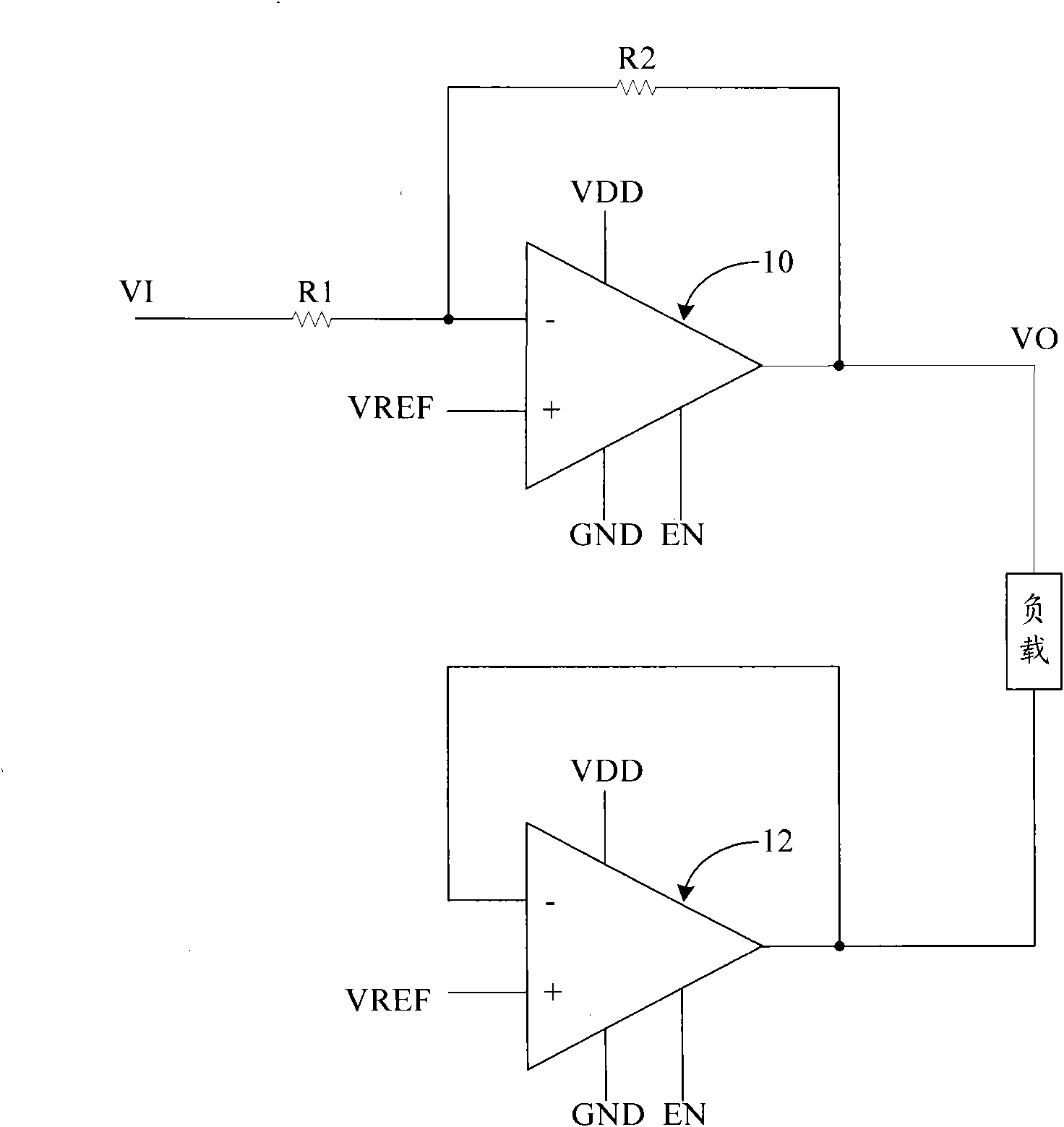

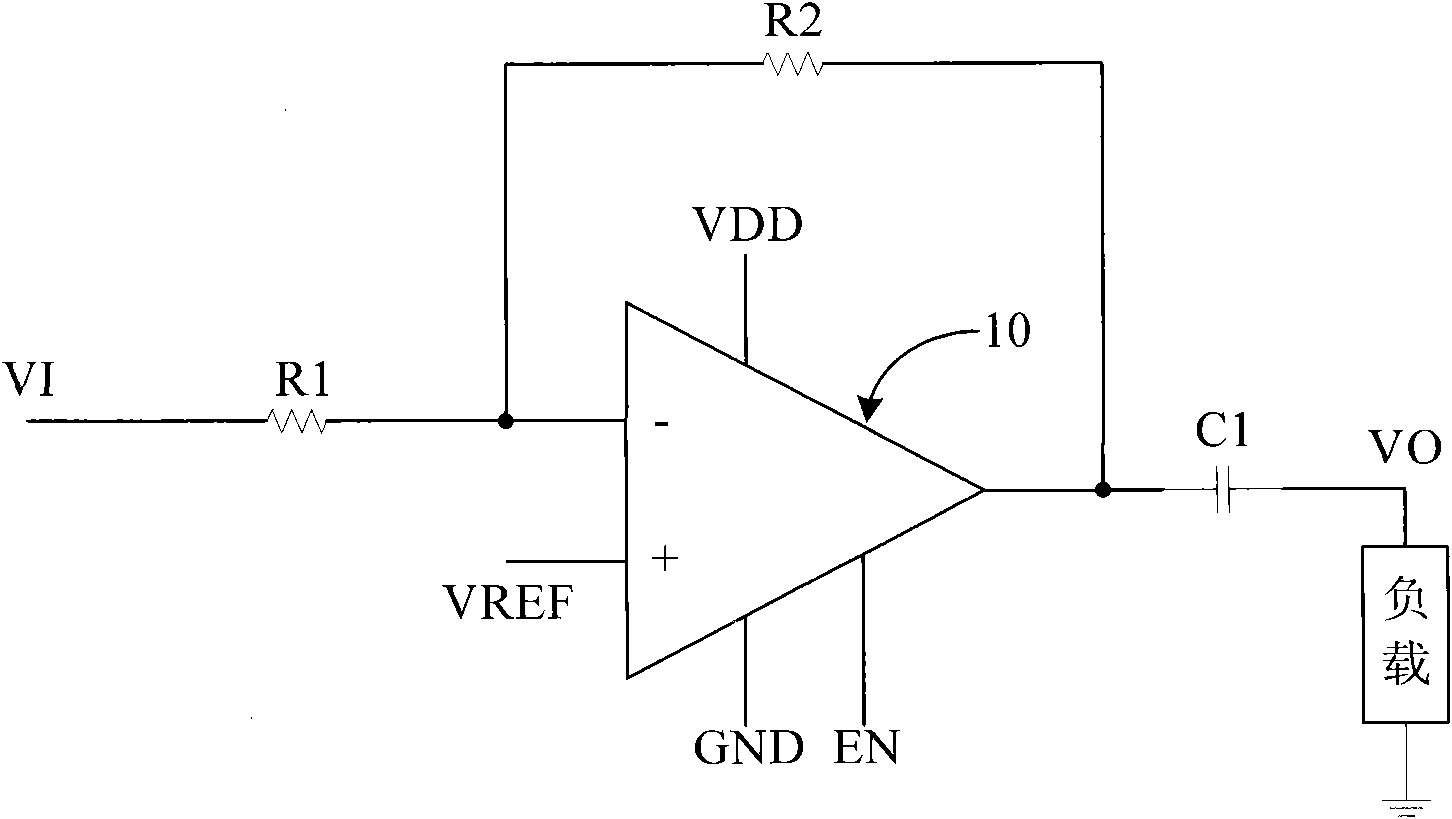

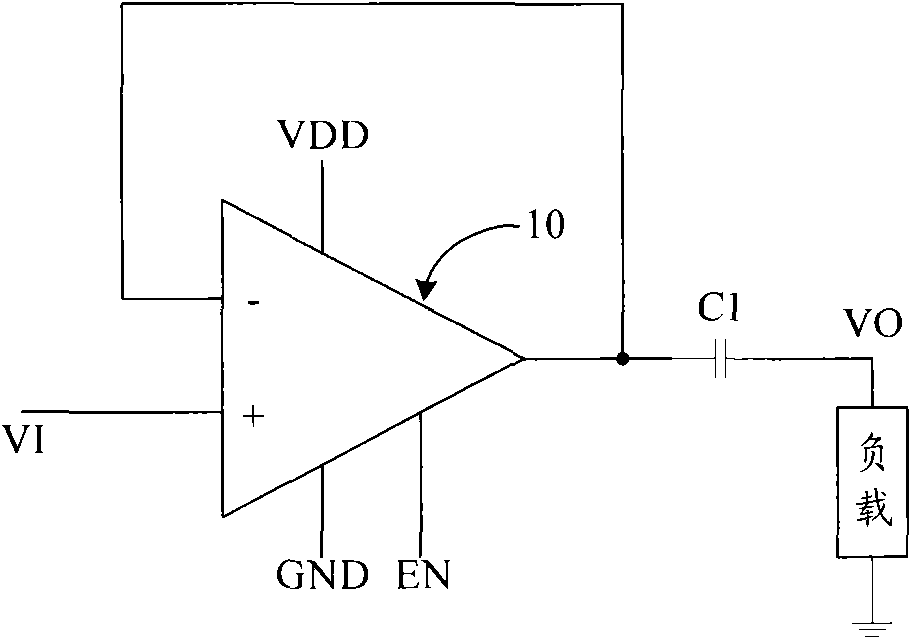

[0034] Figure 6The schematic diagram of the amplifier structure provided for this embodiment, as shown in the figure, the amplifier includes: an operational amplifier 10, a DC blocking capacitor C1, an input impedance circuit R1, a feedback impedance circuit R2, a ramp voltage generation circuit 72, and an enable signal delay control circuit 76 , Analog switch 74. Wherein, the signal output terminal OPO of the operational amplifier 10 is connected to one end of the DC blocking capacitor C1, the other end of the DC blocking capacitor C1 is connected to the input terminal of the load, and the feedback impedance circuit R2 is arranged between the negative signal input terminal of the operational amplifier 10 and the input terminal of the load. between the signal outputs.

[0035] Enable signal delay control circuit 76, its input end receives external enable signal, and the first output end is connected with the enable end of operational amplifier 10, is used for under the contr...

Embodiment 2

[0042] The structure of the amplifier of this embodiment is as Figure 6 As shown, the difference is that, specifically in this embodiment:

[0043] Enable signal delay control circuit 76 When the input external enable signal is effective, the first output terminal outputs an effective enable signal ENOP (see Figure 7 703 in ), to turn on the operational amplifier 10; after its first input end receives an effective external enable signal, its second output end delays the second time interval T2, and outputs an effective switch control signal MUTE (see Figure 7 702) to turn on the analog switch 74.

[0044] It can be seen that when the amplifier is turned on and the external enabling signal is valid, the enabling signal delay control circuit 76 outputs an effective enabling signal to the enabling terminal of the operational amplifier 10 to turn on the operational amplifier 10, and when the external enabling signal is valid , the slope voltage generating circuit 72 outputs a...

Embodiment 3

[0048] The structure of the amplifier of this embodiment is as Figure 6 As shown, the difference from Example 1 is, specifically in this example:

[0049] When the external enable signal is invalid, the second output end of the enable signal delay control circuit 76 outputs a switch control signal MUTE (see Figure 7 In 705), to disconnect the analog switch 74; the first output terminal of the enable signal delay control circuit 76 delays the fourth time interval T4 after the external enable signal fails, and prohibits the output enable signal (see Figure 7 In 706), to turn off the operational amplifier 10;.

[0050] The slope voltage generating circuit 72 outputs a second slope voltage signal (see Figure 7 704 ): the voltage starts to drop slowly from the reference voltage, reaches 0V after a predetermined third time interval T3, and then remains at 0V.

[0051] It can be seen that when the amplifier is turned off and the external enable signal is invalid, the second ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More