High-speed bidirectional clock tree circuit applied to ultrahigh-speed analog-to-digital converter

An analog-to-digital converter, ultra-high-speed technology, applied in the direction of analog-to-digital converter, logic circuit coupling/interface using field effect transistor, logic circuit connection/interface layout, etc., can solve the duty cycle mismatch, can not work, Inconsistent delay and other problems, to achieve the effect of resistance to process fluctuation errors, small footprint, and flexible layout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

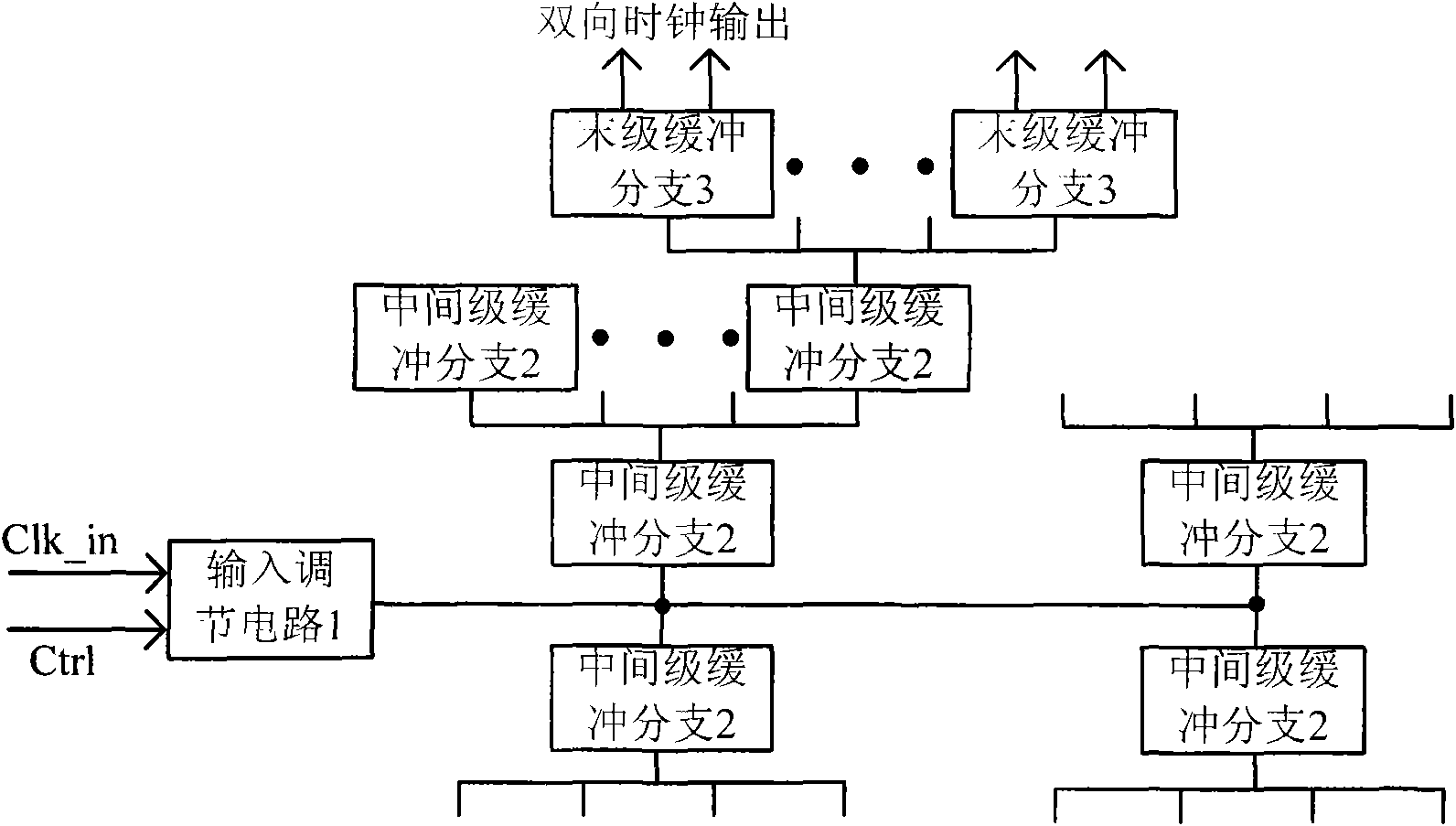

[0017] Such as figure 1 As shown, the input clock signal Clk_in and the control input terminal Ctrl are converted into a single clock output through the input adjustment circuit. Then use multi-level buffer branches to finally form all the clock output branches required. In the layout of the layout, use such as figure 1 The structure shown can not only ensure that the delay of each branch is the same, but also ensure that the input load and output load of each clock buffer branch are exactly the same.

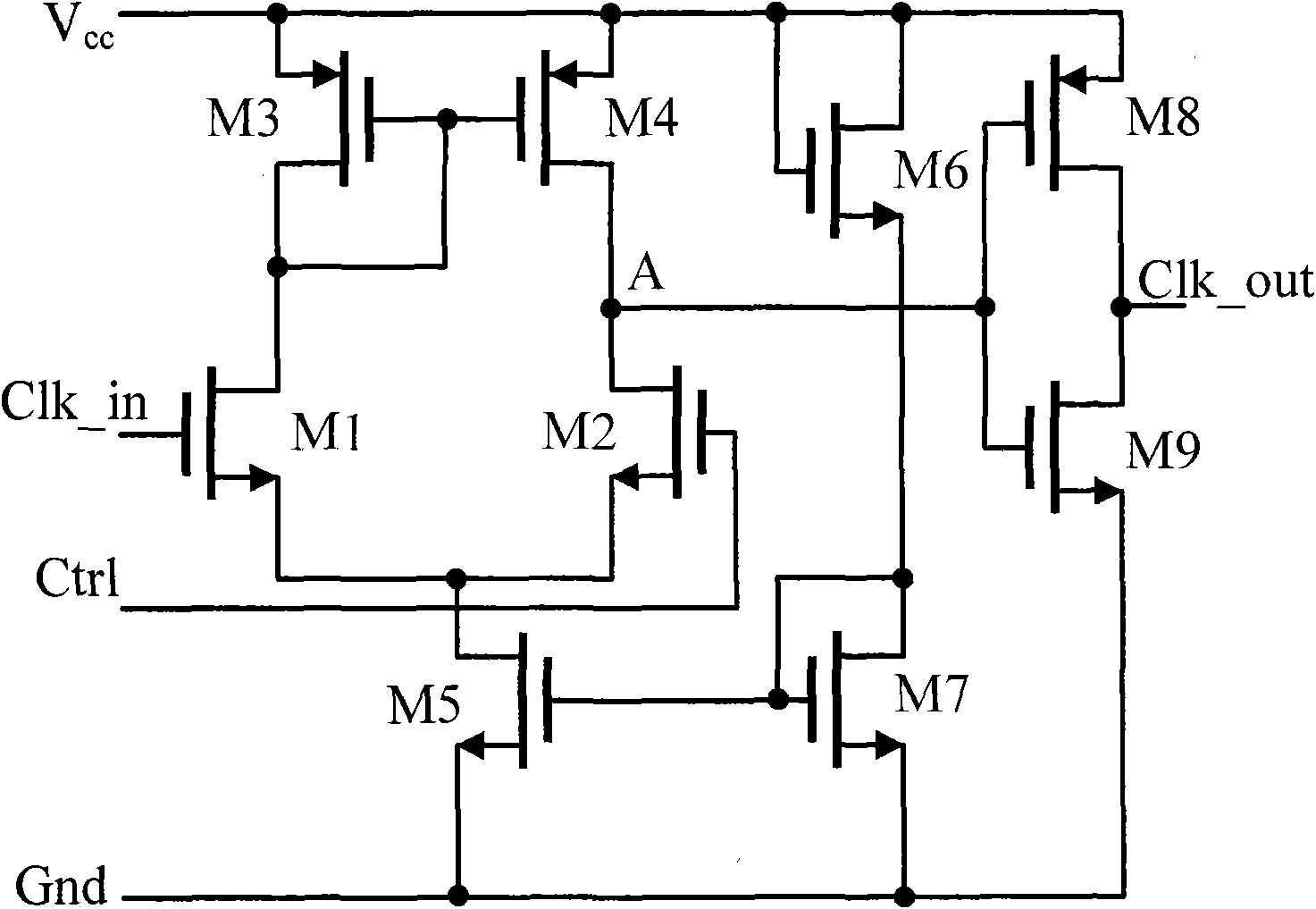

[0018] where the input conditioning circuit such as figure 2 As shown, N tubes M1 and M2 with the same aspect ratio are used to convert unbalanced input current, while P tubes M3 and M4 with the same aspect ratio form a pair of current mirrors. The N transistor M5 provides bias current for the differential input pair transistors M...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap