Cover layer of semiconductor device interconnected structure and manufacturing method thereof

A technology of interconnection structure and manufacturing method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., and can solve the problems of easy chip breakage, chip burnout, and loss of electrical connection of metal wires in interconnection structures, etc. problem, achieve the effect of ensuring work efficiency and stability, reducing RC delay, and reducing parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

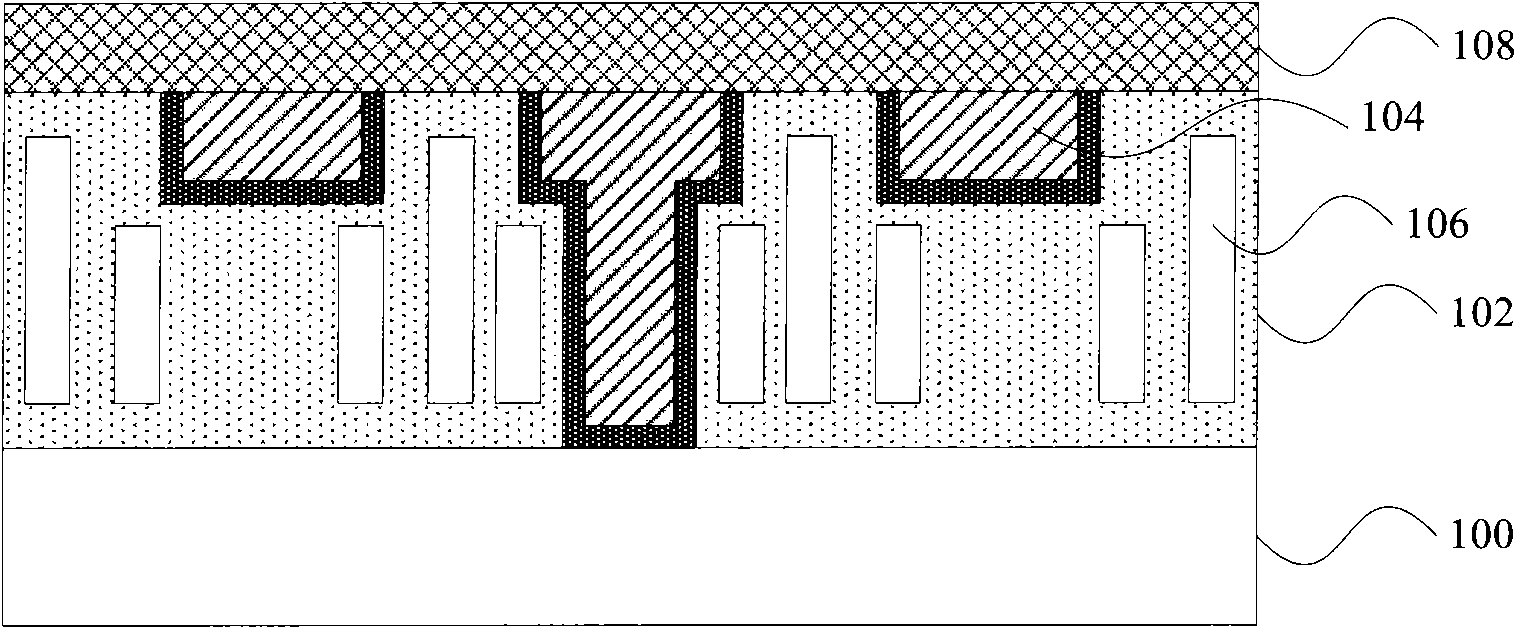

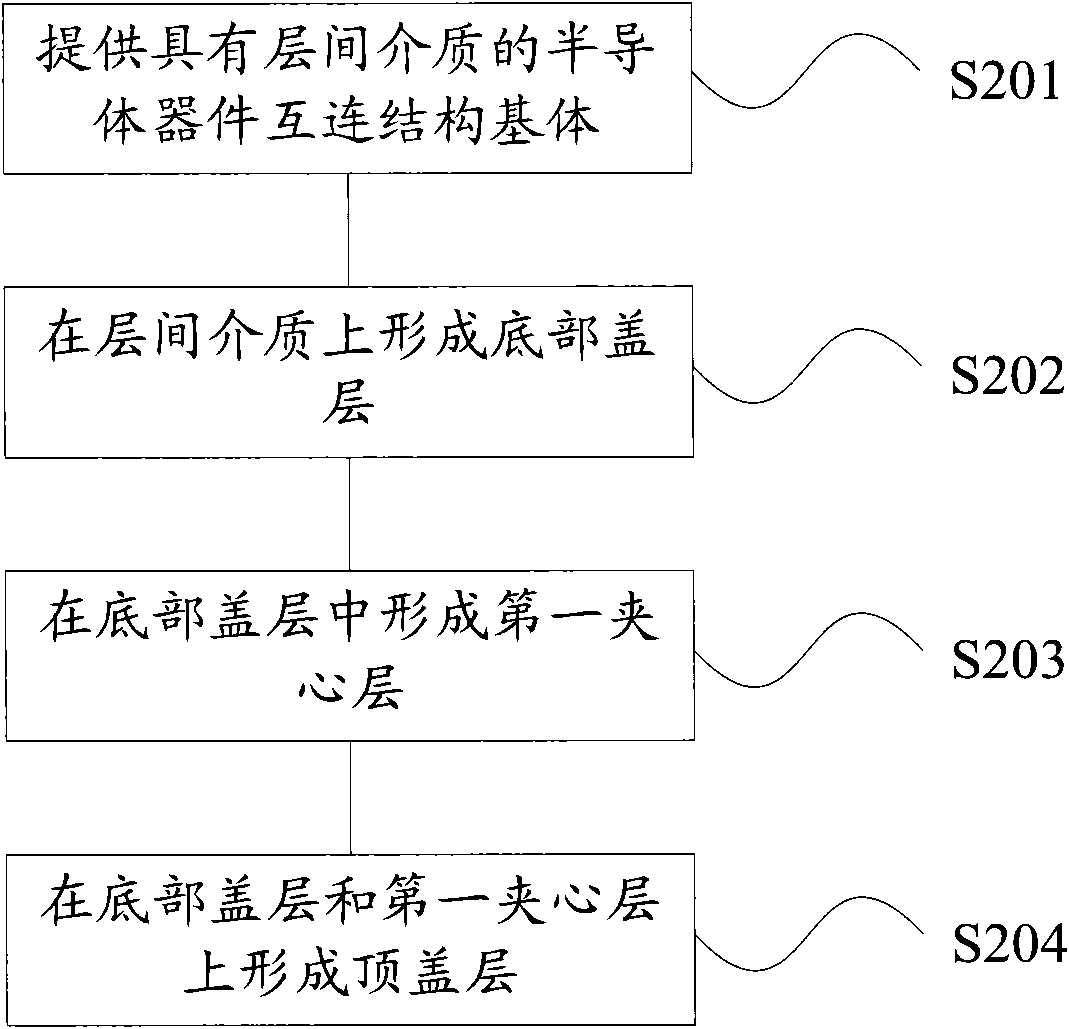

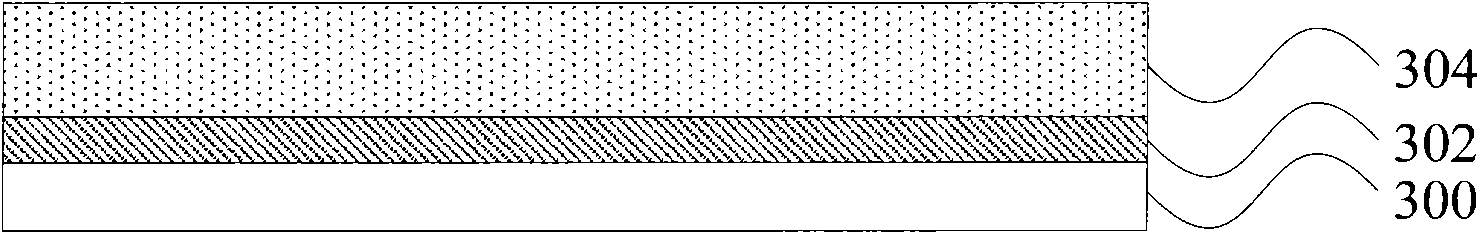

[0033] In the process of manufacturing the interconnection structure of semiconductor devices, the composite dielectric layer is used as a cover layer to protect the interlayer dielectric of each metal interconnection layer, so that the entire interconnection structure has higher mechanical strength and ensures that the chip is in use. Not easy to break. The composite dielectric layer enables the entire interconnection structure to use porous low-permittivity materials as the interlayer dielectric, and can also form air gaps in the interlayer dielectric without adversely affecting the mechanical strength of the interconnection structure, which can reduce the metal The parasitic capacitance between interconnect lines ultimately reduces the RC delay of IC signal transmission.

[0034] In addition, the metal material with high mechanical strength is used as the sandwich layer in the composite dielectric layer, which can further increase the mechanical strength of the interconnect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More