Dielectric layer structure for reducing stress and manufacturing method thereof

A manufacturing method and dielectric layer technology, which can be used in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., and can solve problems such as grain bending

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

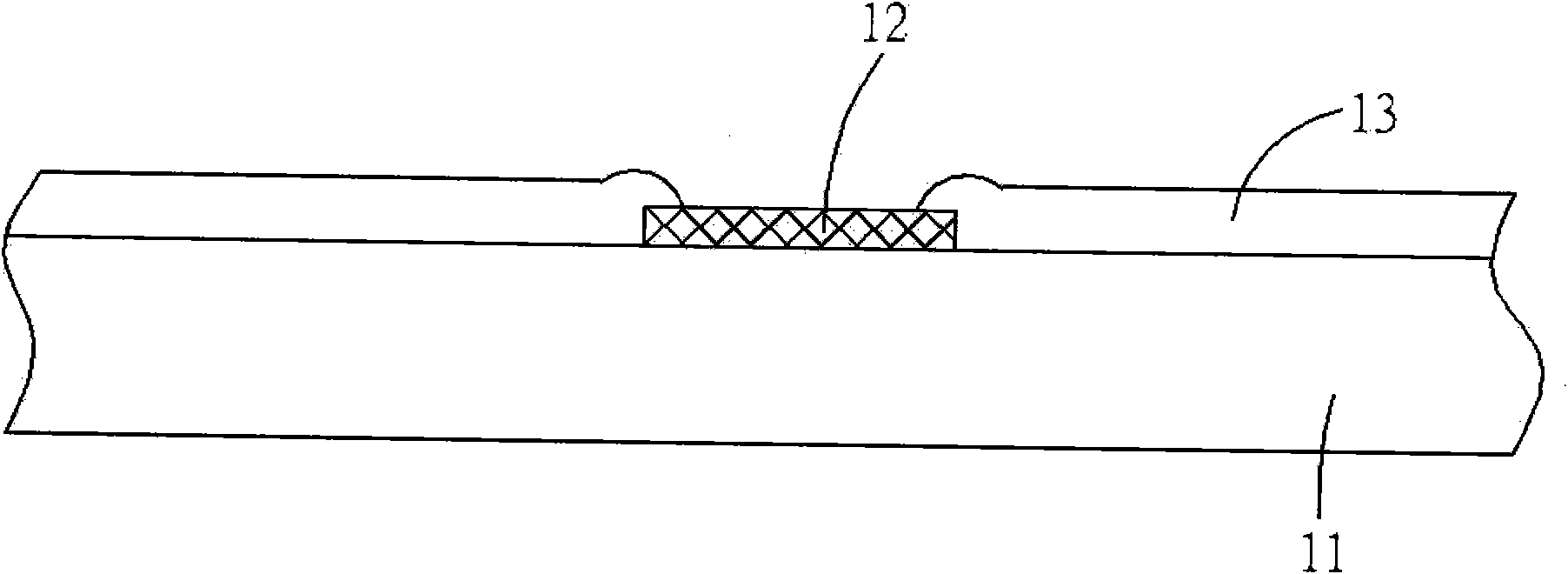

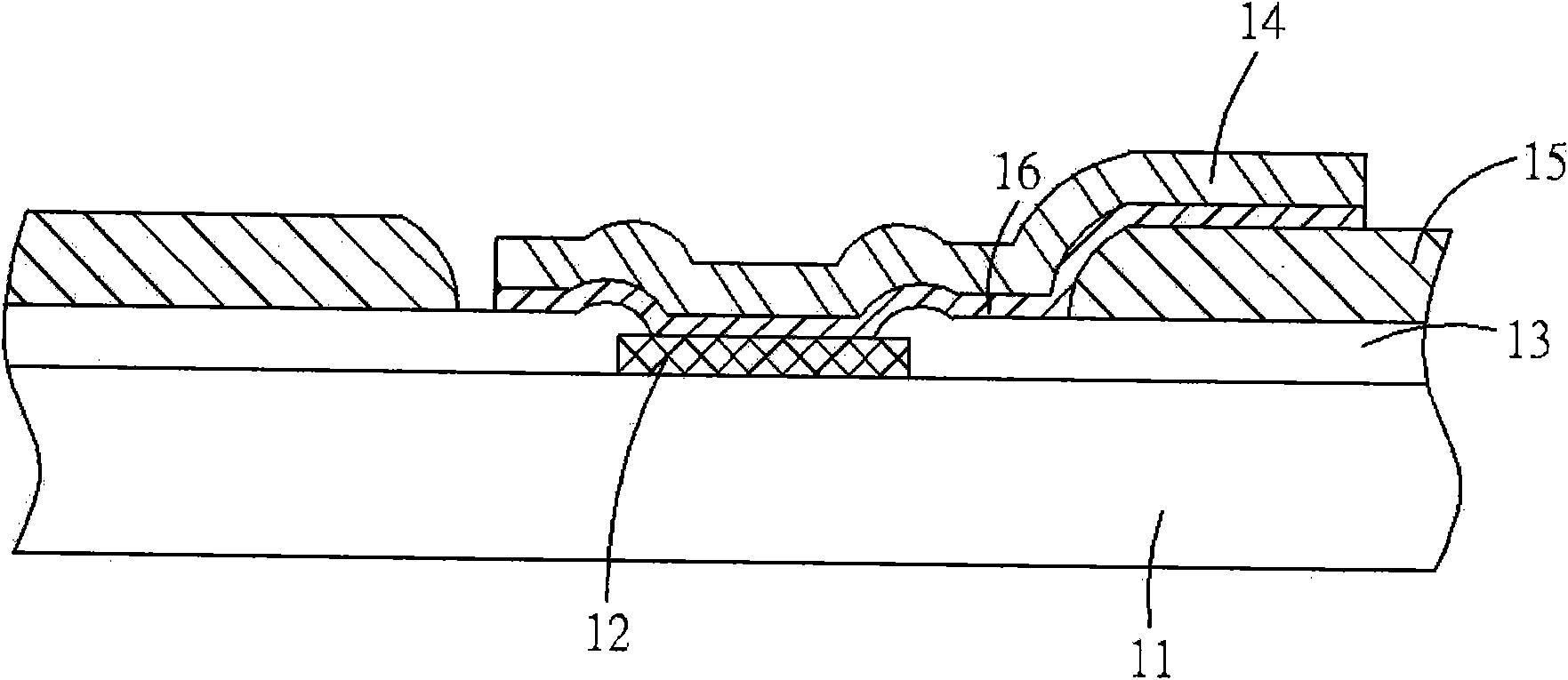

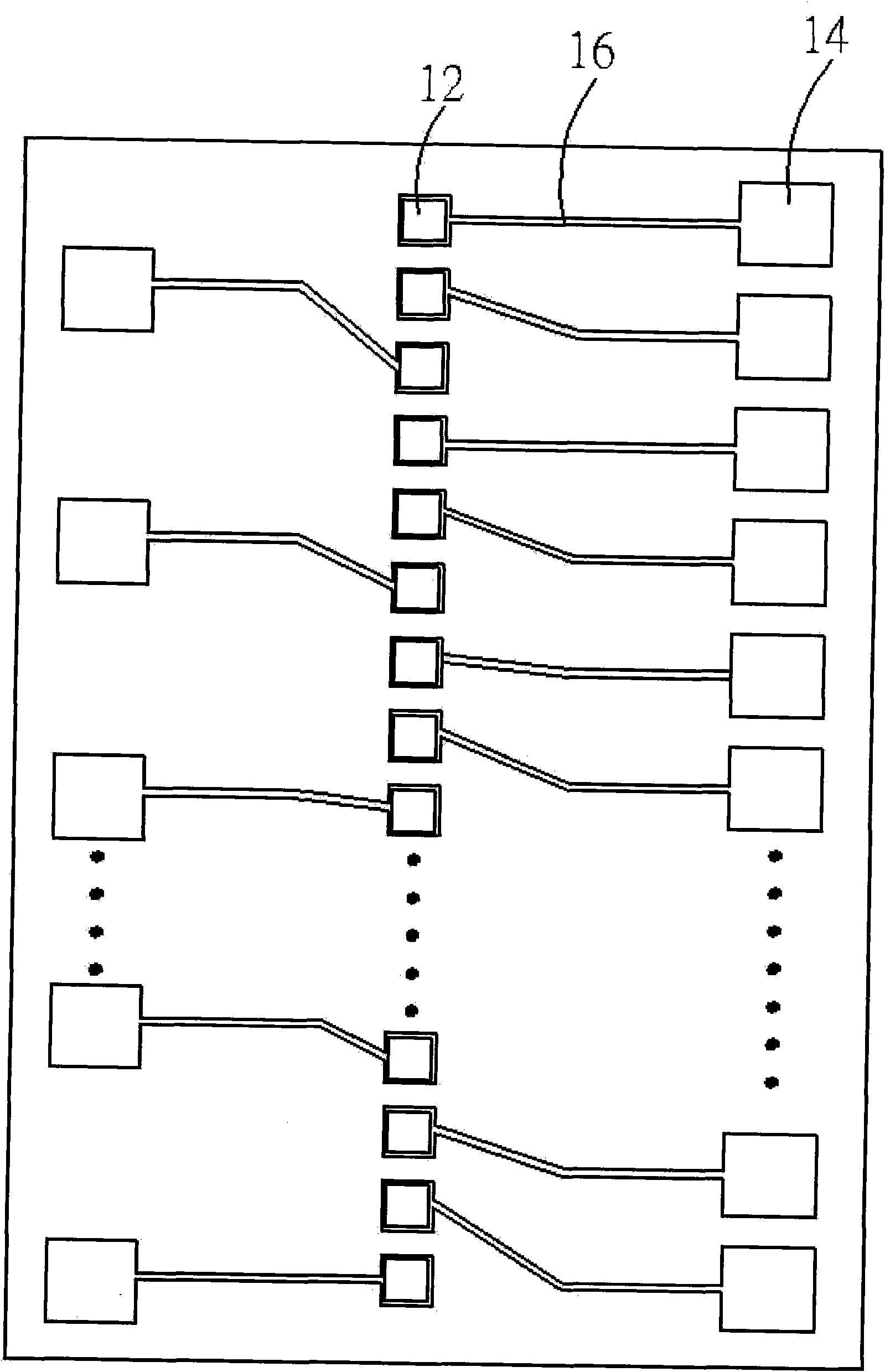

[0034] The features of the present invention can be clearly understood by referring to the drawings and the detailed description of the embodiments.

[0035] The stress-reducing dielectric layer structure and its manufacturing method of the present invention, the structure of the integrated circuit assembly 21 is as follows Figure 4 As shown, the integrated circuit component 21 is provided with a welding pad 22, a protective layer 23 and a first dielectric layer 24, the protective layer 23 covers the surface of the integrated circuit component 21, and the first dielectric layer 24 covers the protective layer. layer 23 surface, the protective layer 23 is provided with a first window 231 to expose the pad 22, and the first dielectric layer 24 is also provided with a second window 241 to expose the pad 22, the first and second windows 231 , 241 overlap up and down, and the size of the windows may be the same or different. In the embodiment shown in the figure, the opening ratio ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com