Dual-channel electrostatic discharge protecting circuit based on RC-triggering

An electrostatic discharge protection, dual-channel technology, used in emergency protection circuit devices, emergency protection circuit devices, circuits, etc. for limiting overcurrent/overvoltage, which can solve the problem of full-chip electrostatic discharge protection design, discharge The degradation of the electrostatic protection ability of the device and the complex physical process of the device can achieve the effect of improving the forward discharge performance, solving the degradation of the electrostatic protection ability, and improving the opening speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

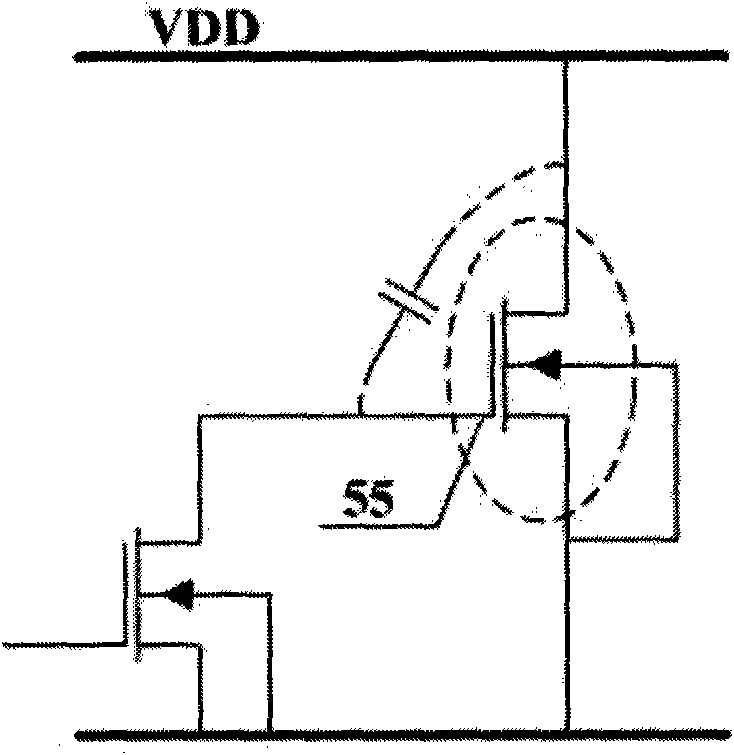

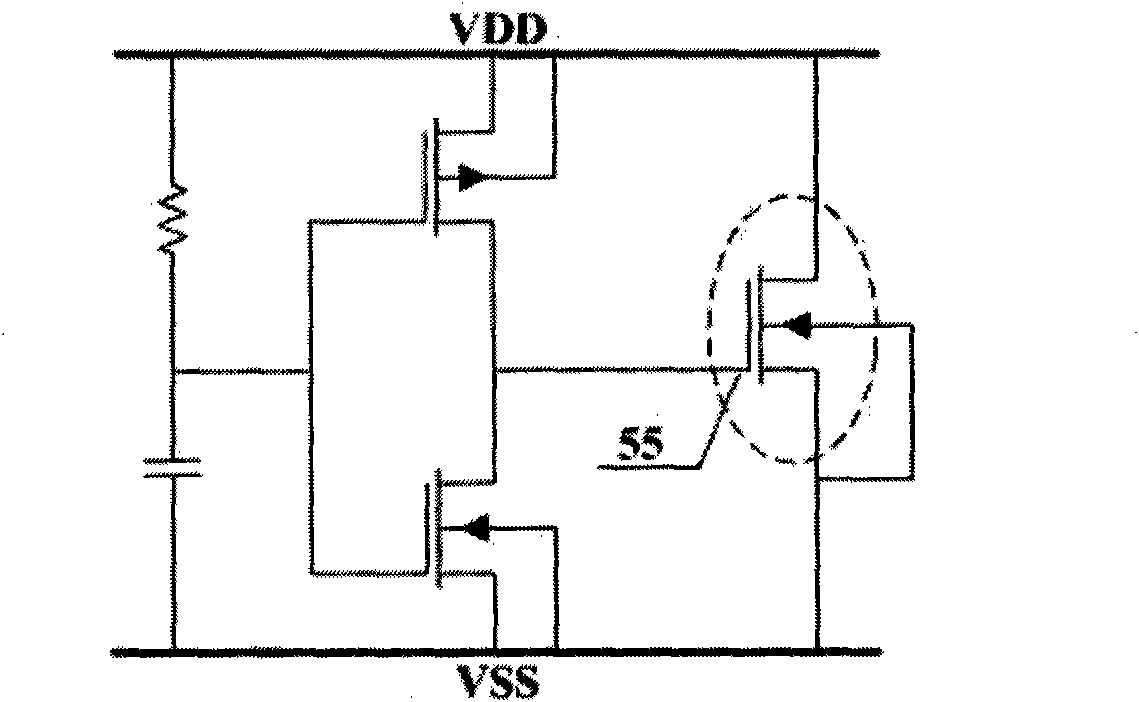

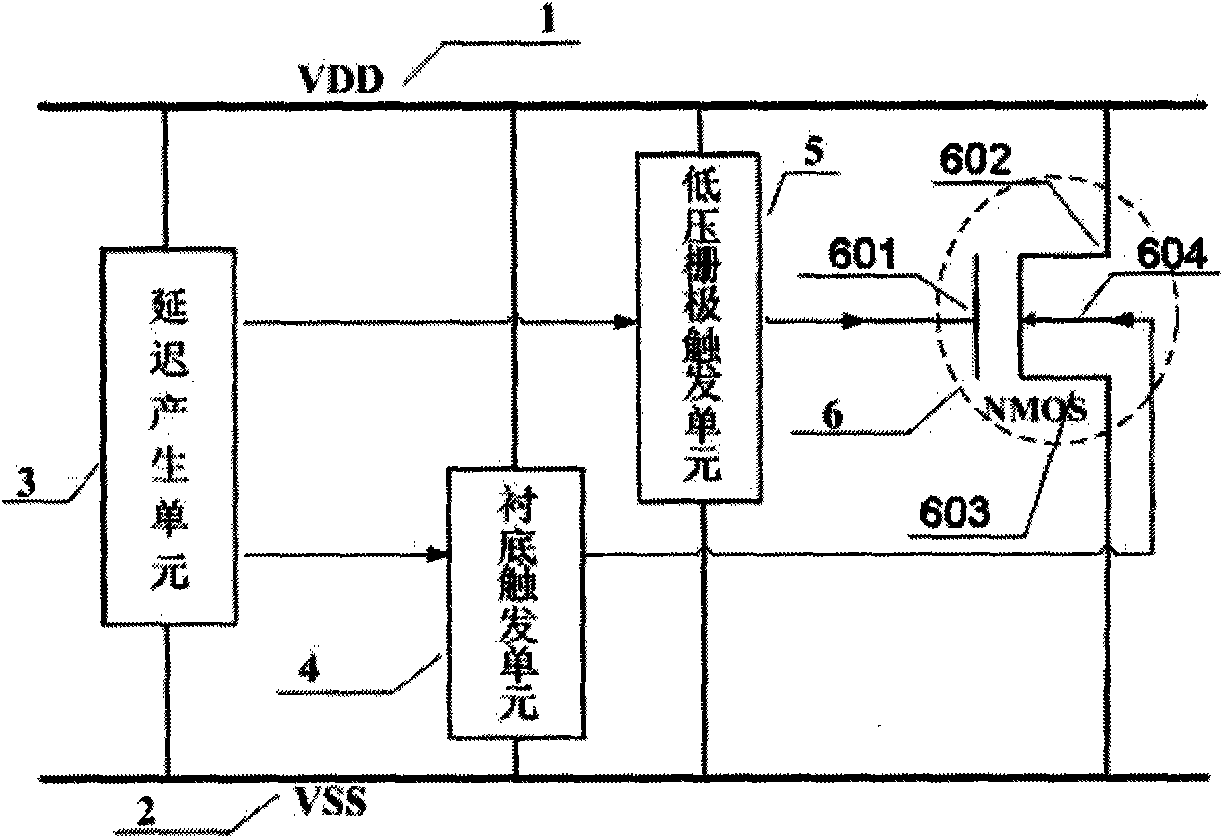

[0023] Such as image 3 As shown, the present invention is composed of a delay generation unit 3, a substrate trigger unit 4, a low-voltage gate trigger unit 5 and an electrostatic discharge device 6, and the electrostatic discharge device adopts an NMOS device. The delay generation unit 3 , the substrate trigger unit 4 , the low-voltage gate trigger unit 5 and the electrostatic discharge device 6 are connected in parallel and connected between the power supply 1 and the ground 2 . Because both the substrate trigger unit 4 and the low-voltage gate trigger unit 5 need to be driven by a certain delay pulse, and the delay time of these two driving pulses corresponds to the discharge time of the ESD process, so the substrate trigger unit 4 and the low-voltage gate trigger unit The unit 5 can use the same time delay, so in the present invention, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More