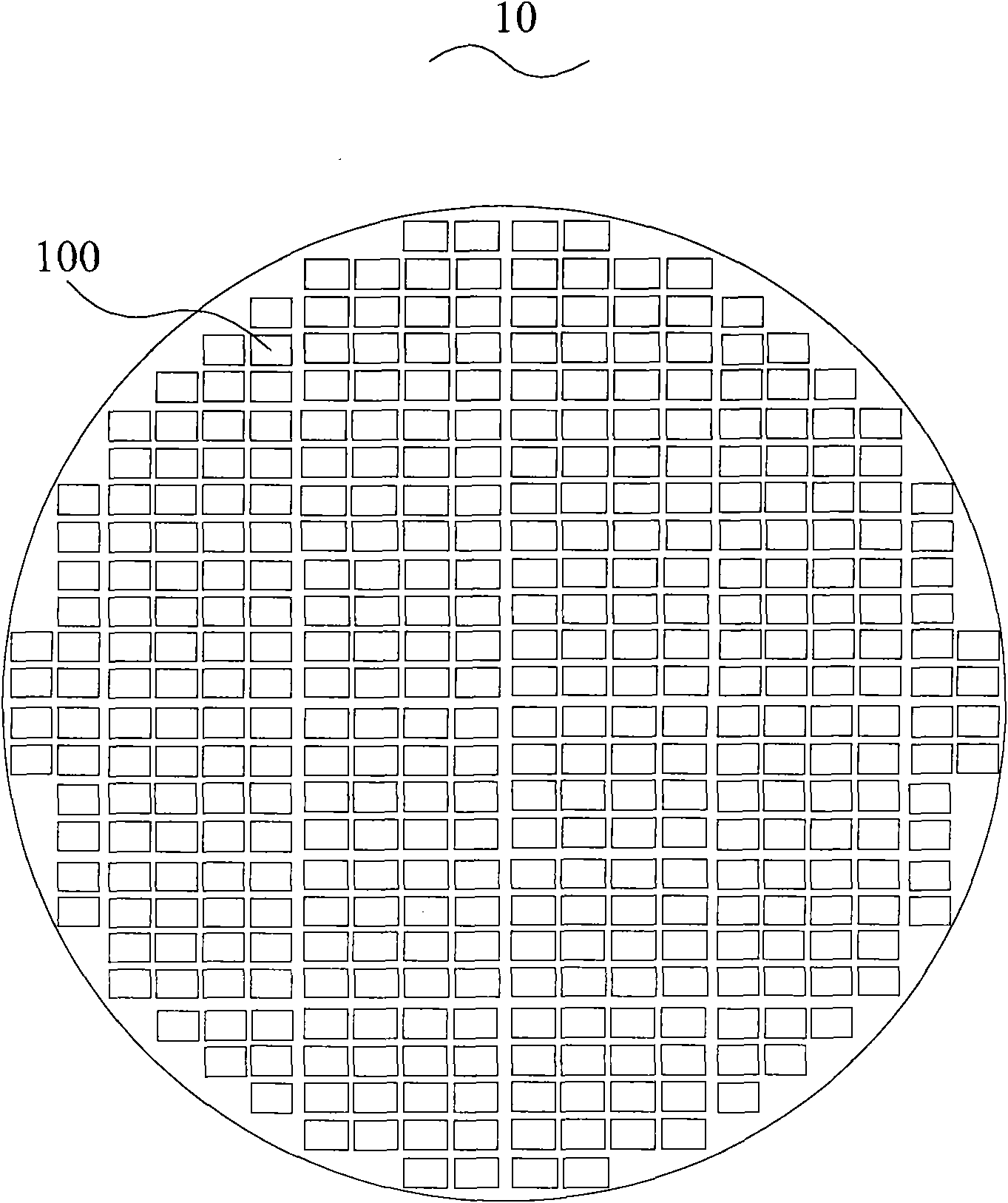

Under bump metal layer, wafer level chip scale package structure and forming method thereof

A metal layer under bump, wafer-level chip technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc. Electrical properties and reliability, improved adhesion, good wetting effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

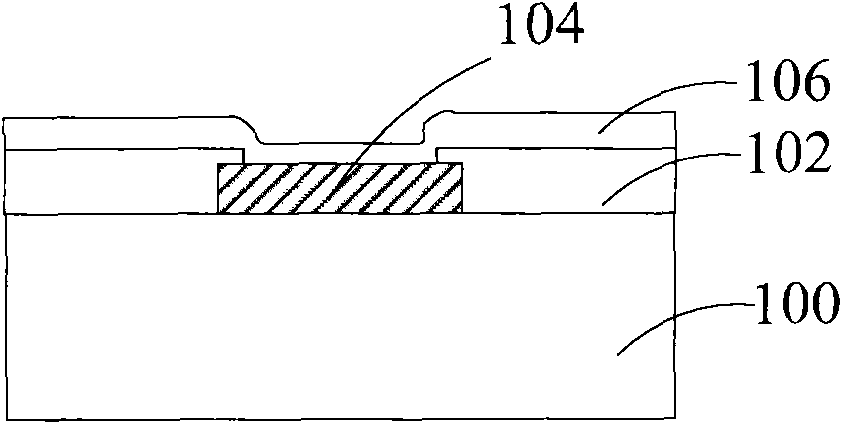

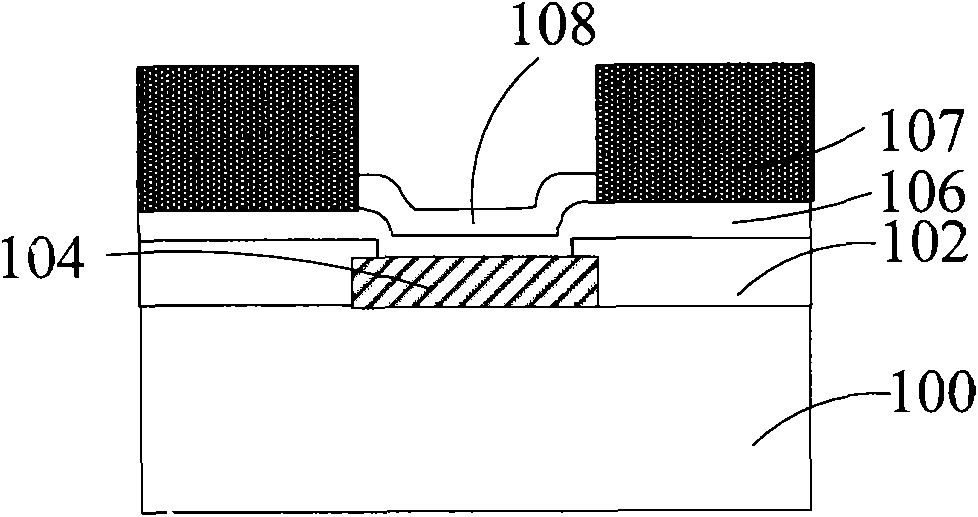

[0033] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0034] Figure 6 It is a flowchart of a specific embodiment of forming an under-bump metal layer in the present invention. Executing step S201, forming a metal pad layer and a passivation layer for protecting the surface of the chip and exposing the metal pad layer on the chip; executing step S202, forming a first metal layer and a photolithography layer on the passivation layer and the metal pad layer After the adhesive layer, an opening is formed on the photoresist layer, and the opening exposes the first metal layer on the metal pad layer; step S203 is performed, and in the opening, a second metal layer is sequentially formed on the first metal layer, and the first metal layer is sequentially formed on the first metal layer. The second metal layer includes a solder layer and a conductive layer under the solder layer; perform step S204,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More