MOS (Metal Oxide Semiconductor) transistor and forming method thereof

A technology of MOS transistors and semiconductors, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem that the channel length does not achieve the expected effect, reduce the reliability of semiconductor devices, and improve hot carrier instability. problem, to achieve the effect of reducing short channel effect, reducing hot carrier effect, and improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

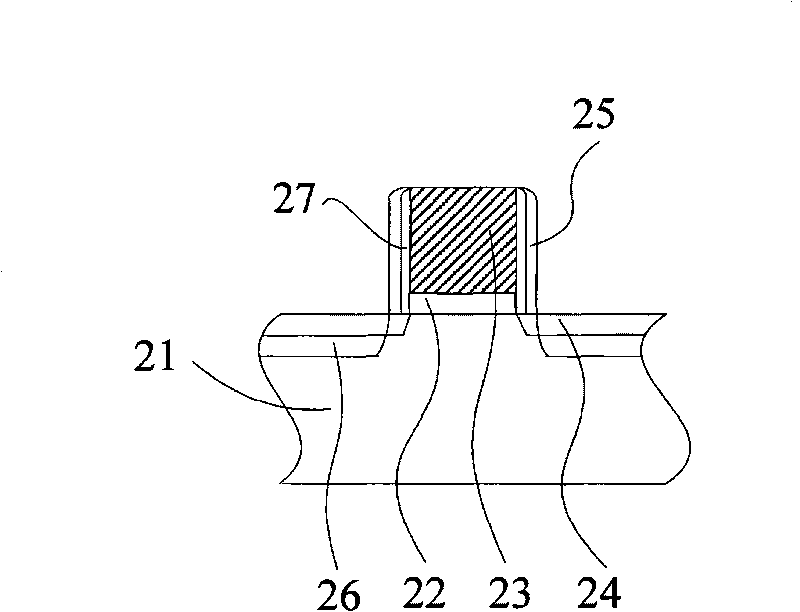

[0021] When the width of the offset sidewall of the invention is 8 nanometers to 9 nanometers, the length of the short channel is increased, and the short channel effect is reduced; at the same time, the stability of the hot carrier is improved, and the hot carrier effect is reduced. Improve the reliability and life of semiconductor devices.

[0022] Figure 4 It is a flow chart of a specific implementation manner of forming a MOS transistor according to the present invention. like Figure 4 As shown, step S1 is performed, a gate dielectric layer and a gate are sequentially formed on the semiconductor substrate, and the gate dielectric layer and the gate form a gate structure; and step S2 is performed to form offset spacers on both sides of the gate structure , the width of the offset sidewall is 8 nanometers to 9 nanometers; step S3 is performed, source / drain extension regions are formed in the semiconductor substrate on both sides of the gate structure and the offset sidew...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More