Groove type high-power MOS device and manufacturing method thereof

A MOS device and high-power technology, applied in the field of trench type high-power MOS devices and their manufacturing, can solve the effect of limiting the withstand voltage and the reliability of the withstand voltage, limit the withstand voltage effect of the MOS device, and reduce the on-resistance of the device. and other problems, to achieve the effect of reducing the characteristic on-resistance, enhancing the reliability of the withstand voltage, and improving the withstand voltage capability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with specific drawings and embodiments.

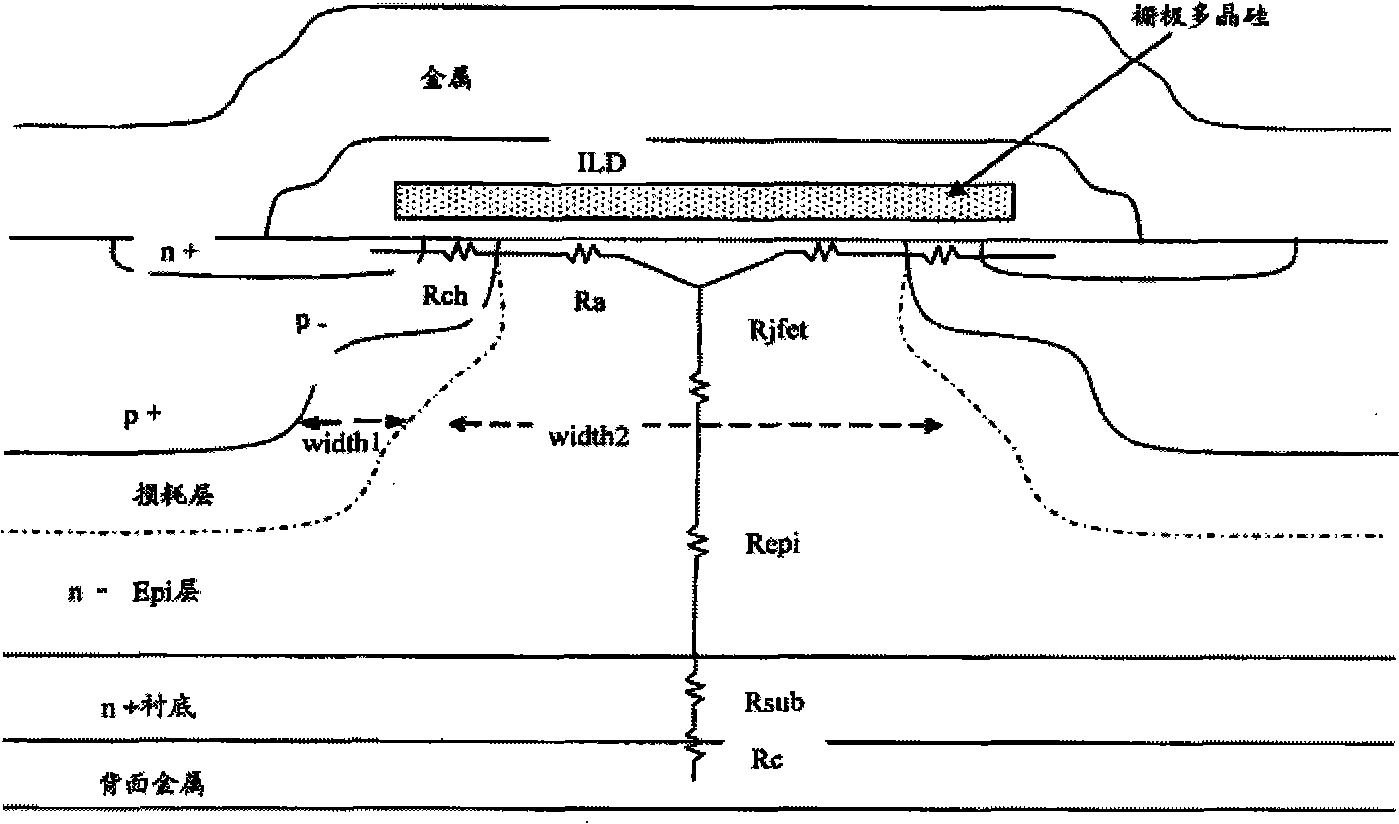

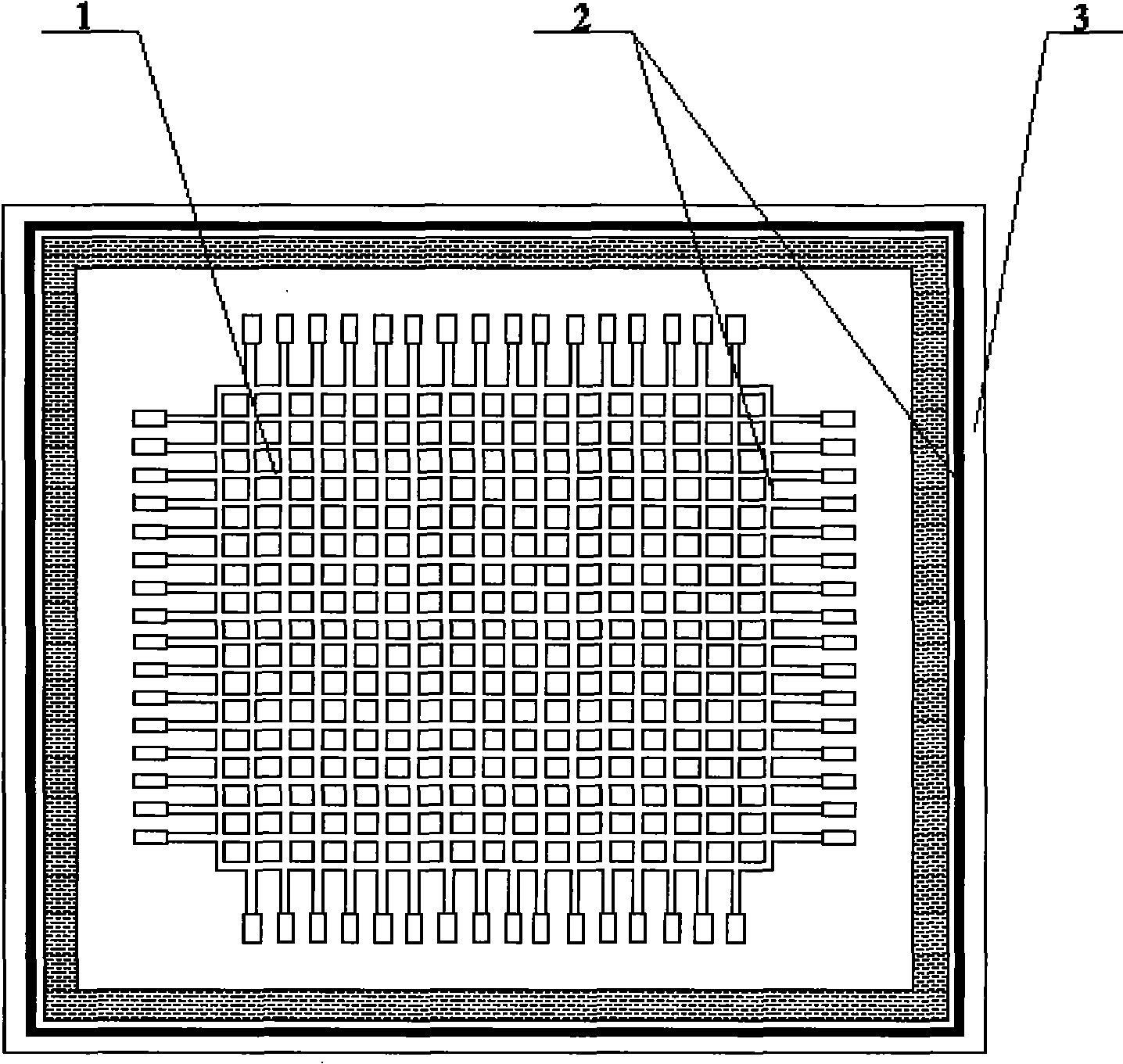

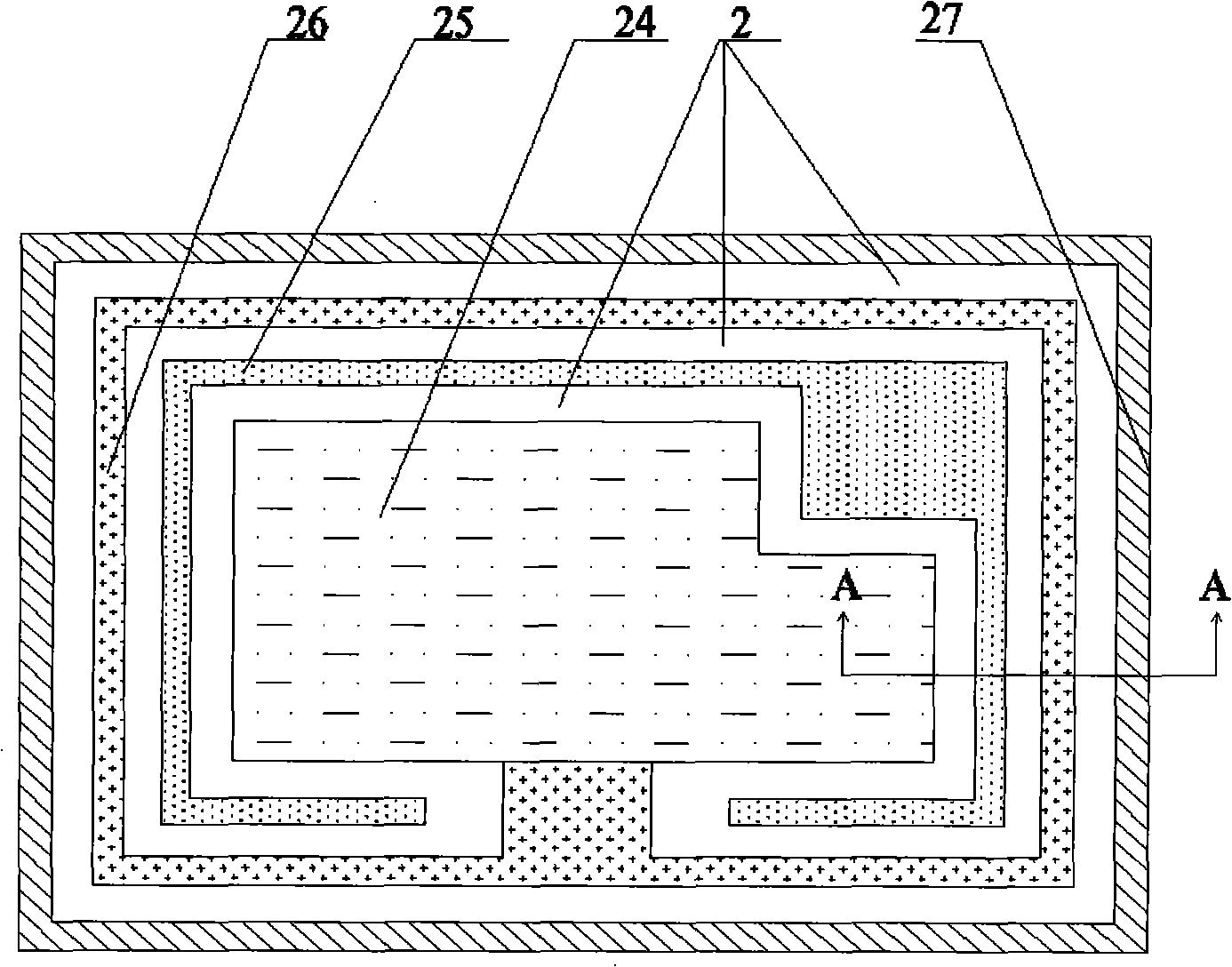

[0039] Such as Figure 2-9 As shown: taking an N-type MOS device as an example, the present invention includes a cell area 1, a voltage dividing protection area 2, a cut-off protection area 3, a photoresist 4, a P well layer 5 in the voltage dividing area, a field oxide layer 6, and a gate terminal 7. N+ substrate 8, N-type epitaxial layer 9, N+ implantation region 10, insulating gate oxide layer 11, conductive polysilicon 12, gate terminal trench 13, cell trench 14, stop trench 15, contact hole filling Metal 16, insulating dielectric layer 17, first ohmic contact hole 18, second ohmic contact hole 19, third ohmic contact hole 20, fourth ohmic contact hole 21, fifth ohmic contact hole 22, cut-off protection region P well layer 23 , a source metal 24 , a gate metal 25 , a third metal 26 , a fourth metal 27 and a P-well layer 28 in the cell region.

[0040] f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More