Digital signal processor with reconfigurable low power consumption data interleaving network

A technology of interleaving networks and digital signals, applied in the field of digital signal processors and microprocessors, can solve the problems of system stability decline, power consumption increase, consumption, etc., achieve high data throughput rate, fast speed, and overcome technical limitations Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

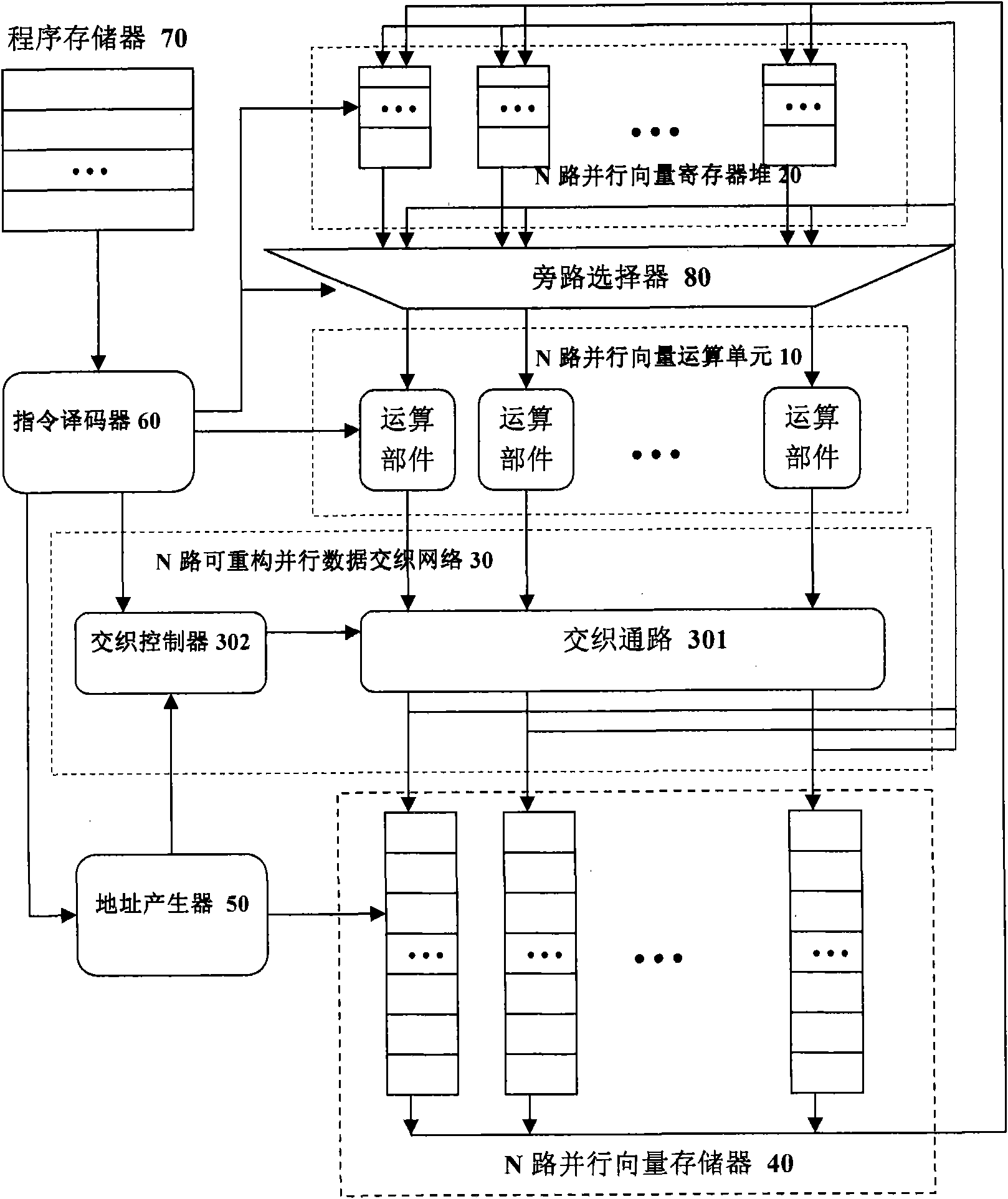

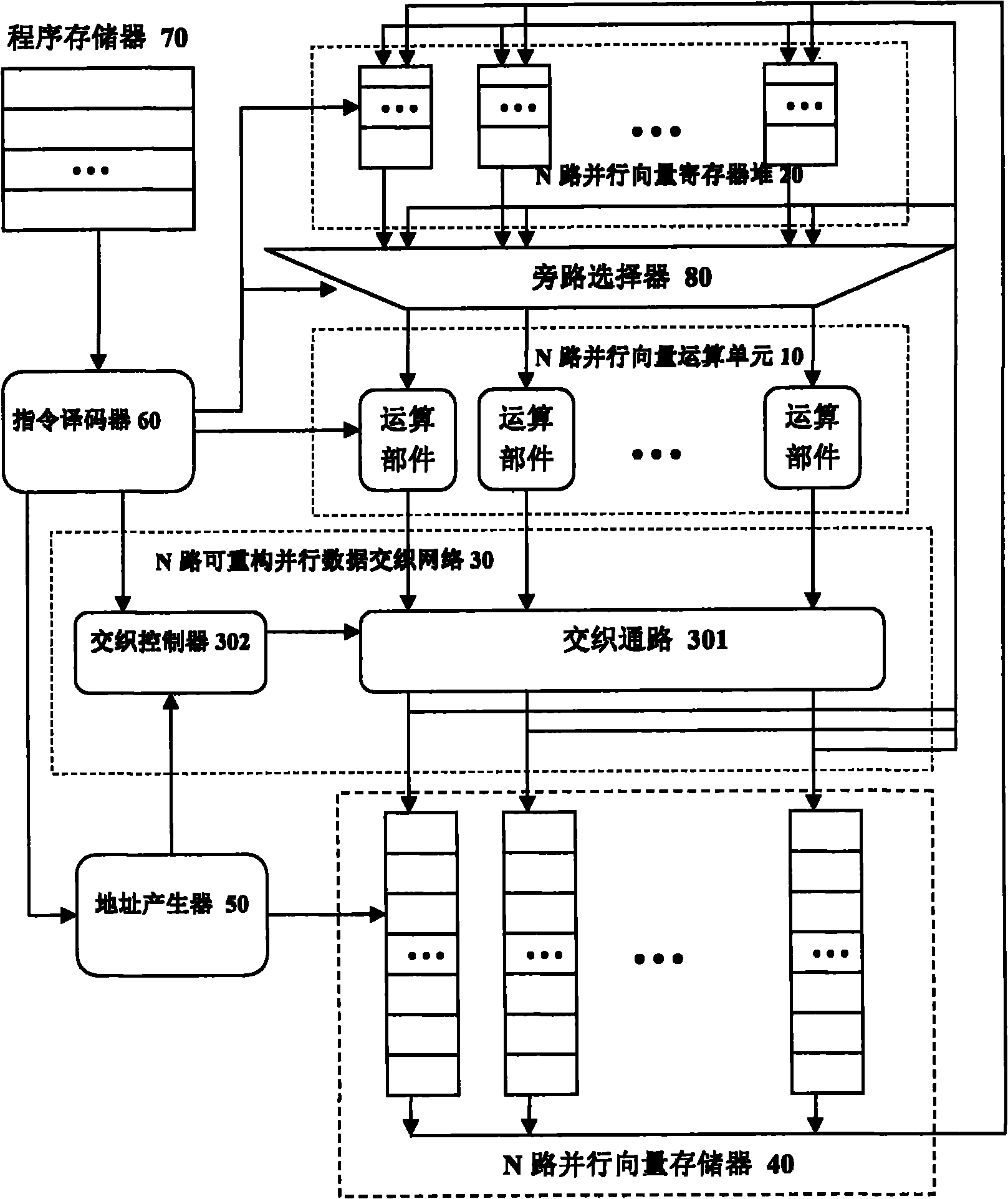

[0035] see figure 1 , figure 1 It is a structural schematic diagram of a digital signal processor with a reconfigurable low-power data interleaving network provided by the present invention. The digital signal processor includes an N-way parallel vector operation unit 10, an N-way parallel vector register file 20, and an N-way parallel vector register file 20. One way parallel vector memory 40 and one N way reconfigurable parallel data interleaving network 30.

[0036] Wherein, the N-way parallel vector operation unit 10 is used to perform calculation processing on the data input by the N-way parallel vector register file 20 , generate an operation result, and output the operation result to the N-way parallel vector regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More