Power metal oxide semiconductor field effect transistor (MOSFET) device with tungsten spacing layer in contact hole and preparation method thereof

A manufacturing method and contact hole technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as poor step coverage, aluminum puncture, small contact hole size, etc., to avoid leakage short circuit, ensure The effect of product quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

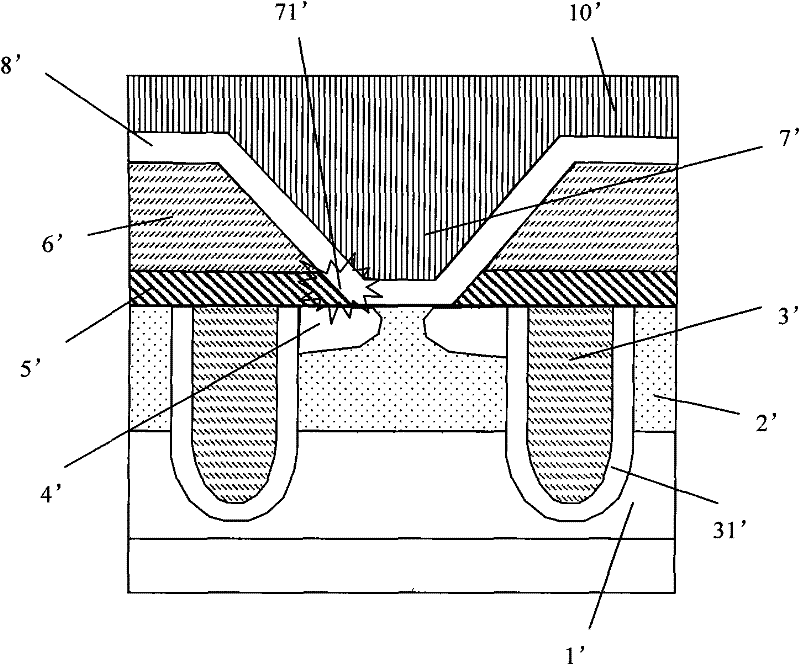

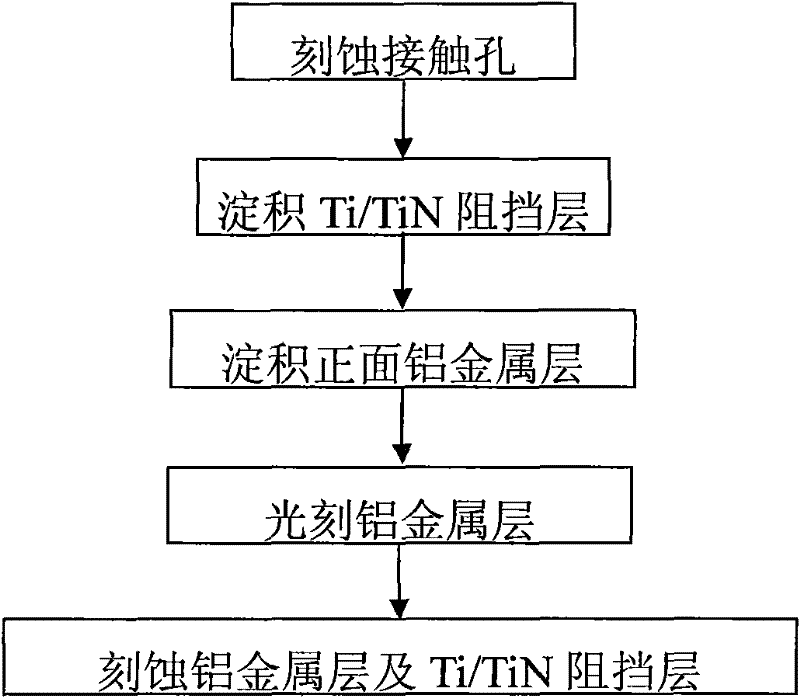

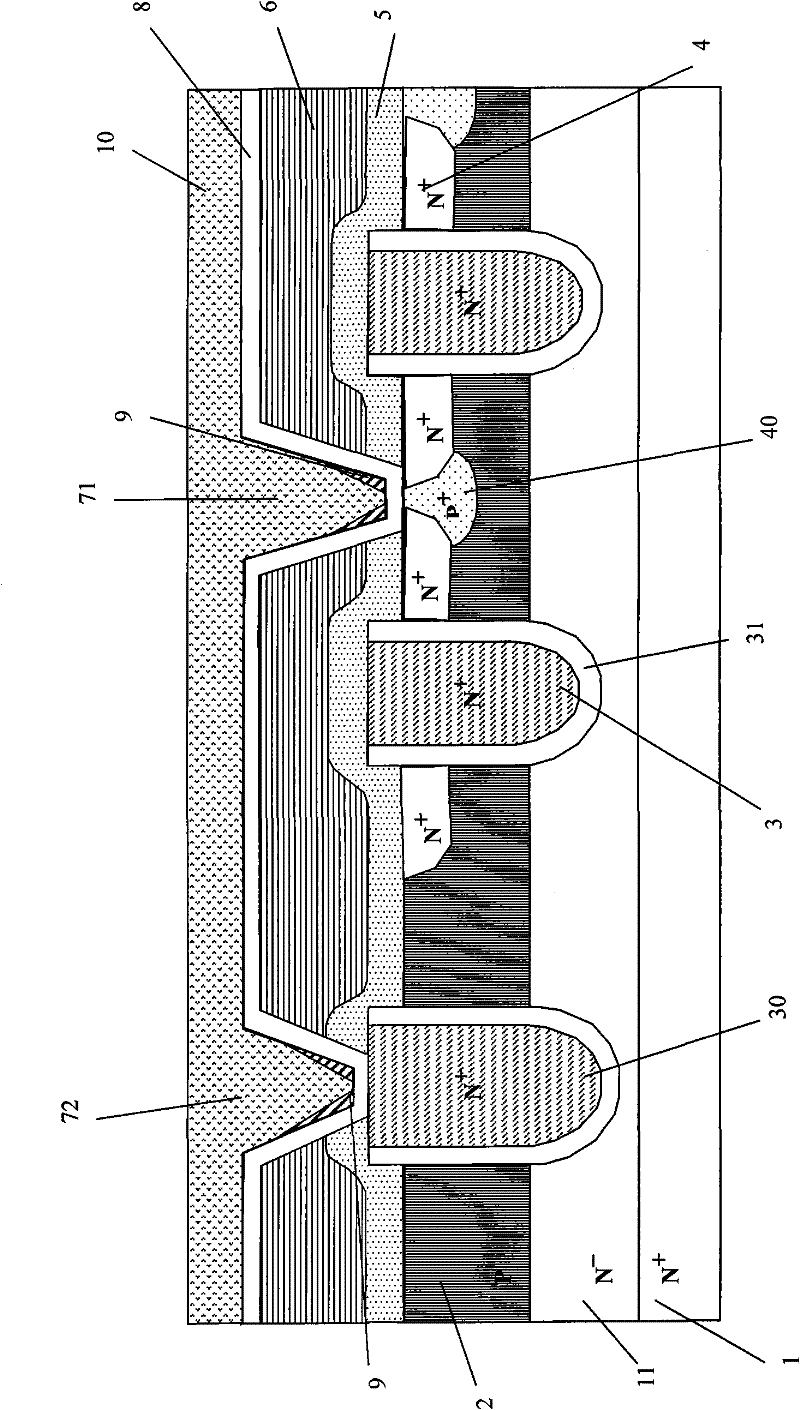

[0062] The following combination image 3 , Figure 4 , Figure 5 and Figures 6A-6E , the specific implementation of the present invention will be described in detail through several examples.

[0063] Such as image 3 Shown is a cross-sectional view of an embodiment of the power MOSFET device with tungsten sidewalls in the contact hole according to the present invention. The power MOSFET device is an N channel semiconductor device, which includes an N+ highly doped bottom substrate 1 as a drain, and an N- epitaxial layer 11 is grown on the N+ bottom substrate 1; on the N- epitaxial layer 11 A P-body region 2 is formed thereon. In the P-body region 2, there are several grooves penetrating the P-body region 2 and extending to a certain depth in the N-epitaxial layer 11, and filling the grooves with conductive material such as polysilicon to form the grooves Gate 3, and a thinner gate insulating layer 31 formed along the sidewall and bottom of the trench is also arranged ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More