Method for constructing floating gate

A floating gate and structure technology, applied in the field of semiconductor integrated circuit manufacturing, can solve problems affecting device performance, silicon substrate damage, transistor leakage, etc., and achieve the effect of reducing production costs and simplifying the process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

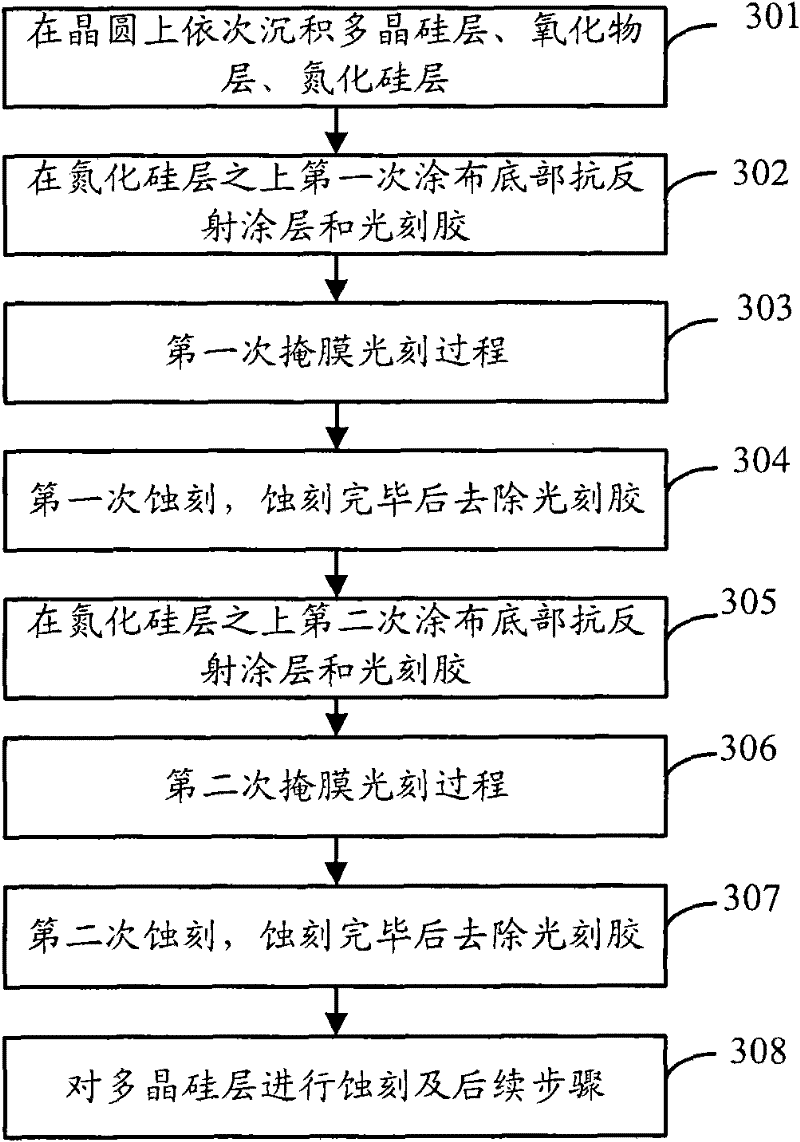

[0028] Aiming at the problems existing in the prior art, the present invention improves the construction process of FG, only coats photoresist and anti-reflection layer once, still adopts two photomasks, exposes twice in succession, and then develops once, but only uses One etching process can avoid the problem that the polysilicon layer is consumed in advance due to excessive consumption of silicon nitride in some areas.

[0029] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further elaborated below in conjunction with the accompanying drawings.

[0030] The process of constructing the floating gate proposed by the embodiment of the present invention is as follows Figure 4 shown, including the following steps:

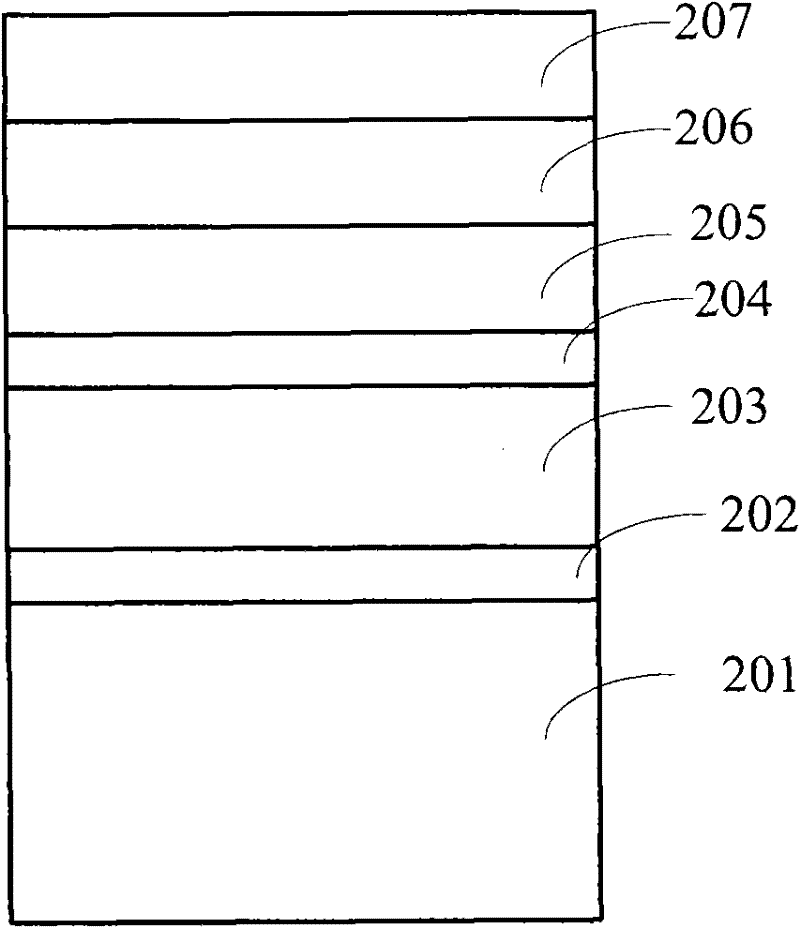

[0031] Step 401: sequentially depositing a gate oxide layer, a polysilicon layer, an oxide layer and a silicon nitride layer on the upper surface of the wafer.

[0032] Step 402: coat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com